一、冯·诺伊曼结构

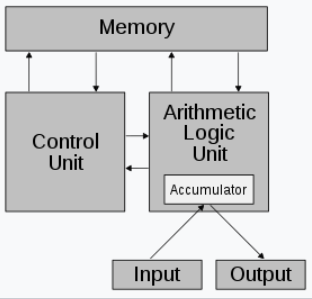

冯·诺伊曼结构(英语:Von Neumann architecture),也称冯·诺伊曼模型(Von Neumann model)或普林斯顿结(Princeton architecture),是一种将程序指令存储器和数据存储器合并在一起的电脑设计概念结构。

冯●诺依曼结构的计算机其程序和数据共用一个存储空间,程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置;采用单一的地址及数据总线,程序指令和数据的宽度相同。处理器执行指令时,先从储存器中取出指令解码,再取操作数执行运算,即使单条指令也要耗费几个甚至几十个期,在高速运算时,在传输通道上会出现瓶颈效应。

冯●诺依曼结构的计算机由CPU和存储器构成,程序计数器(PC)是CPU内部指示指令和数据的存储位置的寄存器。CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到所需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。在这种体系结构中,程序计数器只负责提供程序执行所需要的指令或数据,而不决定程序流程。要控制程序流程,则必须修改指令。

冯·诺伊曼结构这个词出自约翰·冯·诺伊曼的论文:First Draft of a Report on the EDVAC , 于1945年6月30日。冯·诺依曼由于在曼哈顿工程中需要大量的运算,从而使用了当时最先进的两台计算机Mark I和ENIAC,在使用Mark I和ENIAC的过程中,他意识到了存储程序的重要性,从而提出了存储程序逻辑架构。

二、哈佛架构

哈佛架构(英语:Harvard architecture)是一种将程序指令储存和数据储存分开的存储器结构(Split Cache)。这一词起源于Harvard Mark I型继电器式计算机,它存储指令(24位)在纸带上和数据于机电计数器上。

中央处理器首先到程序指令储存器中读取程序指令内容,解码后得到数据地址,再到相应的数据储存器中读取数据,并进行下一步的操作(通常是执行)。程序指令储存和数据储存分开,数据和指令的储存可以同时进行,可以使指令和数据有不同的数据宽度,如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。程序需要由操作者加载;处理器无法自行初始化。

在哈佛架构,两个寄存器不需要有共同的特征。特别是,字宽、定时、实现技术和内存地址都可以不同。在一些系统中,指令可以存储在只读存储器(ROM)中,而数据存储器一般需要读写存储器(RAM等)。在一些系统中,指令存储器比数据存储器多,因此指令地址比数据地址更宽

三、哈佛架构冯诺依曼架构的对比

纯冯诺依曼架构下的CPU可以读取指令或读/写内存数据,它们都不能使指令和数据同时使用同一个的总线系统。使用哈佛结构的计算机中CPU,即使没有缓存的情况下也可以在读取指令的同时进行数据访问。由于指令和数据访问不使用同一个内存沟道,因此哈佛结构的计算机可以在相同的电路复杂度下有更好的表现。

同时,哈佛架构机拥有不同的代码和数据的地址空间:指令的零地址和数据的零地址是不同的。指令的零地址可能是二十四位的值,而数据的零地址可能是一个八位字节,而非二十四位值的一部分。

四、哈佛架构与改进的哈佛架构的对比

改进的哈佛架构机更像哈佛架构机,但它放松了指令和数据之间严格分离的这一特征,仍然允许CPU同时访问两个(或更多)内存总线。最常见的修改包括由公共地址空间支持的单独指令和数据高速缓存。当它作为一个纯粹的哈佛机时,CPU通过高速缓存来执行指令。当访问外部存储器时,它的作用就像一个冯·诺依曼机(代码可以像数据一样移动,像是一个功能强大的技能)。这一改良在现代处理器是普遍存在的,例如ARM体系结构、Power Architecture和x86处理器。它有时被称为哈佛架构,忽略了它实际上被“修改”的事实。

另一种修改提供了指令存储器(例如ROM或闪存)与CPU之间的通路,以允许来自指令存储器的字被视为只读数据。该技术用于某些微控制器,包括Atmel的AVR。这允许访问诸如文本字符串或函数表之类的常量数据,而无需首先将其复制到数据存储器中,从而为读/写变量保留稀缺(且耗电的)数据存储器。特殊的机器语言指令提供了从指令存储器中读取数据的功能。(这是不同于指令本身嵌入常数的数据,虽然对于单个常量来说,两种机制可以相互替代。)

五、后续

冯诺依曼的瓶颈:将CPU与存储器分开并非十全十美,反而会导致所谓的冯·诺伊曼瓶颈(von Neumann bottleneck):在CPU与存储器之间的流量(数据传输率)与存储器的容量相比起来相当小,在现代电脑中,流量与CPU的工作效率相比之下非常小,在某些情况下(当CPU需要在巨大的数据上运行一些简单指令时),数据流量就成了整体效率非常严重的限制。CPU将会在数据输入或输出存储器时闲置。由于CPU速度远大于存储器读写速率,因此瓶颈问题越来越严重。

哈佛架构的应用:纯粹的哈佛架构同时访问多个存储系统的主要优点是由哈佛处理器利用现代CPU缓存系统。相对纯的哈佛架构机主要用于在应用中的取舍,就像忽略缓存的成本和节省功率,大于编程在不同的代码和数据的地址空间的不利。

- 数字信号处理器(DSPs) 一般执行少,高度优化的音频或视频处理算法。他们避免缓存,因为他们的行为必须非常重现。应对多地址空间的困难,执行速度是次要的问题。因此,一些DSP功能在不同的地址空间的多个数据存储器便于SIMD和VLIW处理。德克萨斯仪器TMS320 C55x处理器,具有多个并行数据总线(双写,三读)和指令总线。

- 单片机的特点是具有少量的程序(闪存)、数据存储器(SRAM),没有缓存,并利用哈佛架构的并行高速处理指令和数据的访问。分开存储的程序和数据存储器可能具有不同的位宽,例如使用16位指令和8位宽的数据。这也意味着指令预取可以与其他活动同时进行。例子包括,Atmel的AVR和Microchip的 PIC。

即使在这种情况下,它是为了访问程序存储器只读表的数据使用特殊指令或重新编程;这些处理器是改进的哈佛架构的处理器。