1、冯诺依曼计算机问题:

a、指令执行时的串行性

b、存储空间访问的串行性(每次只能读取一个单元的数据)

基本原理“串行性”严重制约其性能(效率)提升空间

2、存储器问题:

a、高速度与易失、容量的矛盾

b、大容量与速度、成本的矛盾

c、非易失与速度、寿命的矛盾

没有一款性能完全满足显示计算机要求的存储器

3、今天所有计算机的模型,没有离开冯氏结构。

4、计算及结构分析举例:

a、地址缓存、数据缓冲、总线控制分别于地址总线、数据总线、控制总线相连接。

b、两种存储器,内存与外存,一种断电消失,一种不消失,以保证计算机永远有程序可以执行

c、一个计算机必须要的东西(定时器,存储器,控制器,总线等)会做在主板上。

d、每一个元件都有一个缓冲区,从逻辑上认为他是通的,为了让数据能够有序进行传输,类似于水龙头,防止速度不匹配。

5、任何一个计算机,都必须有:

a、并口(通用I/O口)

b、串口

c、定时器

d、中断

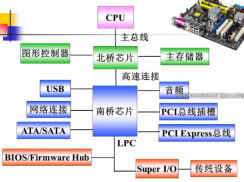

6、现代微型系统结构(三芯片)

a、增加了两个南北桥芯片,使得总线被分段,每一段的宽度不在一定,某些部分可以更宽更快,某些可以窄一点,这样既可以达到提高速度,又可以降低成本。每一段总线可以同时发送不同的数据,互不干扰,可以看做并行。

b、现在的结构是将北桥的大部分和CPU结合,而剩下的小部分和南桥结合,形成了2芯片结构。

c、主板结构:CPU+北桥+南桥

d、总线改进:总线分段,各段可独立并行,优化电气性能

e、北桥:连接高速部件:存储器、图形控制器;支持多种存储器、显示器

f、南桥:高集成度:集成通用计算机几乎全部常用外设,向前兼容

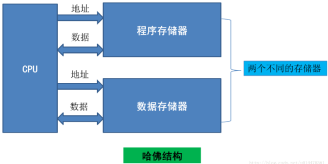

7、哈佛结构:

a、将存储器单独拿出来,单独用一条总线和CPU相连,即将取指令的运算和I/O的运算分开。

b、CPU有四条总线和外部相连,将程序指令存储和数据存储分开的存储结构,是一种并行体系结构,两个存储器独立编址,独立访问。

c、CPU执行指令的速度快过指令的存取速度,所以将指令的存储部分单独出来换成更高速的存储设备(比方说加宽了程序存储器的总线的宽度)。

d、允许在一个机器周期内同时获得指令字(来自程序存储器)和操作数(来自数据存储器),从而提高了执行速度和数据的吞吐率。

e、由于取指和执行存储在两个分开的物理空间,因此取指和执行能完全重叠。CPU首先到程序存储器中读取程序指令内容,解码后得到数据地址,再到响应的数据存储器中读取数据,并进行下一步的操作。

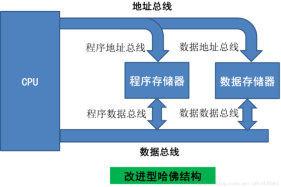

8、改进型哈佛结构:

a、也使用两个不同的存储器:程序存储器和数据存储器,但把两个存储器的地址总线合并了,数据总线也进行了合并,即原来的结构需要四条不同的总线,改进后需要两条。

b、使用两个独立的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存,以便实现并行处理

c、使用两个独立的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存,以便实现并行处理

d、两条总线由程序存储器和数据存储器分时共用

嵌入式(十六):冯诺依曼结构&哈佛结构

猜你喜欢

转载自blog.csdn.net/qq_40851744/article/details/106426464

今日推荐

周排行