相关文章

数字IC前端学习笔记:格雷码(含Verilog实现的二进制格雷码转换器)

单比特信号同步基础

当一个触发器的输入信号不满足建立时间(setup time)和保持时间(hold time)时,输出会处于亚稳态,即输出即不是1也不是0,处于一个不确定值,当亚稳态输出作为其他逻辑门的输入时,可能会导致亚稳态的连锁传递,因此必须使用一些方法组织触发器进入亚稳态。

在只有一个时钟的数字系统中(称为单时钟域数字系统),通过控制两个触发器之间的组合逻辑电路的延迟,可以确保建立时间和保持时间满足时序要求。但当一个时钟域触发器的输出作为另一个时钟域触发器的输入时,两个时钟没有任何关联,这时的亚稳态需要其他方法来避免。

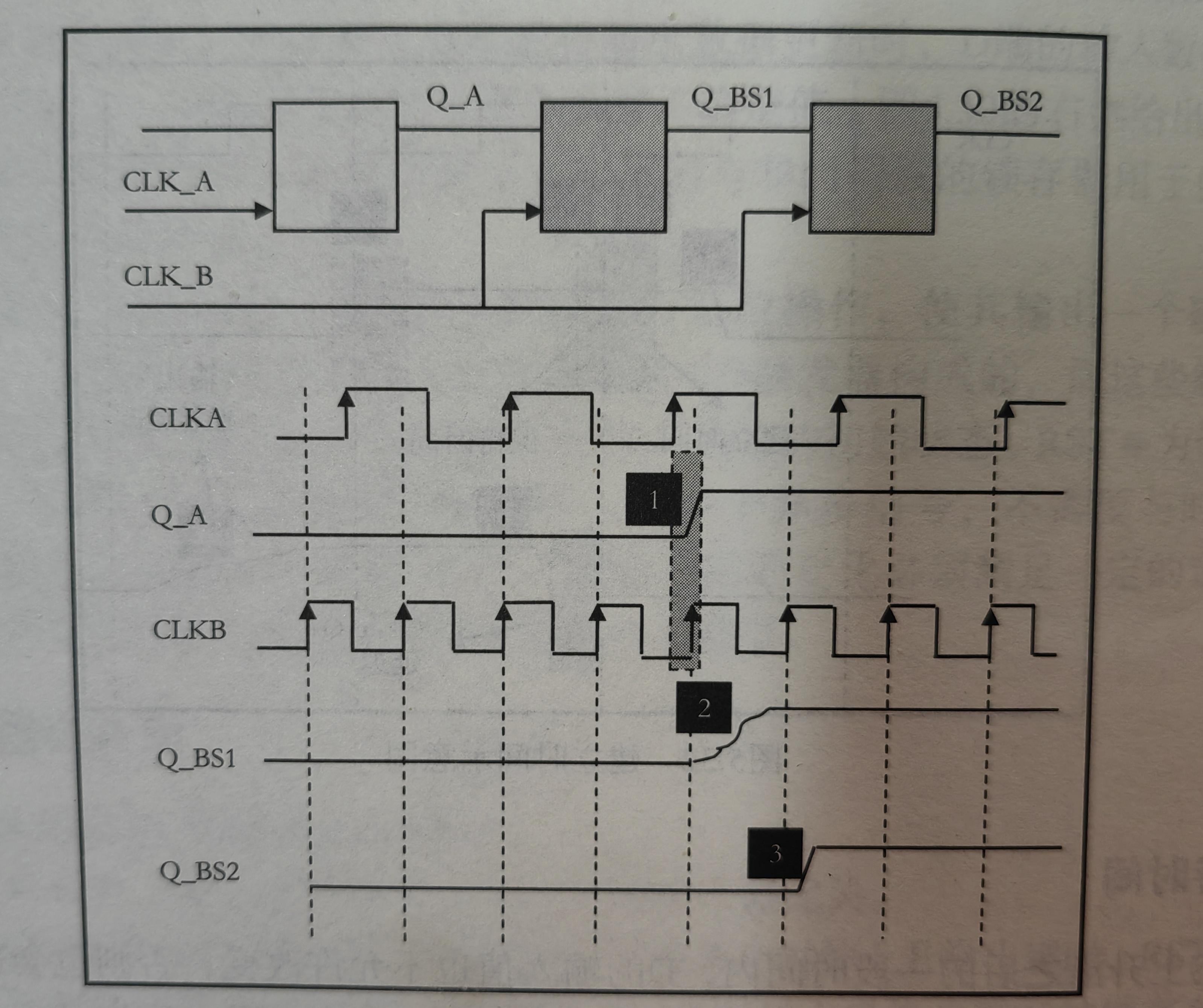

下图给出了解决这个问题的一种方法,即在CLK_B时钟域的输出最后插入两个级联的D触发器。此时,输出Q_BS1的输出可能会出现亚稳态,但当下个时钟沿来临前,亚稳态会稳定下来,这时Q_BS2就大概率不会出现亚稳态。但当CLK_B时钟很快时,Q_BS2依旧可能出现亚稳态,此时可以考虑增加级联的D触发器数量。实际应用中,多使用两级触发器打拍即可。

信号同步规则

当信号同步时,需要遵循以下几条规则。

跨时钟域的信号必须直接来自源时钟域的寄存器输出。如果信号来自组合逻辑,而不是直接来自触发器,可能会造成竞争与冒险,下图给出了一个例子。

在开始时,与门的两个输入是1和0,输出c为0,当a从0变1,同时b从1变0时,最终输出c仍然是0,但a和b可能在短暂的时间都处于1状态,造成了输出c在一段时间内错误的为1,如果恰好CLK_B上升沿出现在此时,那么毛刺信号1将传递到后级,使得d和e出现了一个有一定宽度的错误信号,这是我们不希望看到的。如果使用CLK_A时钟域的寄存器插入到与门后,那么c上的毛刺就不会出现,从而不影响电路正常工作。

使用逻辑单元库中的专用触发器实现同步器。这里说的专用触发器具有高驱动能力和高增益(

),这会使他们能更快进入稳定状态,所以使用他们能加快电路摆脱亚稳态的速度。

),这会使他们能更快进入稳定状态,所以使用他们能加快电路摆脱亚稳态的速度。

一个输出信号,避免使用多个同步装置进行同步。这句话的意思是,不能使用多个同步装置将一个信号同步到另一个时钟域的多个点,因为同步装置会导致信号延迟1到2个周期,如果有多个同步装置,那么结果可能会出现不一致(即使最终的结果是一致的),会导致下游系统出错。

多位输出信号,避免使用多个同步装置分别同步。我们这篇文章讨论的,都是单比特信号,多为控制信号,当有多比特信号需要同步时,我们不能使用本文的方法,原因同c,多位结果可能会出现不稳定的组合情况,可能会导致出错(这里也可以通过使用格雷码编码避免,因为格雷码每次只改变一位)。那么多位Bit信号如何同步?我们可以利用异步FIFO,或者握手协议等其他方式同步。

信号同步进阶

根据两个频率域时钟速度的相对快慢,我们把单比特信号的同步分为两种情况,对于这两种情况,需要采用不同方法来进行同步。

快时钟同步慢时钟域下的异步控制信号

在这种情况下,可能会出现异步信号在自己的慢时钟域中只维持了一个时钟的有效时间,但在快时钟域却被采样了多次,这可能会导致目标时钟域误以为有多个连续的有效控制信号(这里和之前的信号沿检测文章中要求输出一个单周期宽度的检测信号类似,见https://blog.csdn.net/weixin_45791458/article/details/128690161?spm=1001.2014.3001.5501)。

这里采用的方法为在两级同步器后再加一个级别,然后利用第三个同步器的低电平和第二个同步器的高电平译码出一个周期的高电平。

input sig_a;

input clkb;

input rstb;

reg sig_a_d1,sig_a_d2,sig_a_d3;

wire sig_a_posedge;

assign sig_a_posedge=sig_a_d2&!sig_a_d3;

always@(posedge clkb,negedge rstb)

begin

if(!rstb)

begin

sig_a_d1<=1'b0;

sig_a_d2<=1'b0;

sig_a_d3<=1'b0;

end

else

begin

sig_a_d1<=sig_a;

sig_a_d2<=sig_a_d1;

sig_a_d3<=sig_a_d2;

end

end慢时钟域同步快时钟域下的异步控制信号

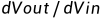

用慢时钟同步快时钟域下的控制信号带来的问题是可能在慢时钟到来之前,快时钟的控制信号已经失效,这样就丢失了控制信号,显然造成了功能错误,信号波形如下图所示。对于这个问题,常见的是使用握手机制。

握手机制(一)

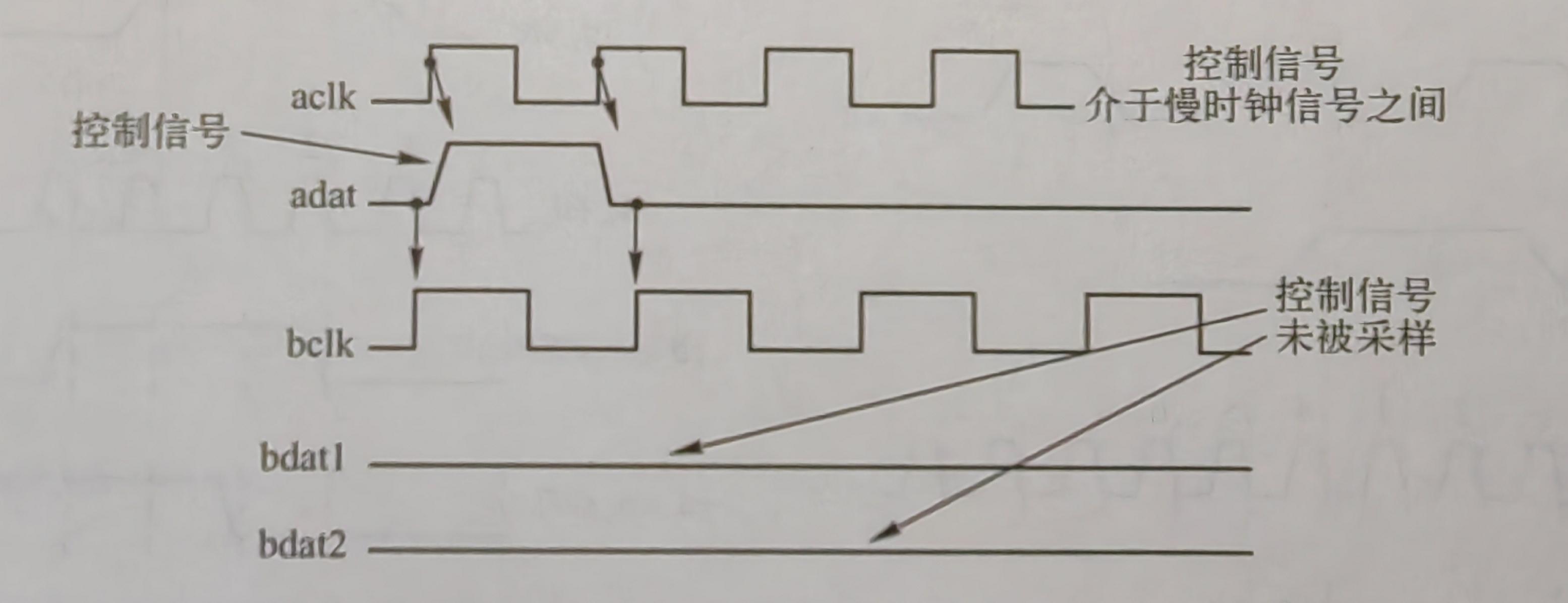

我们通过握手机制,人为锁存快时钟域的控制信号,然后通过同步器穿越边界,使慢时钟域采样到信号,再通过同步器反馈给快时钟域,接着快时钟域释放当前控制信号,这时就可以响应下一个控制信号,原理图如下所示。

其中,数据从adat输入,左下角应该是一个不是一个简单的触发器,而是可以根据反馈信号锁存adat的触发器,锁存后的信号为adat1,这个信号通过两级同步器进入慢时钟域,并将反馈信号(这里是信号本身)同步会快时钟域,表示信号已收到,可以取消快时钟域的锁存信号了,并等待下一个adat有效信号的到来。

用Verilog HDL实现的快时钟域的锁存代码如下。

module adapt_gen(input aclk,rest_b,adat,abdat2,output reg adat1);

always@(posedge clk,negedge rest_b)

if(!reset_b)

adat1<=1'b0;

else

if(abdat2)

adat1<=1'b0;

else

adat1<=adat;

endmodule

这种方法不能解决快时钟域信号在两个慢时钟域信号间多次翻转的问题。握手机制默认了这种情况不存在,也就是说,在设计时,必须保证快时钟域两个有效信号间的最小时间限制。这个最小值是反馈回路的延迟和第一个同步器恢复无效状态的时间之和。

握手机制(二)

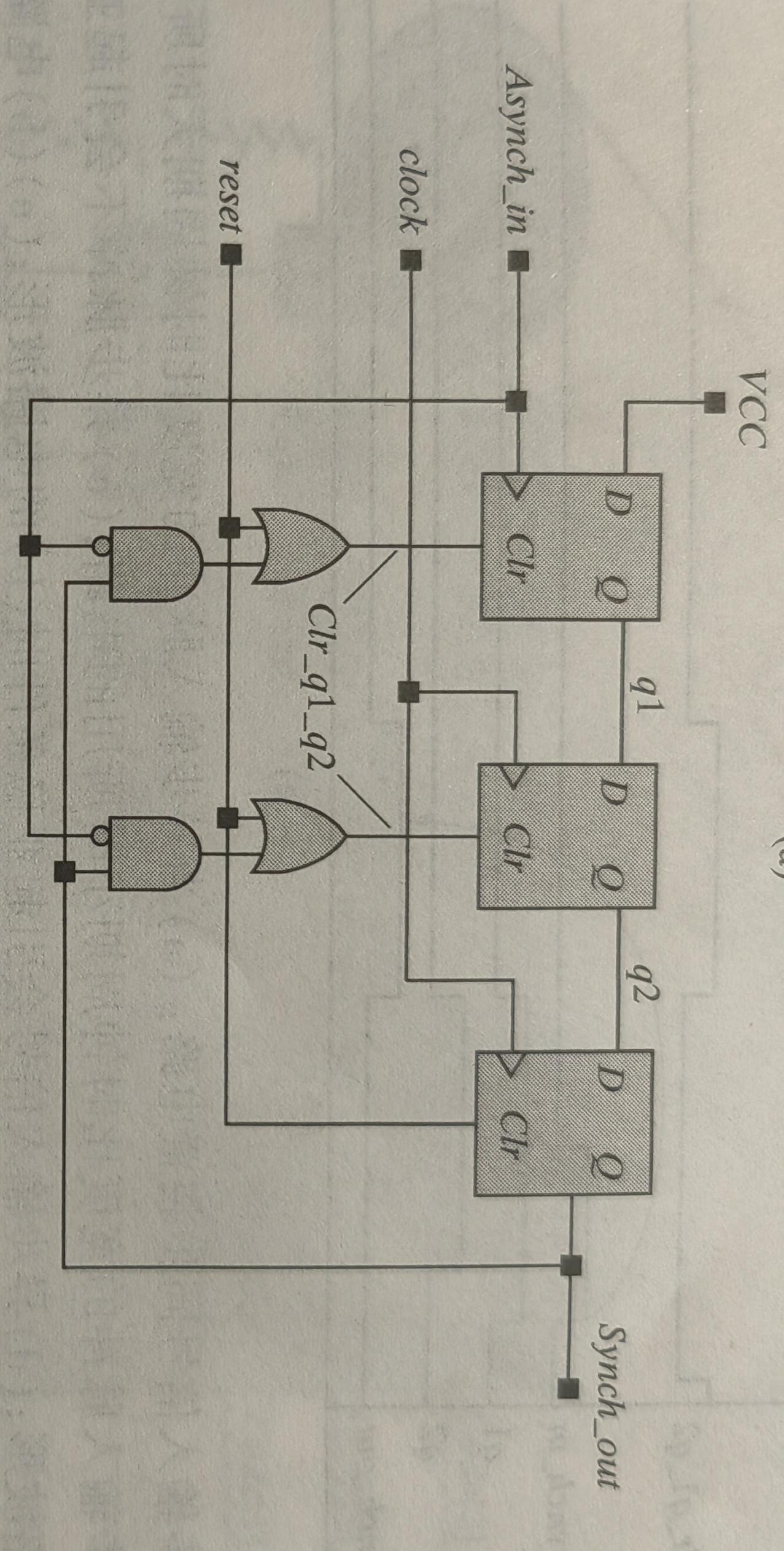

我们还可以将快时钟域异步信号连接到一个D触发器的时钟端,而输出端连接至高电平,然后通过两级同步器连接至慢时钟域,慢时钟域收到信号后给出反馈信号,复位D触发器和第一个同步器,如下图所示。

当异步信号有效沿来临时,D触发器的输出q1被置为1,此时q1可能不满足第一个同步器的建立时间要求,导致q2出现亚稳态,但在Synch_out端,亚稳态不会出现(同步装置的原理),输出被反馈回到复位端,与输入信号的低电平一起复位前两个触发器,这样使得输出信号的宽度为一个慢时钟域时钟周期。

以上内容来源于《Verilog高级数字系统设计技术和实例分析》、《SOC设计方法与实现》和《Verilog HDL高级数字设计》