文章目录

前言

目前正在备考24考研,现将24计算机408学习整理的知识点进行汇总整理。

博主博客文章目录索引:博客目录索引(持续更新)

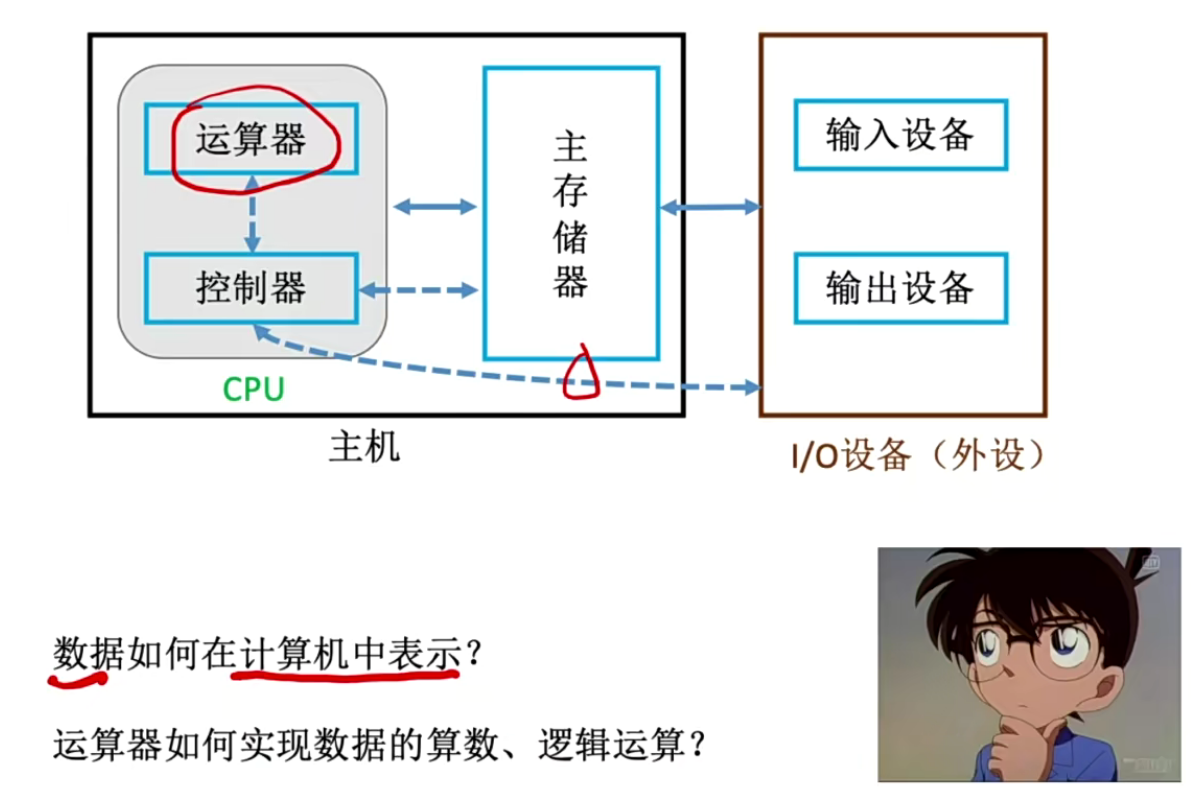

一、数制与编码

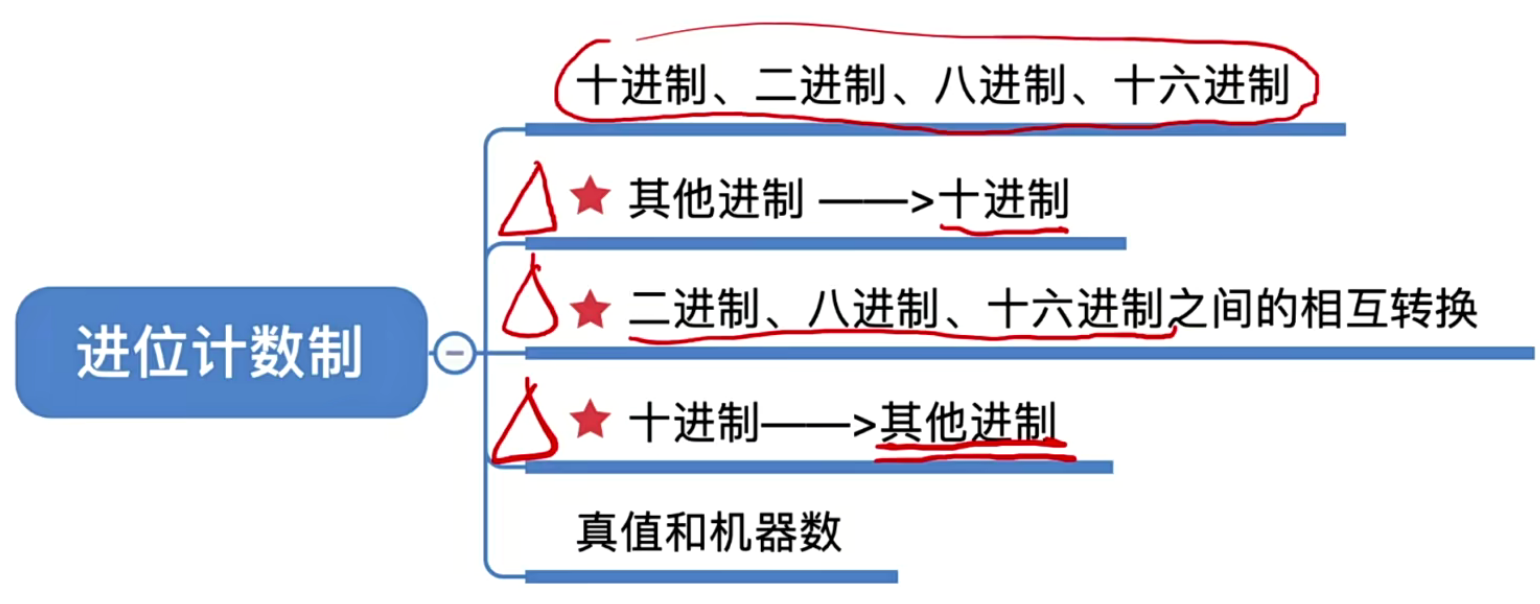

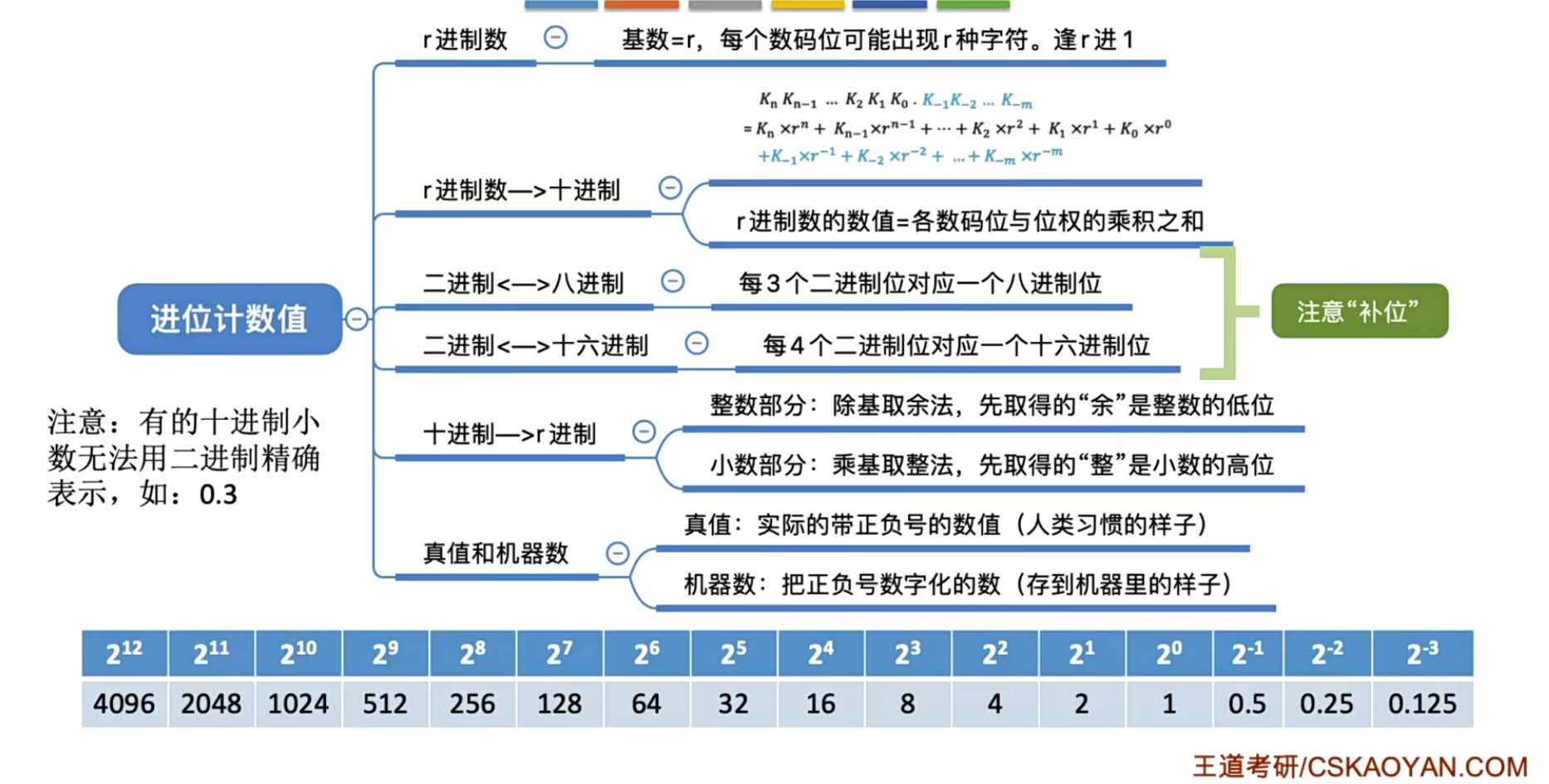

1.1、进位计数制

1.1.1、计数方法(最古老计数方法、十进制计数、r进制计数)

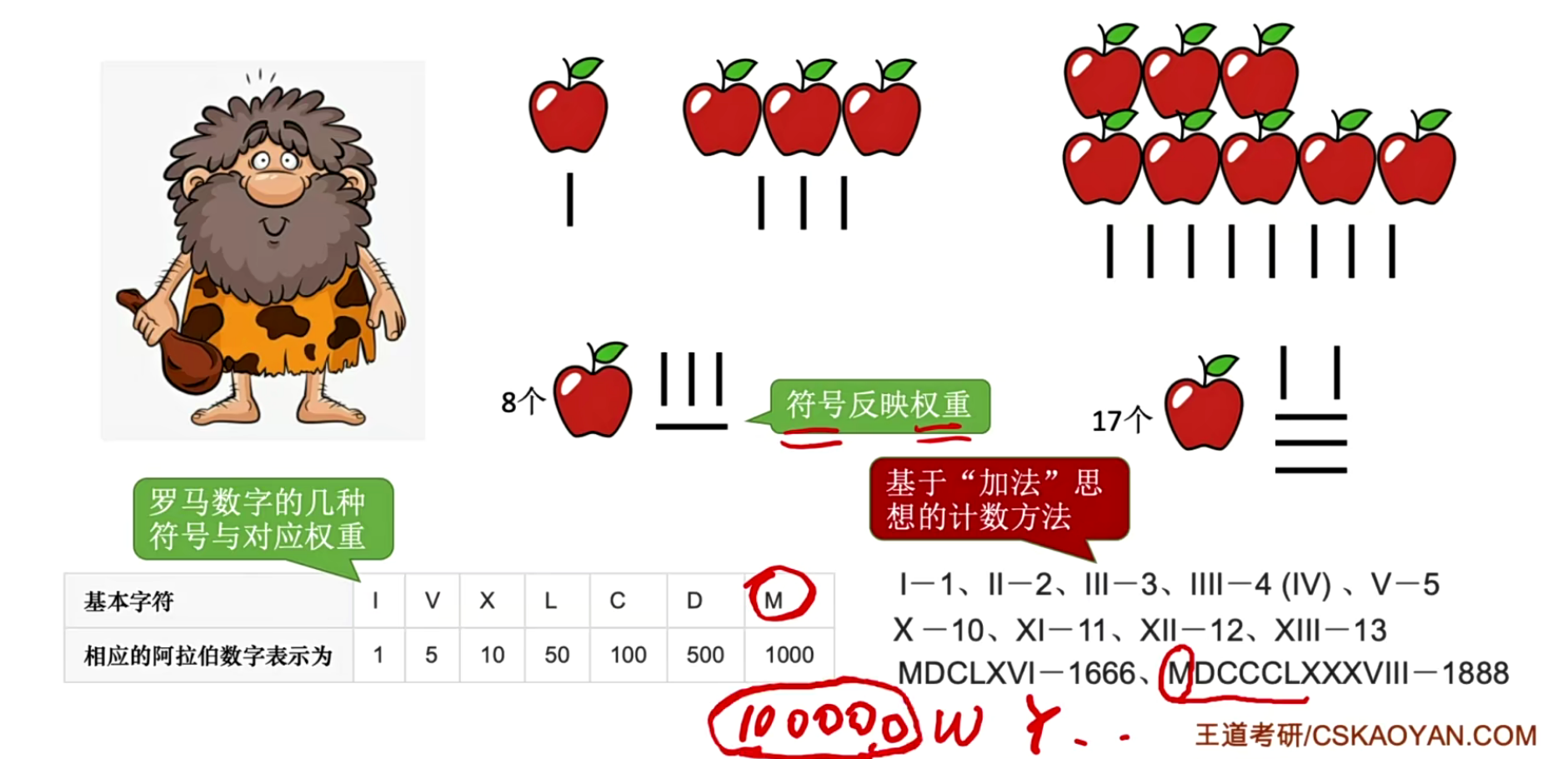

最古老的计数方法:一开始是以基本字符来进行表示的数字,其有一个缺陷就是当我们要表示更大的数字之后,此时我们就需要去构造更大的字符,如之后的10000、100000等等,这就产生出了弊端。

- 其中MDCCCLXXXVIII:表示1个1000 + 1个500 + 3个100…,最终通过加法思路来得到这个数字。

十进制计数法:

位权·:根据对应数字的位置来去表示的权重。

- 人有10根手指,能够逢十进一,比较符合人类的规律。

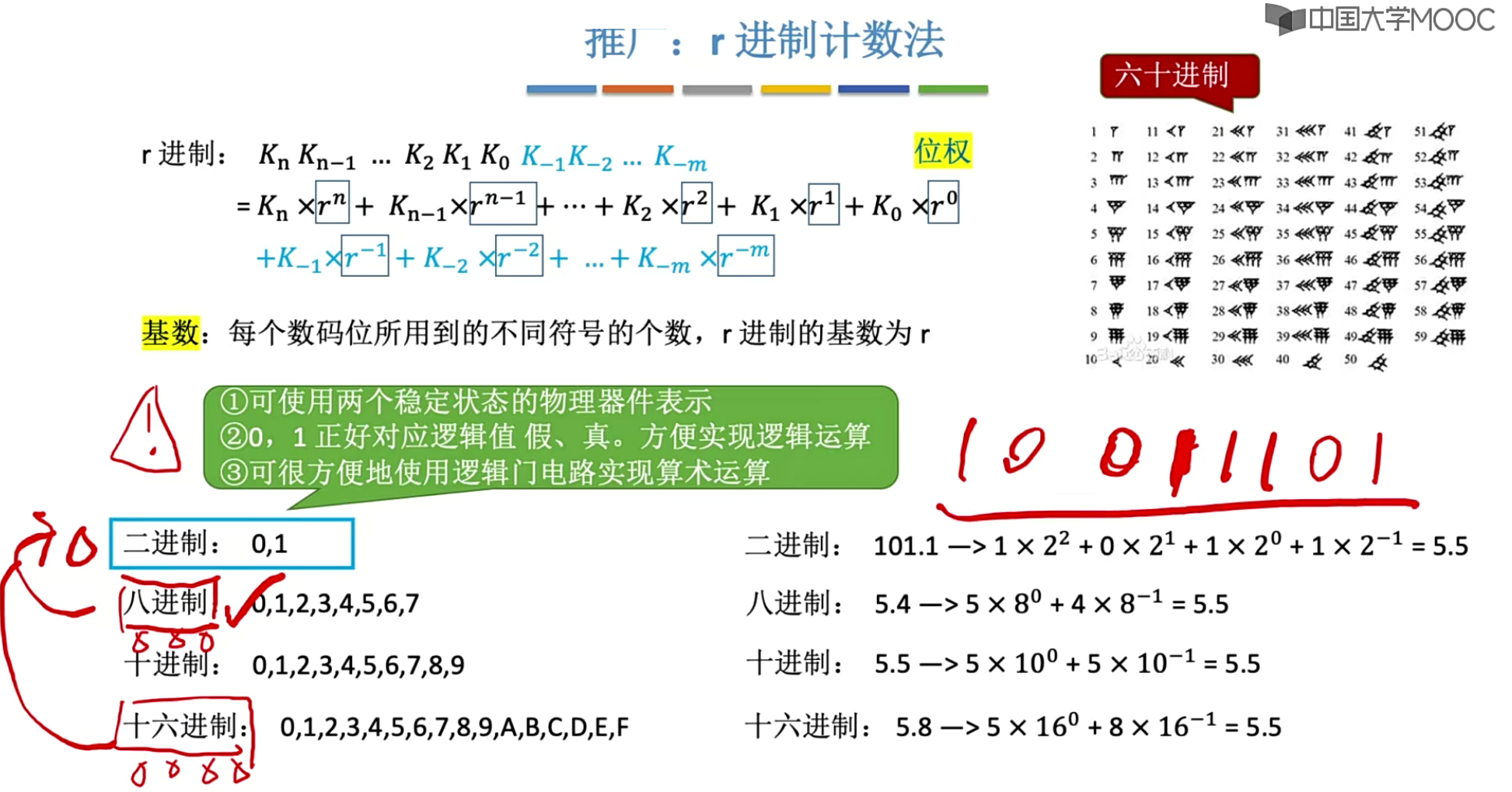

推广:r进制计数法

六十进制:时间

计算机中通常使用的是二进制、八进制、十六进制。不同的r进制需要逢r进1。

基数:每个数码位所用到的不同符号的个数,r进制的基数为r。

1.1.2、进制转换

①任意进制转为十进制

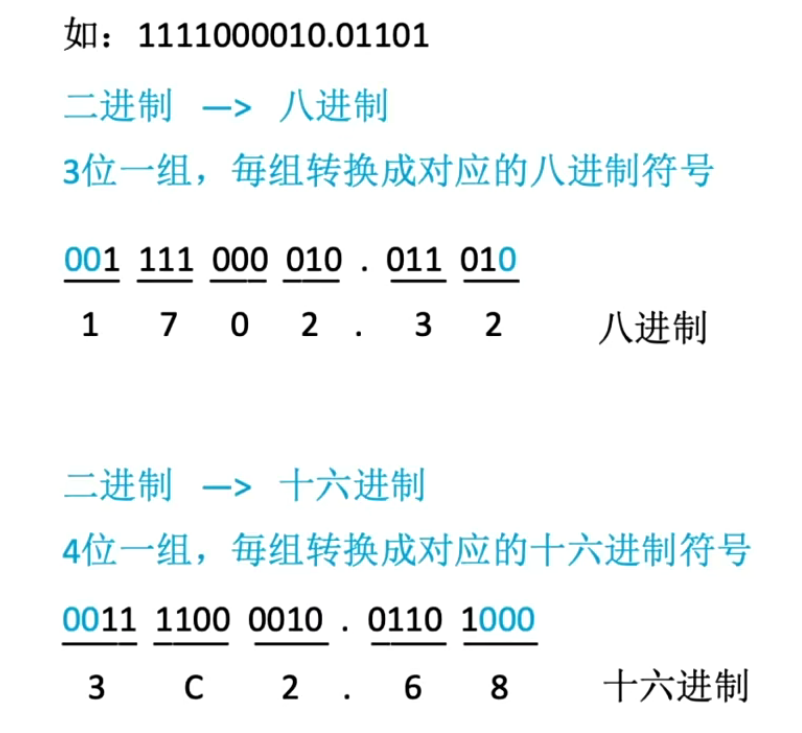

②二进制转八进制、十六进制

③八进制、十六进制转二进制

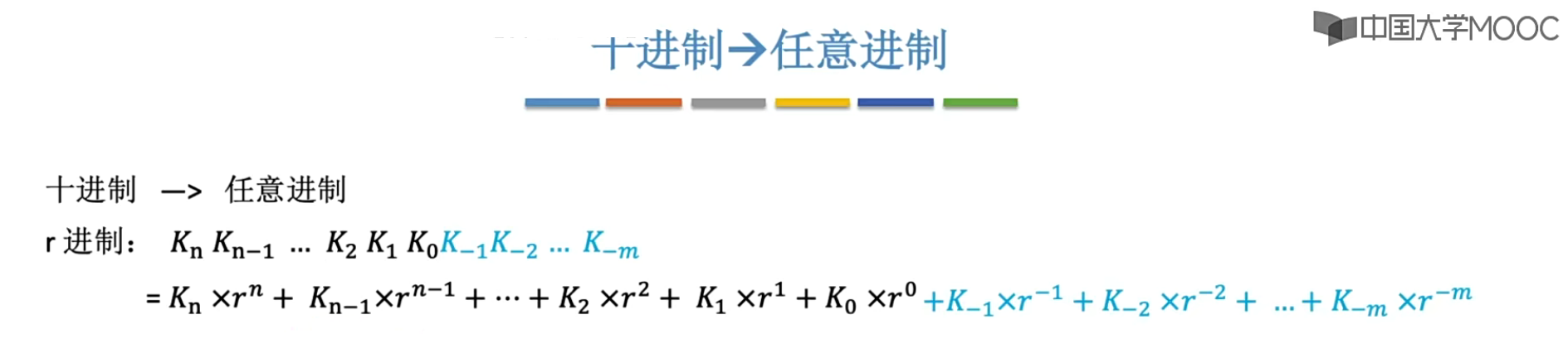

④十进制转任意进制(包含整数、小数,拼凑法)

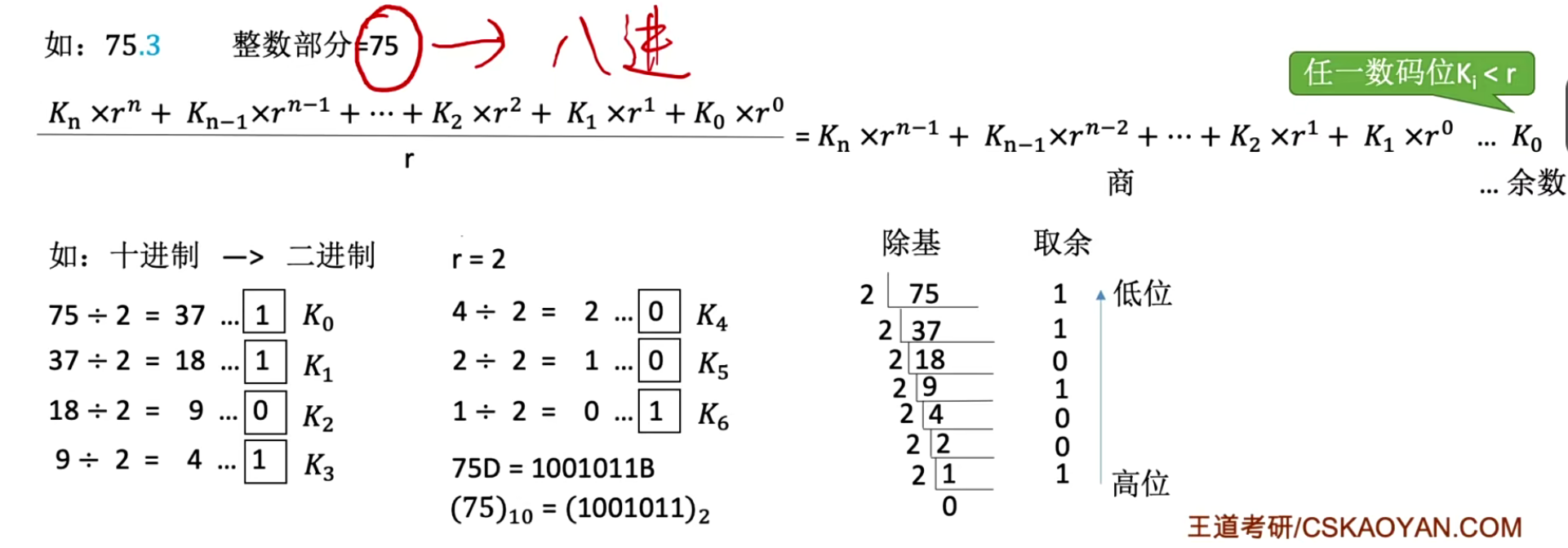

针对于十进制整数部分处理:不断的通过除法取余得到位数

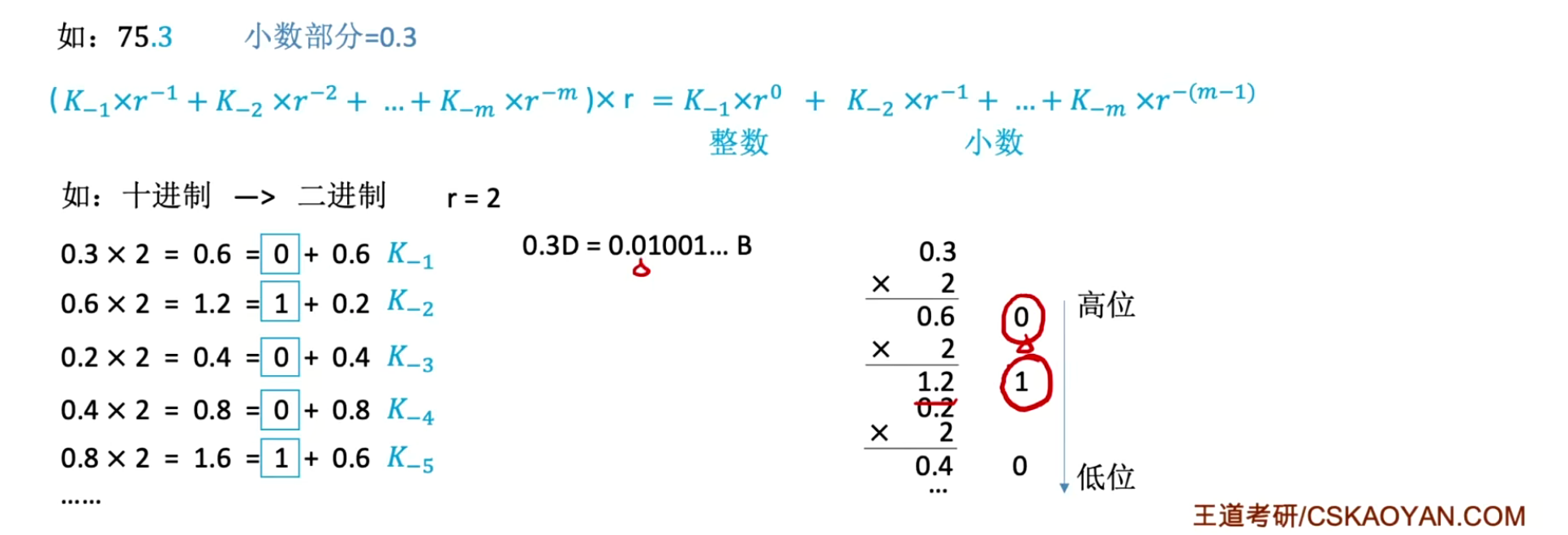

针对于十进制小数部分处理:

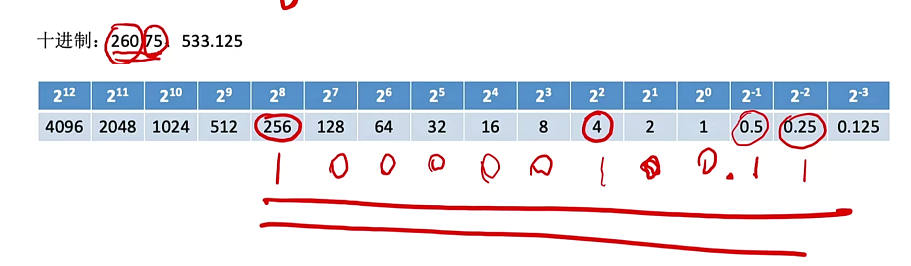

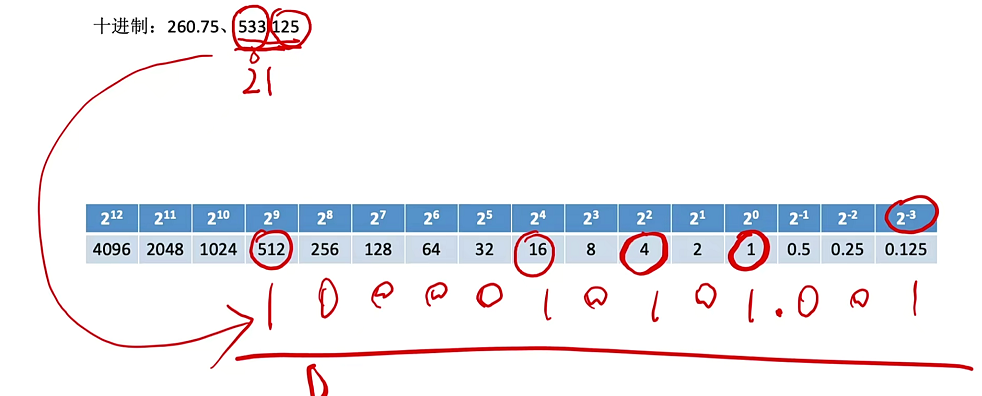

十进制转二进制(拼凑法)

对于十进制转八进制或者其他的,可以先去转为二进制,接着二进制再去转对应的r进制:如下借助上面的例子继续往下,最后得到的八进制数为1025.1

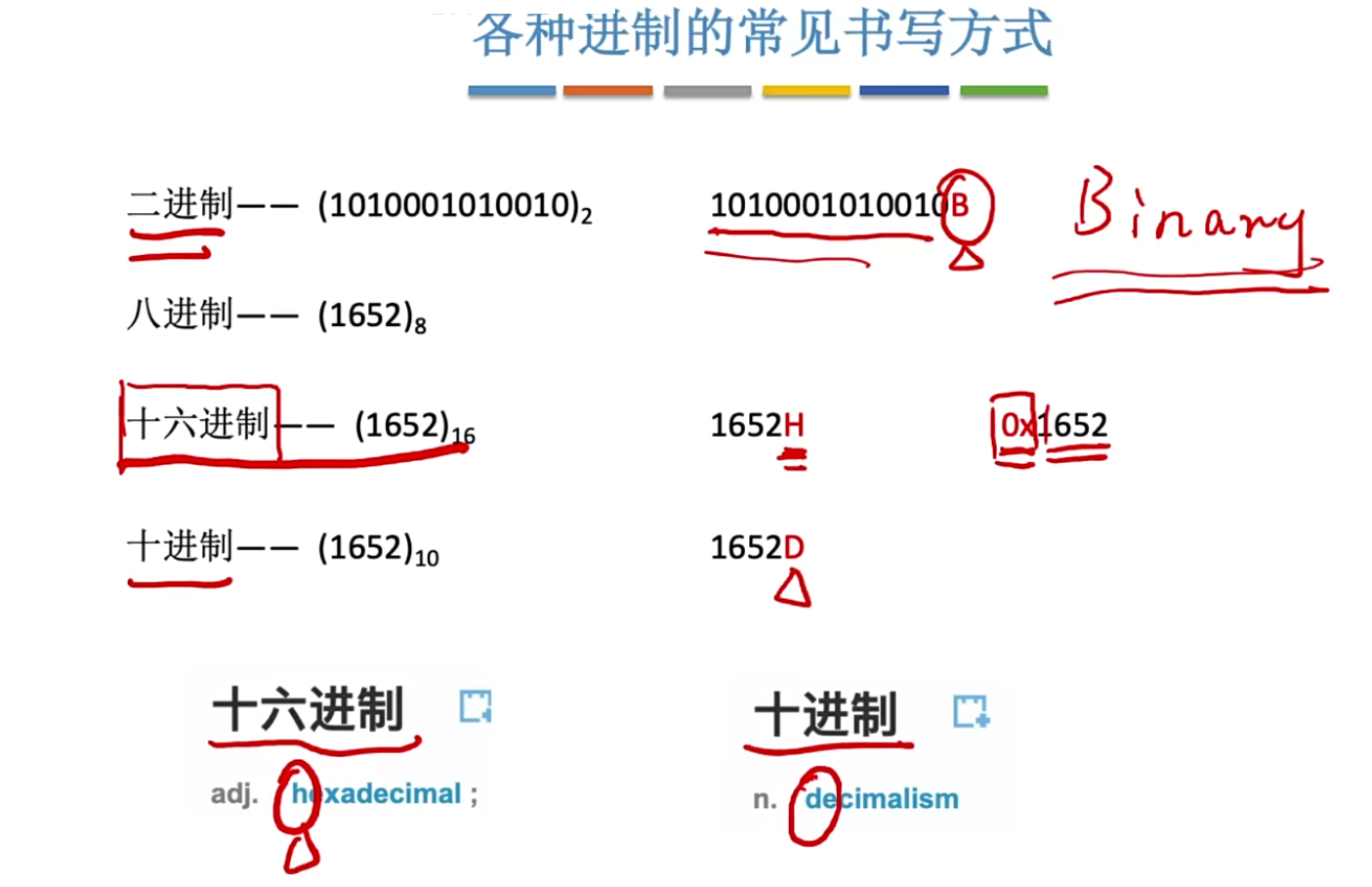

1.1.3、各种进制的常见书写方式

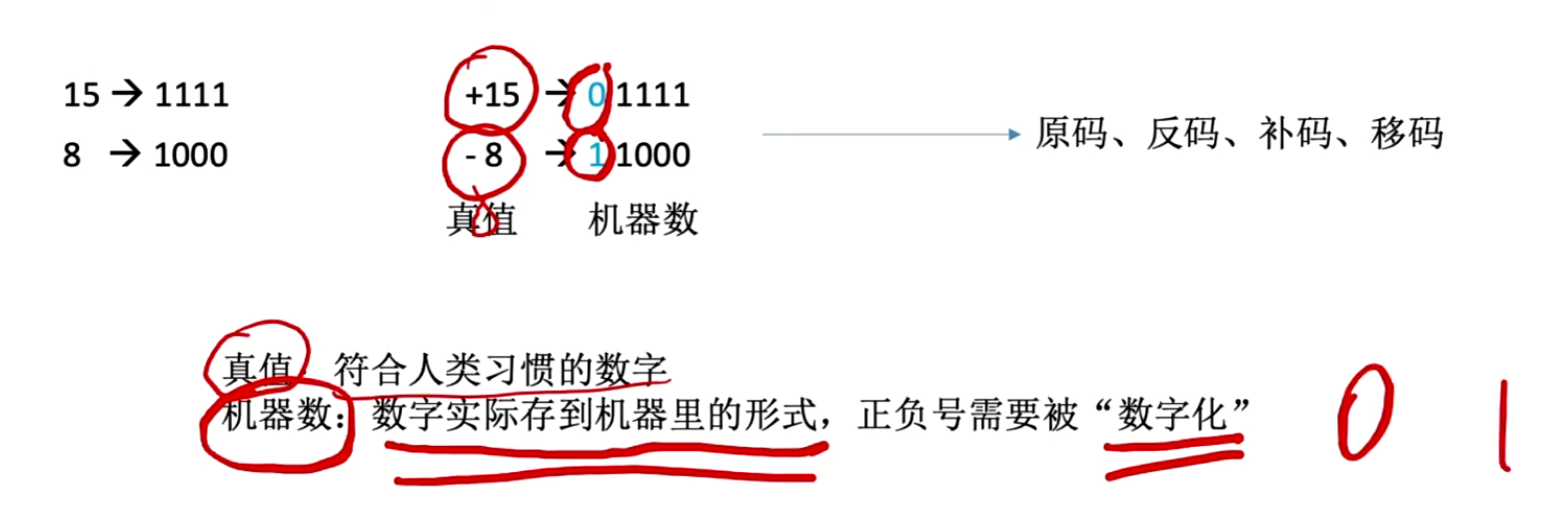

1.1.4、真值和机器数

知识回顾与重要考点

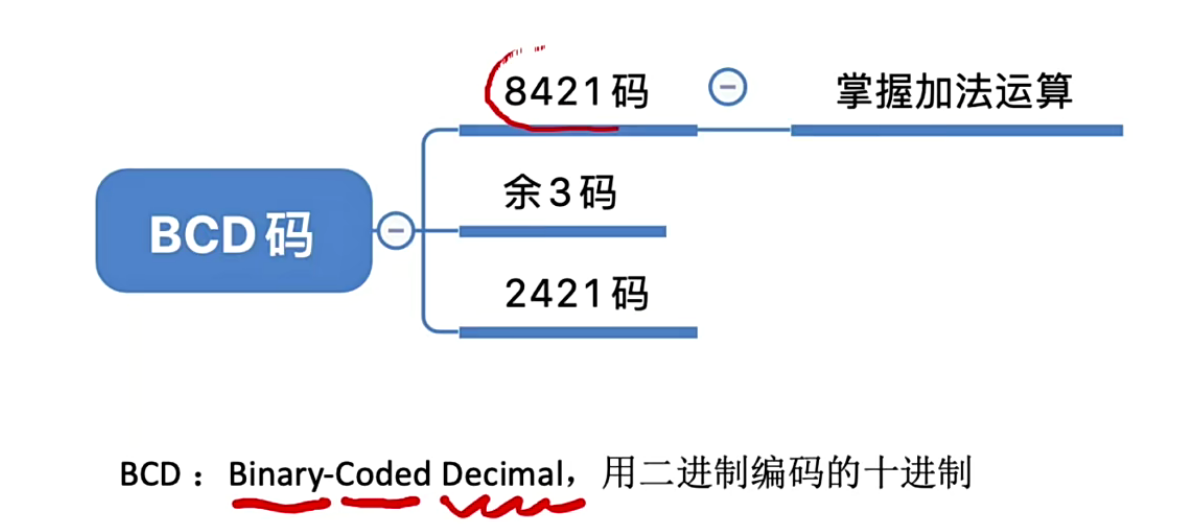

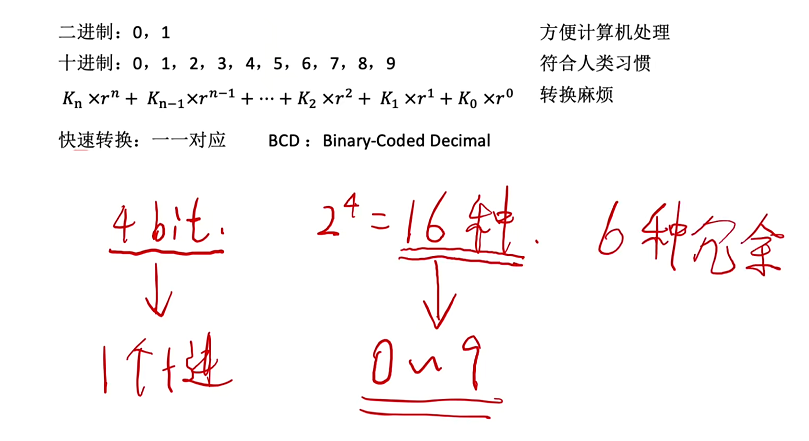

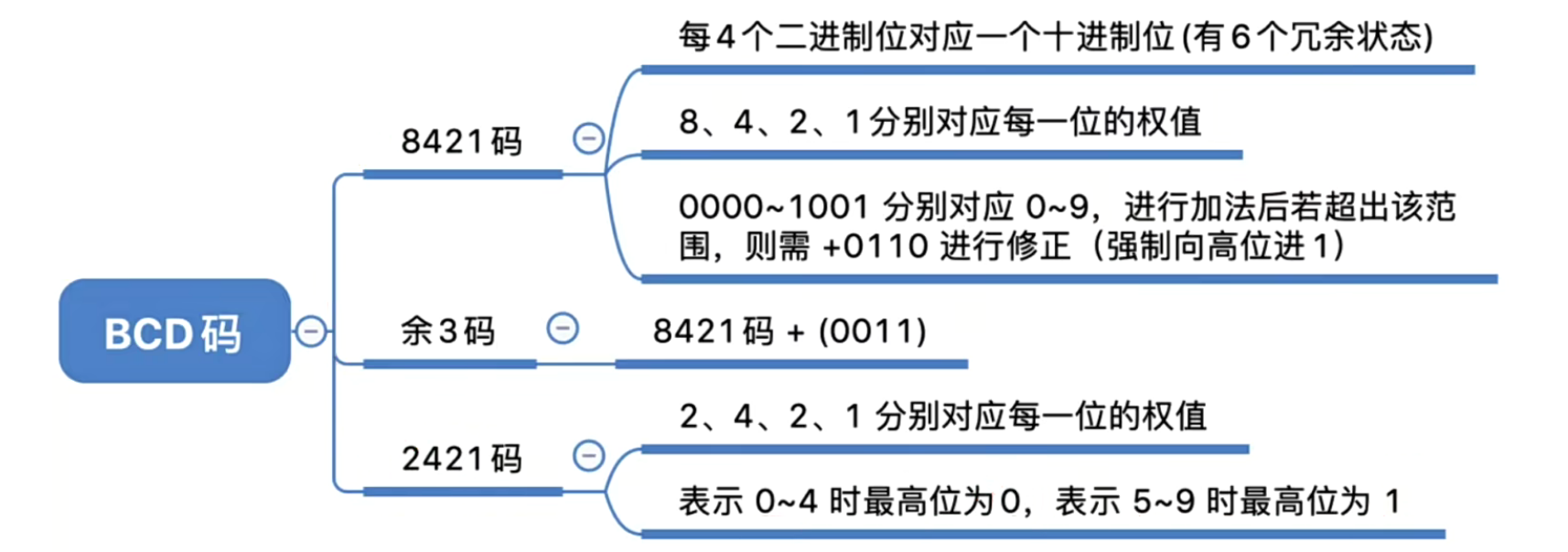

1.2、BCD码

1.2.1、认识BCD码

四个bit位来对应一个十进制位

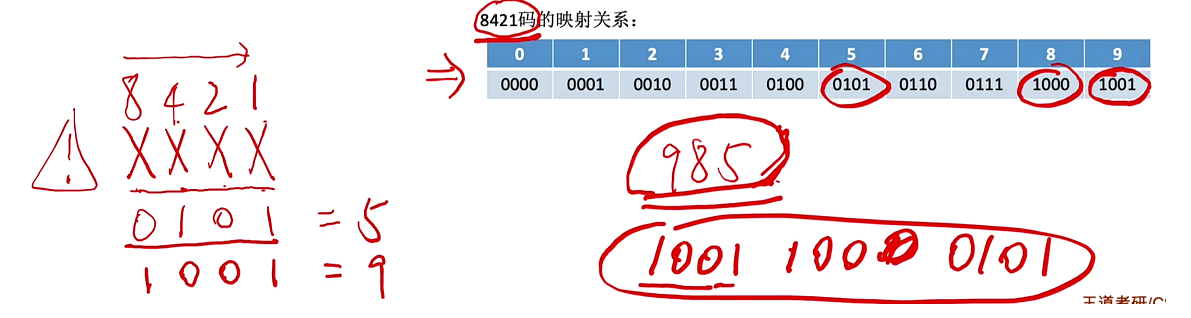

1.2.2、认识BCD的编码方式:8421码(有权码)

第一种BCD码的编码方式为:8421,即每4位表示一个数字

对于8421如何进行加法计算呢?

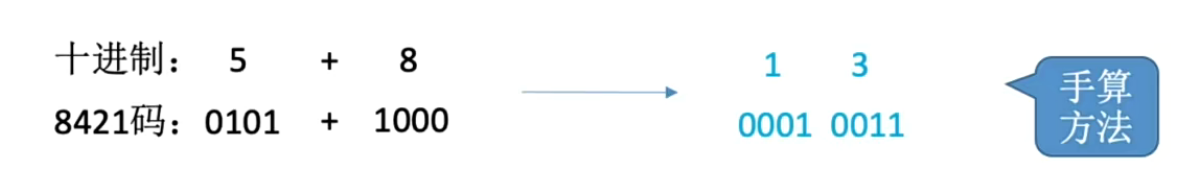

①手算方式:首先使用十进制来加到结果,接着转换为8421表示。

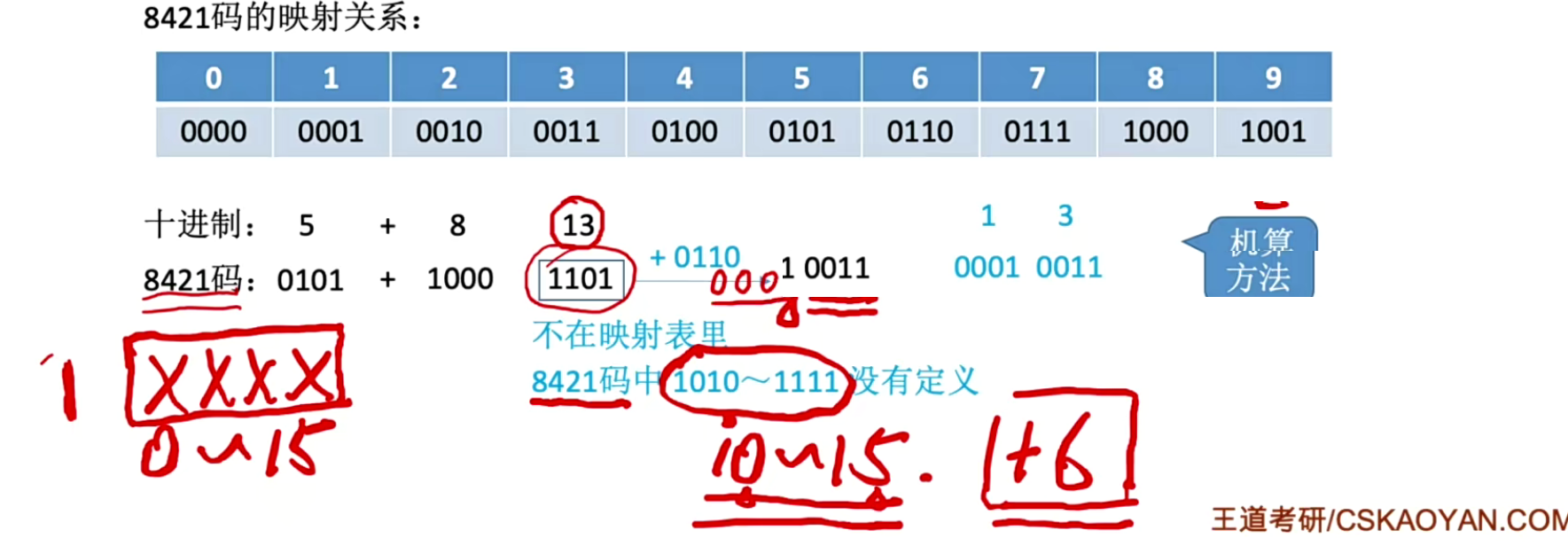

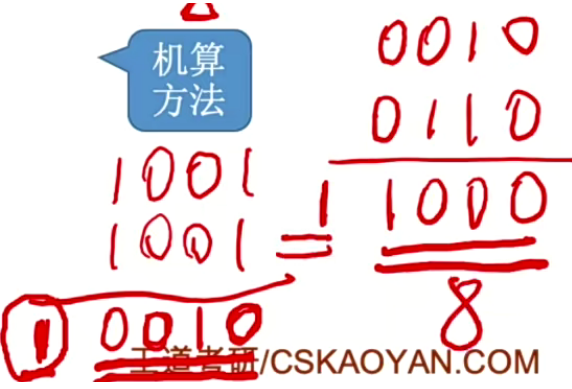

②计算机方式:

步骤:①首先直接进行二进制计算。②判断是否在0-9中且在1010-1111中有定义,若是在直接表示,若是不在+6。③得到的结果用8421方式四位表示一位对应。

示例对于9+9情况:18的二进制为10010,实际上这个整体已经超过了1010-1111,则也要进行+6,此时修正得到为11000,也就是18。

注意:若是相加结果在合法范围中,则无需修正。

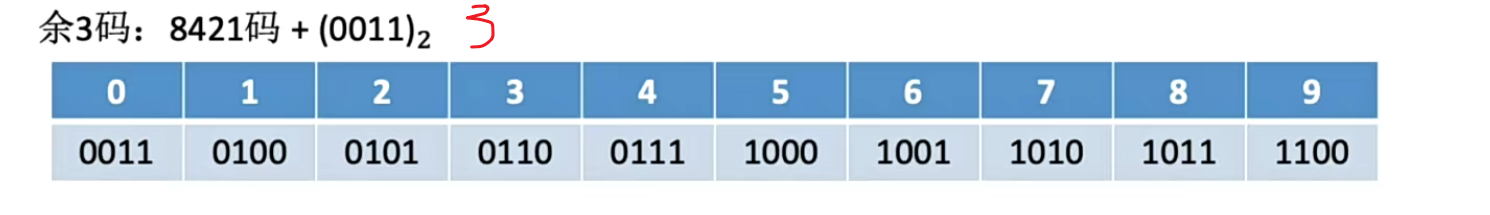

1.2.3、余三码(无权码)

余三码指的是在8421码上+3来得到一个新的映射方案。

在8421码中,每个位都有固定的权值,表示的四位,分别是8、4、2、1;在余三码中每位并没有固定的权值。

- 8421称为有权码,余3码称为无权码。

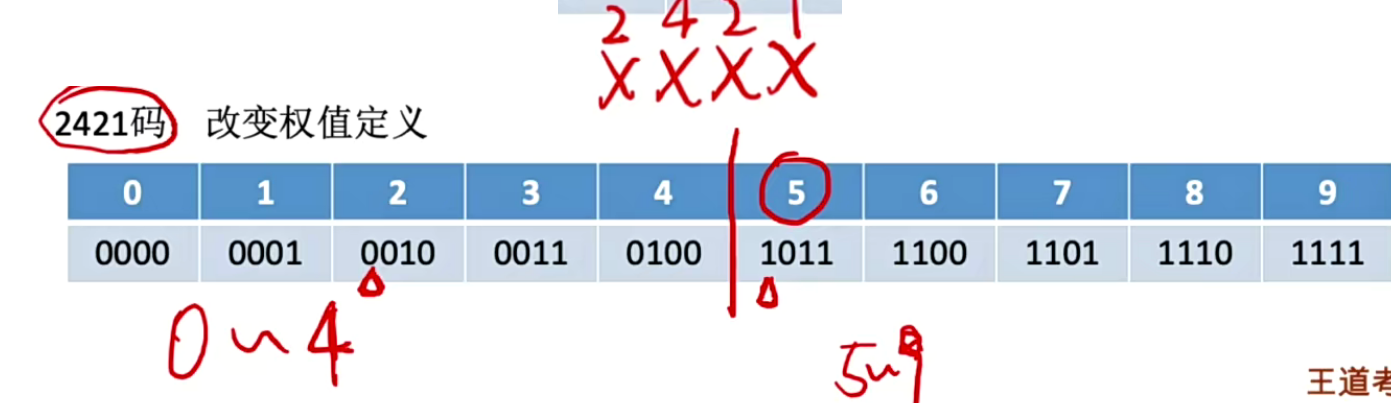

1.2.4、2421码

同样也是用4位来进行表示,分别权值从左到右位2 4 2 1:

为了避免有歧义,例如5也可以使用0101表示,也可以使用1011表示,此时就对2421码来做了一个规定。

规约:0-4中的第一位为0,5-9中第一位为1!!!

知识回顾与重要考点

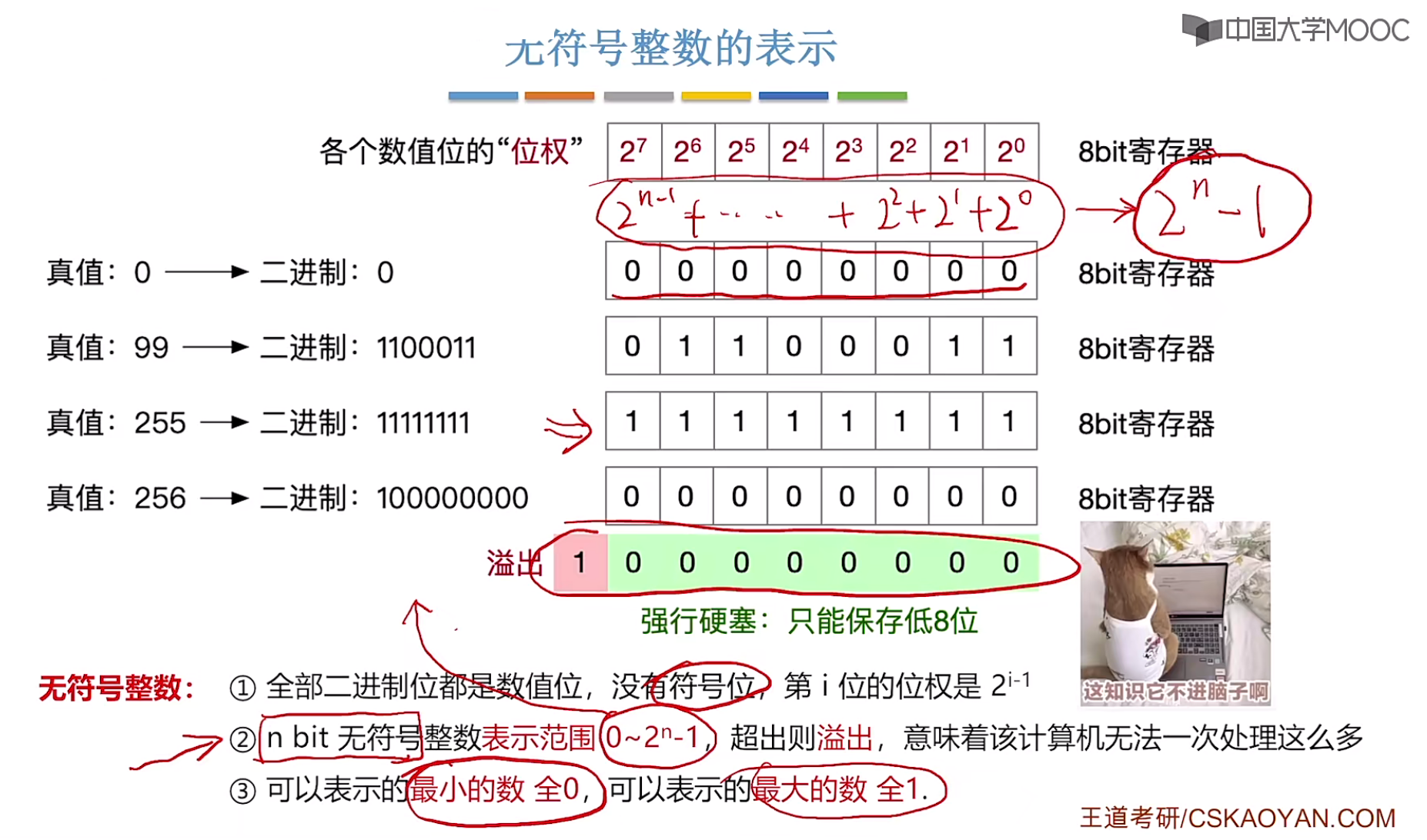

1.3、无符号整数

无符号整数在计算机中的应用:

1.3.1、无符号整数在计算机内部表示

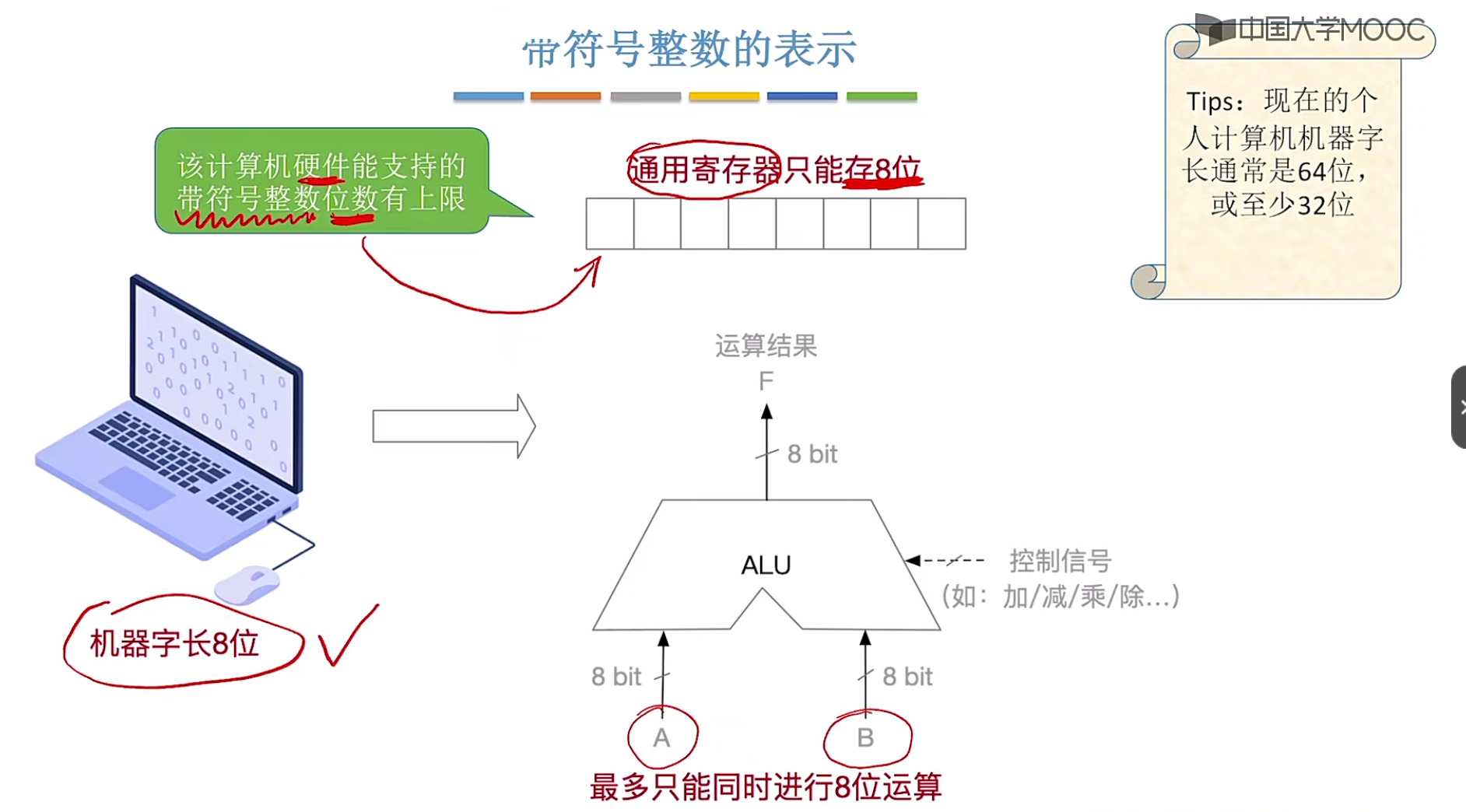

讲解说明按照字长8位来进行介绍,目前一般系统的机器字长为64位或32位。

无符号在二进制中不包含有符号位,不够8位的都可以进行补0:

若是真值大小超过二进制8位,那么会只保留低8位在寄存器中,多余的将会省略。

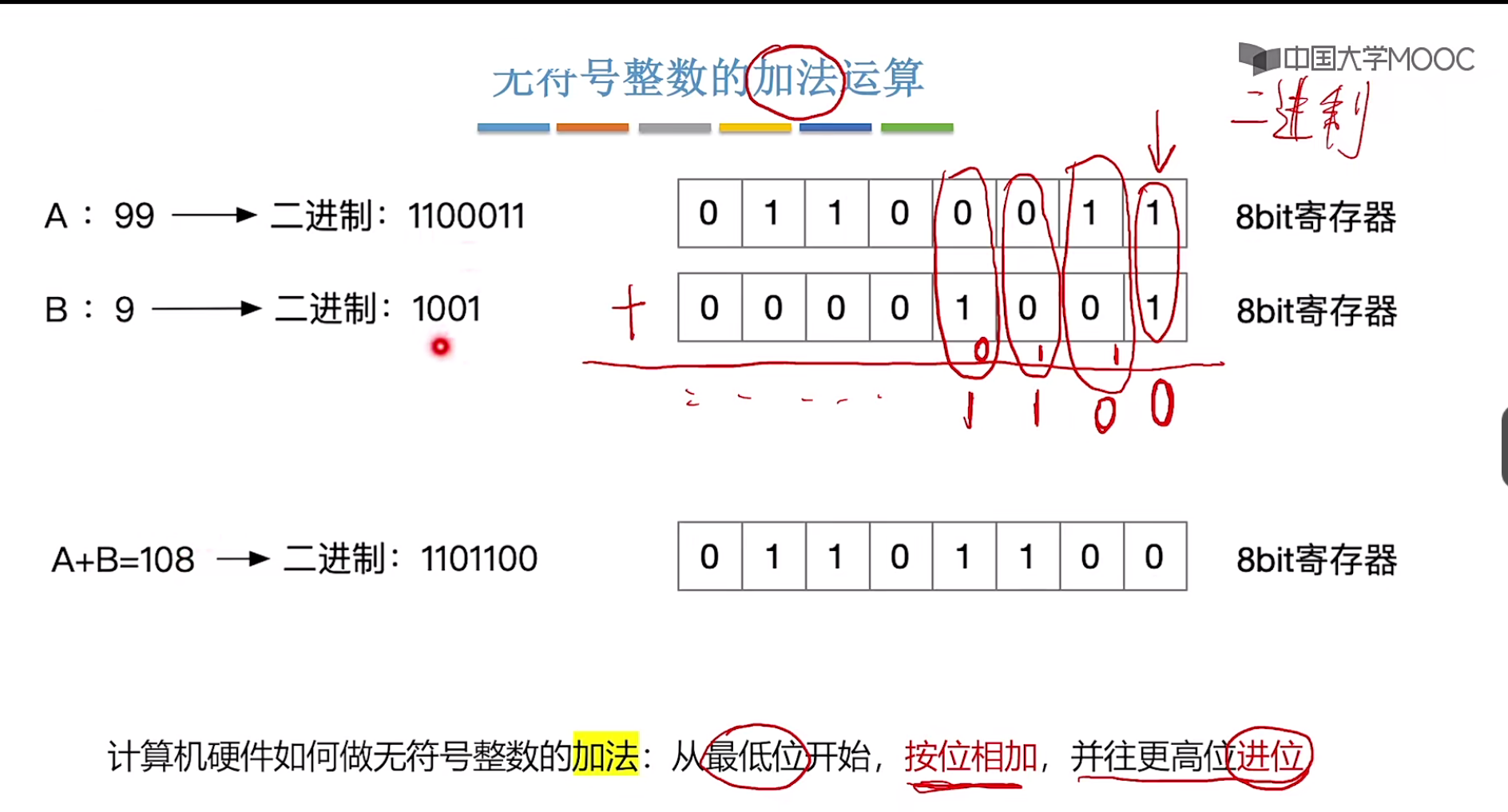

1.3.2、无符号整数的加法运算

直接从低位开始加到高位:

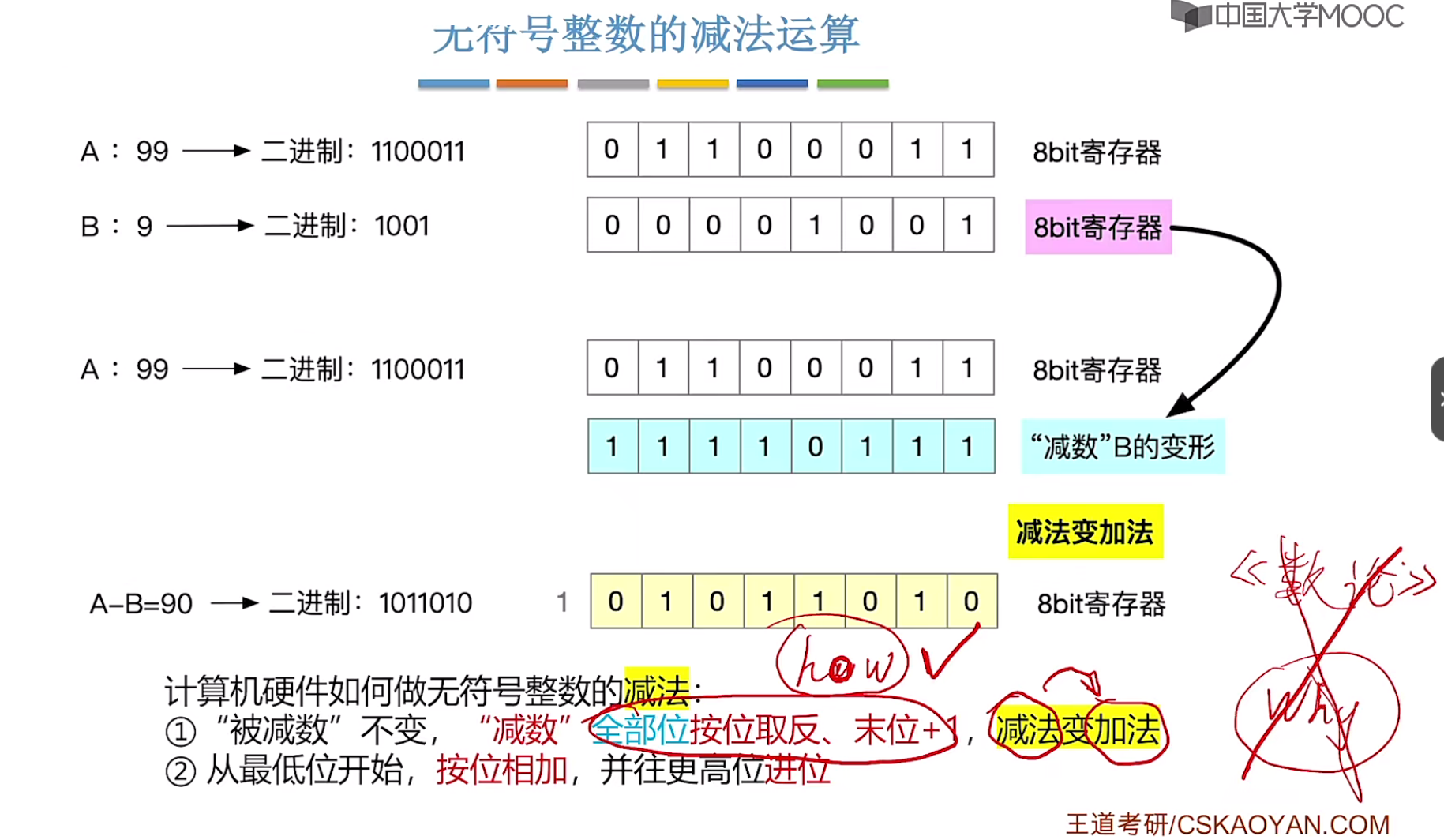

1.3.3、无符号整数的减法运算

减法:将减法变为加法操作。

步骤:①被减数不变,减数全部取反+1。②接着按照加法运算计算得到二进制数。

举例:A=99,B=9,A-B=90

A = 01100011

B = 00001001

①被减数不变 A = 01100011,减数全部取反+1 => 11110111

②加法运算

01100011

+ 11110111

-----------

101011010 => 90

知识点回顾

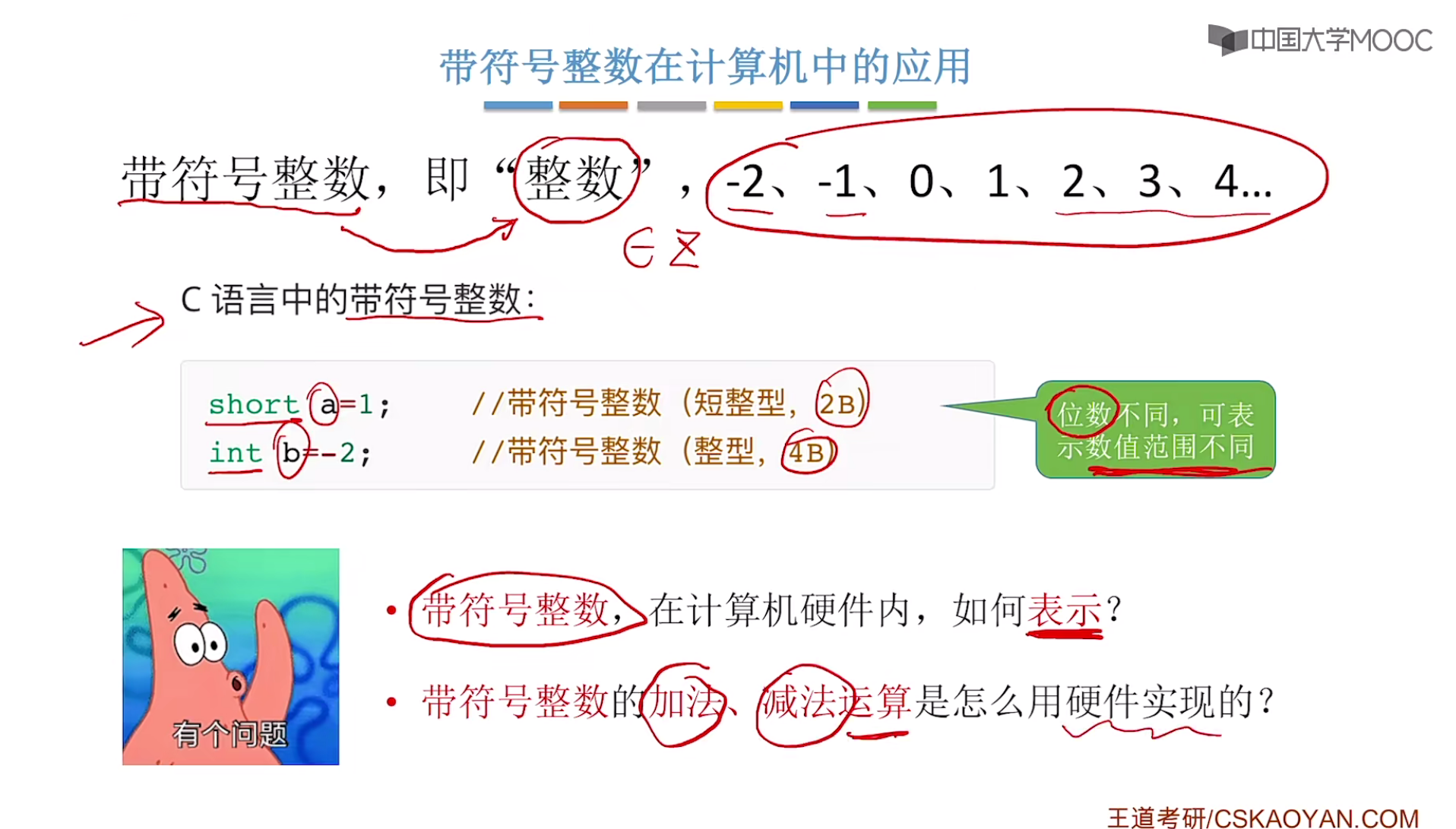

1.4、带符号符号的表示与运算(含原/反/补)

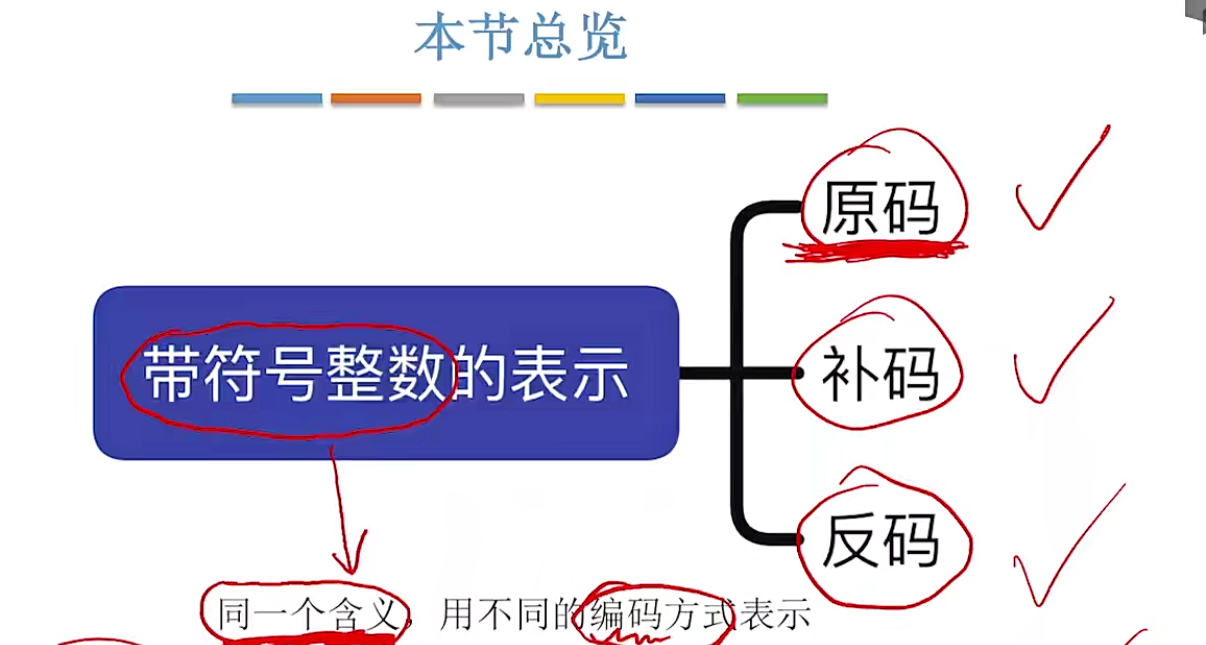

对于同一个数可以在计算机中采用不同的原反补码表示:

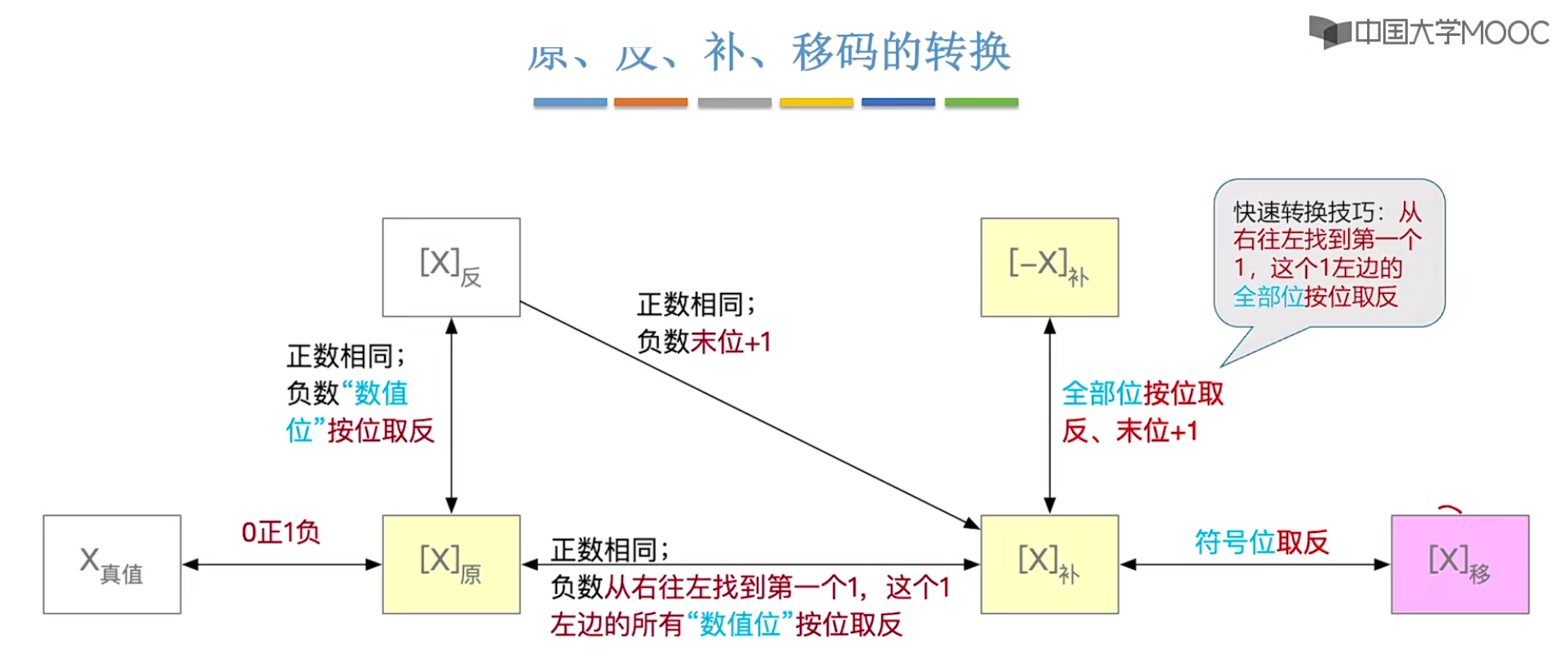

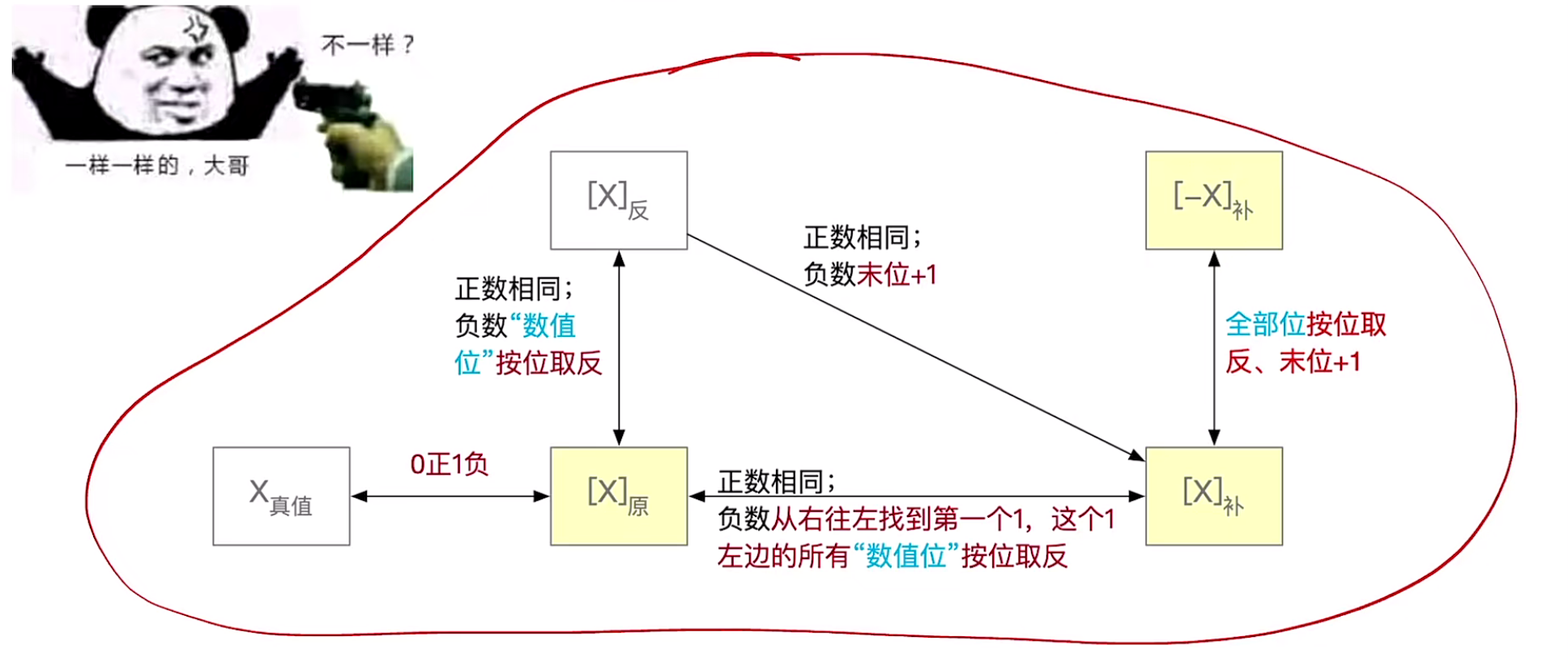

知识补充(原、反、补转换,原码转补码快速方法)

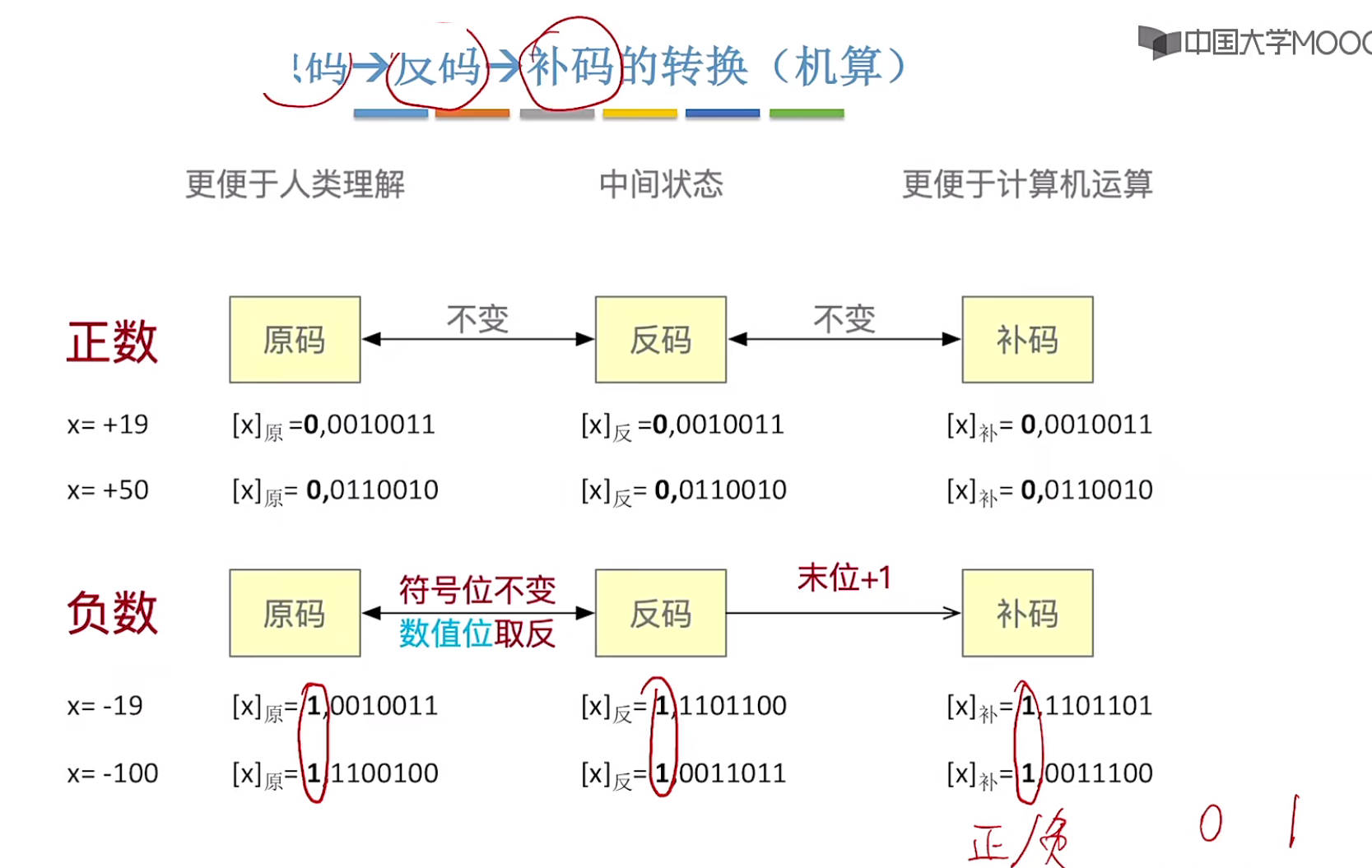

正数:原反补不变。

负数:反码为正数取反,补码为反码+1。

- 上述负数转换是机器转换的过程!

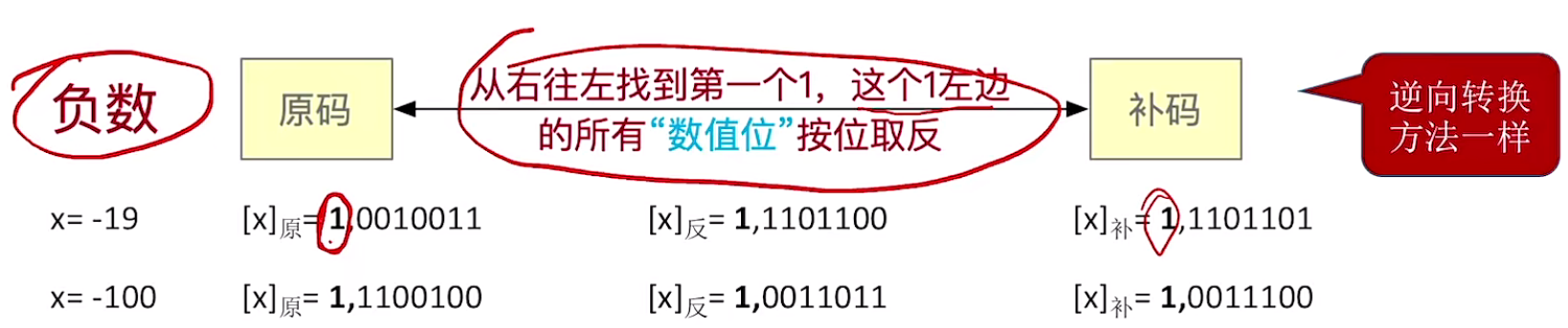

对于负数的原码转换为补码的快速方法:手算十分推荐

1.4.1、带符号整数的表示(原码)

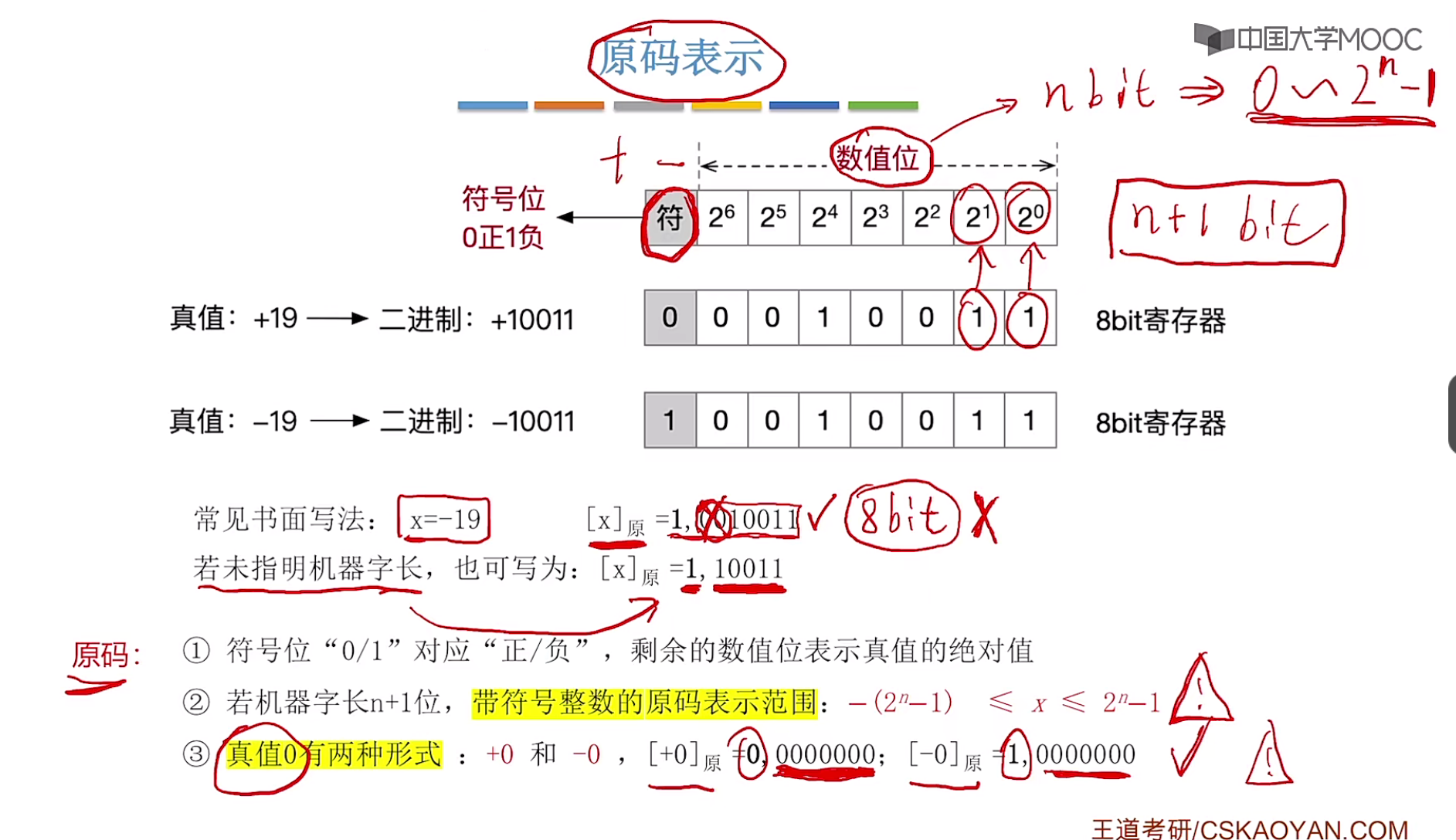

同样使用的是机器字长8位来进行演示!

原码符号位表示:

若是没有指明机器字长,对于x=-19,可以表示为[x]原=1,10011

- 符号位带上逗号!

1.4.2、原码的加减法运算

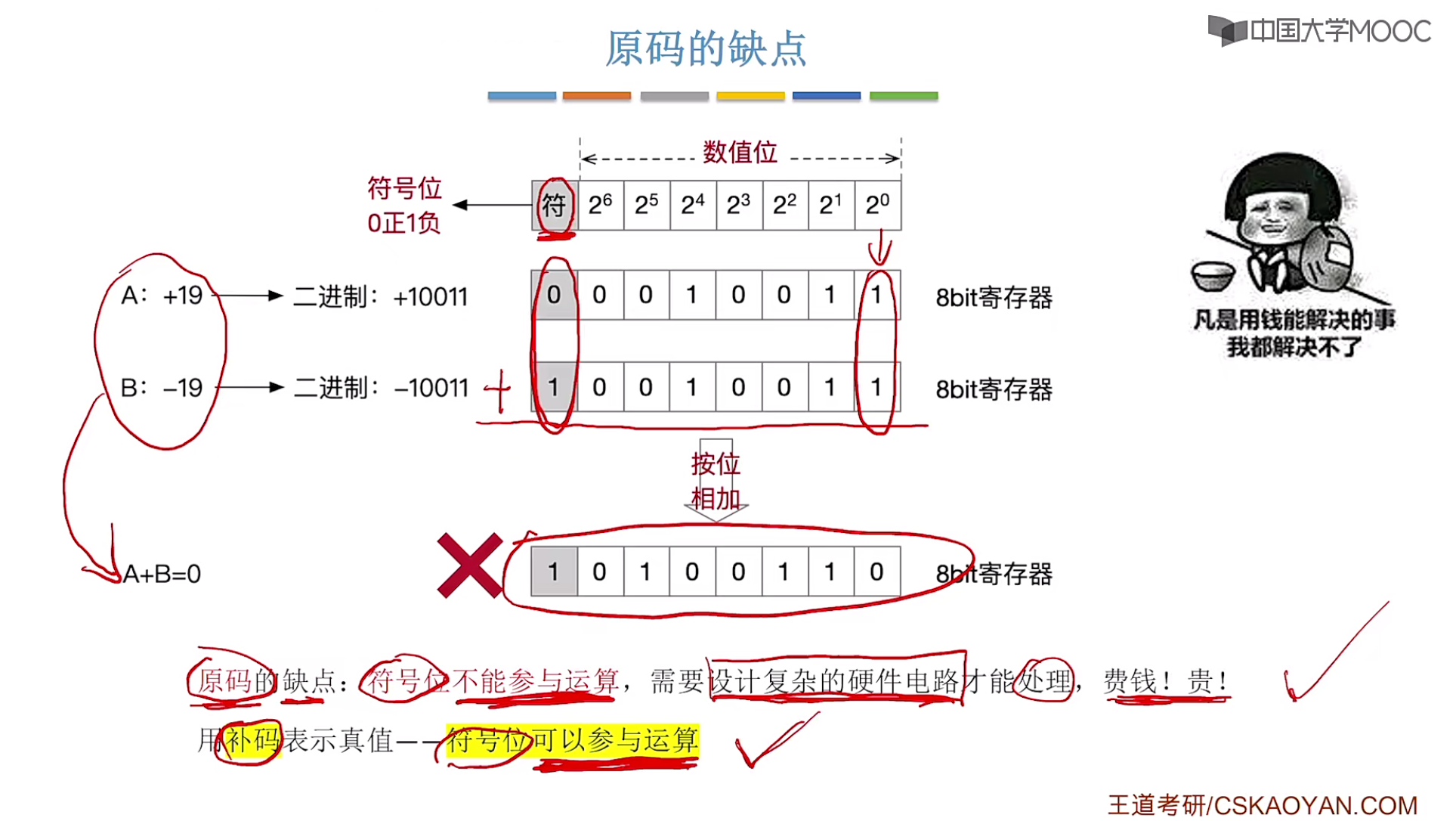

原码的加减法运算:若是按照原先的按位加减则最后结果会有错误,需要设计复杂的硬件电路才可处理

实际最终可采用补码方式来进行运算!

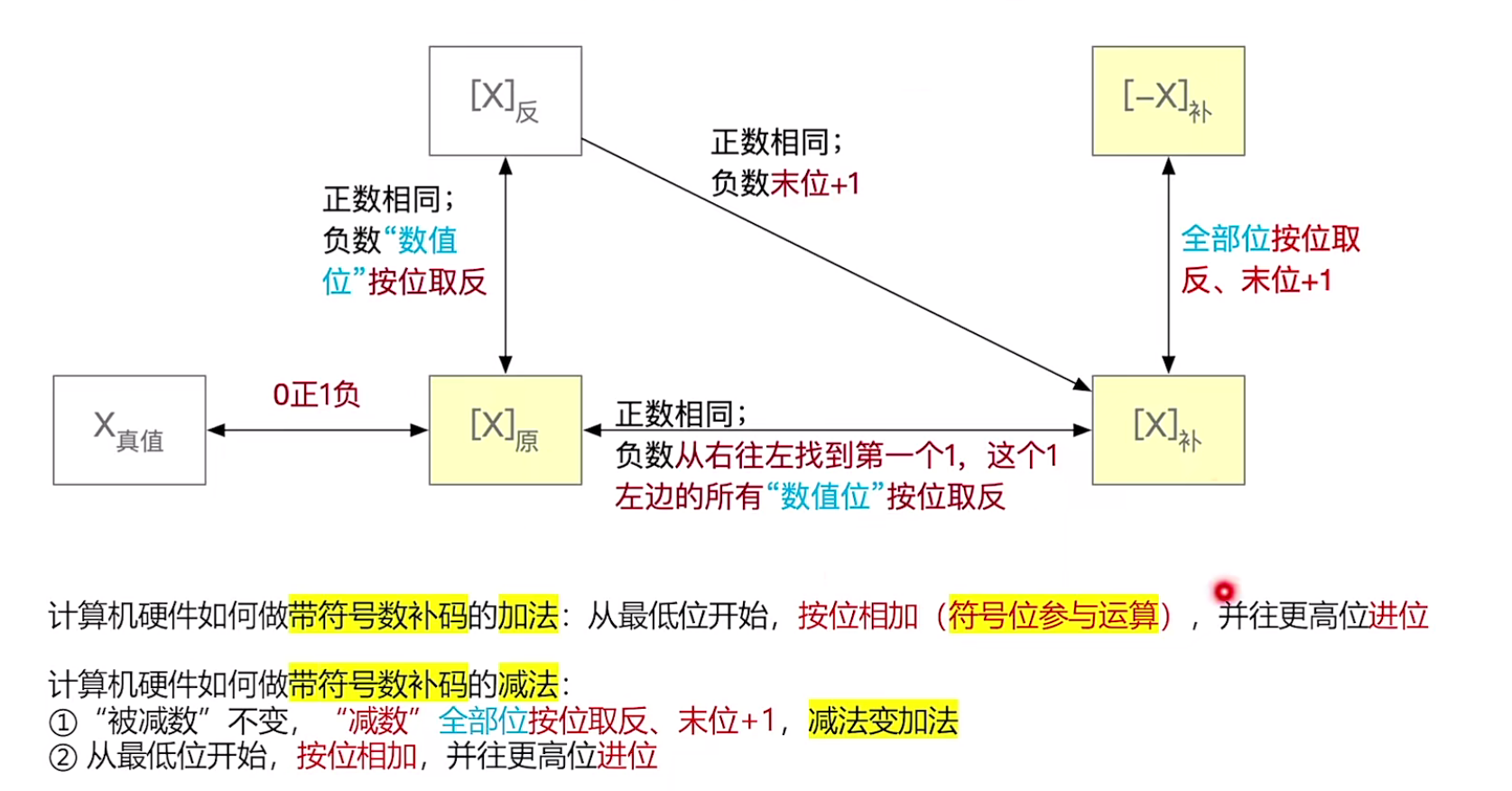

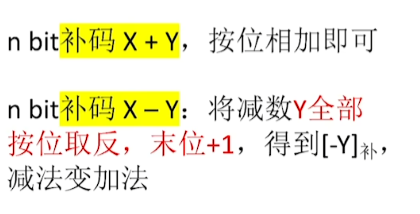

1.4.3、补码的加法运算

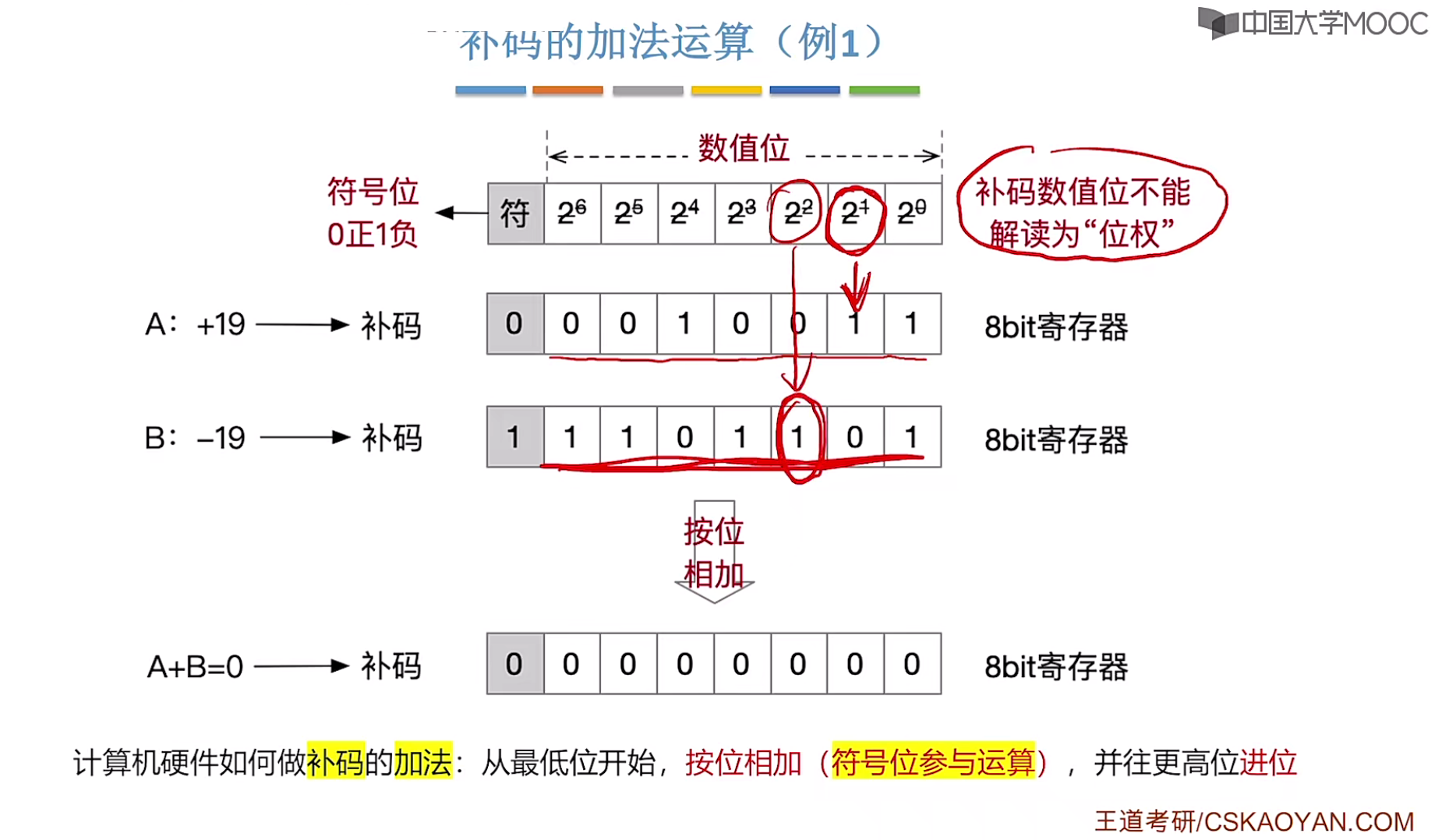

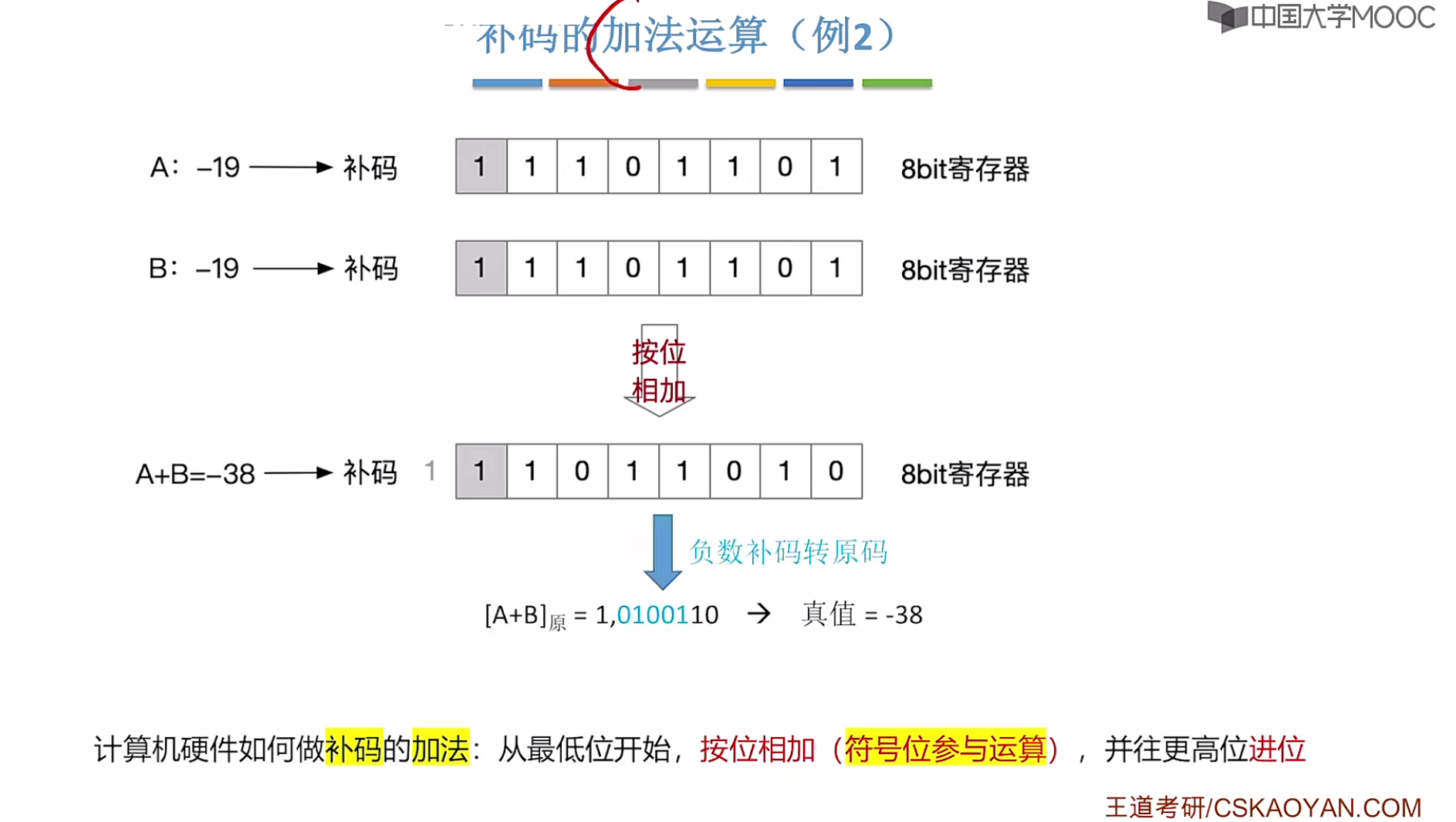

补码的加法运算:加法的规则与之前一样

示例1:正数+负数,最终的补码需要先进行转换为原码后才能得到它的结果值:

示例2:负数+负数

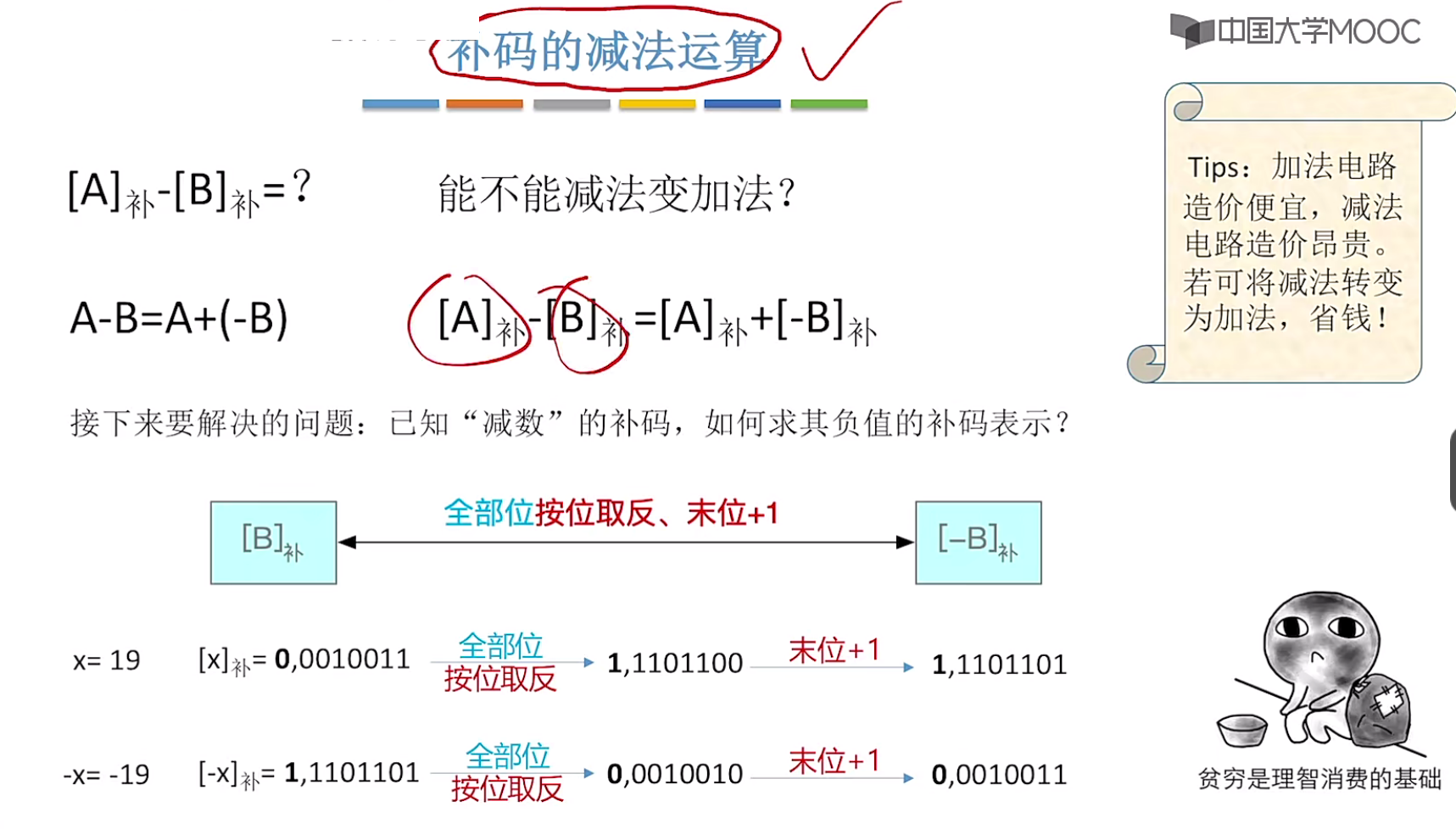

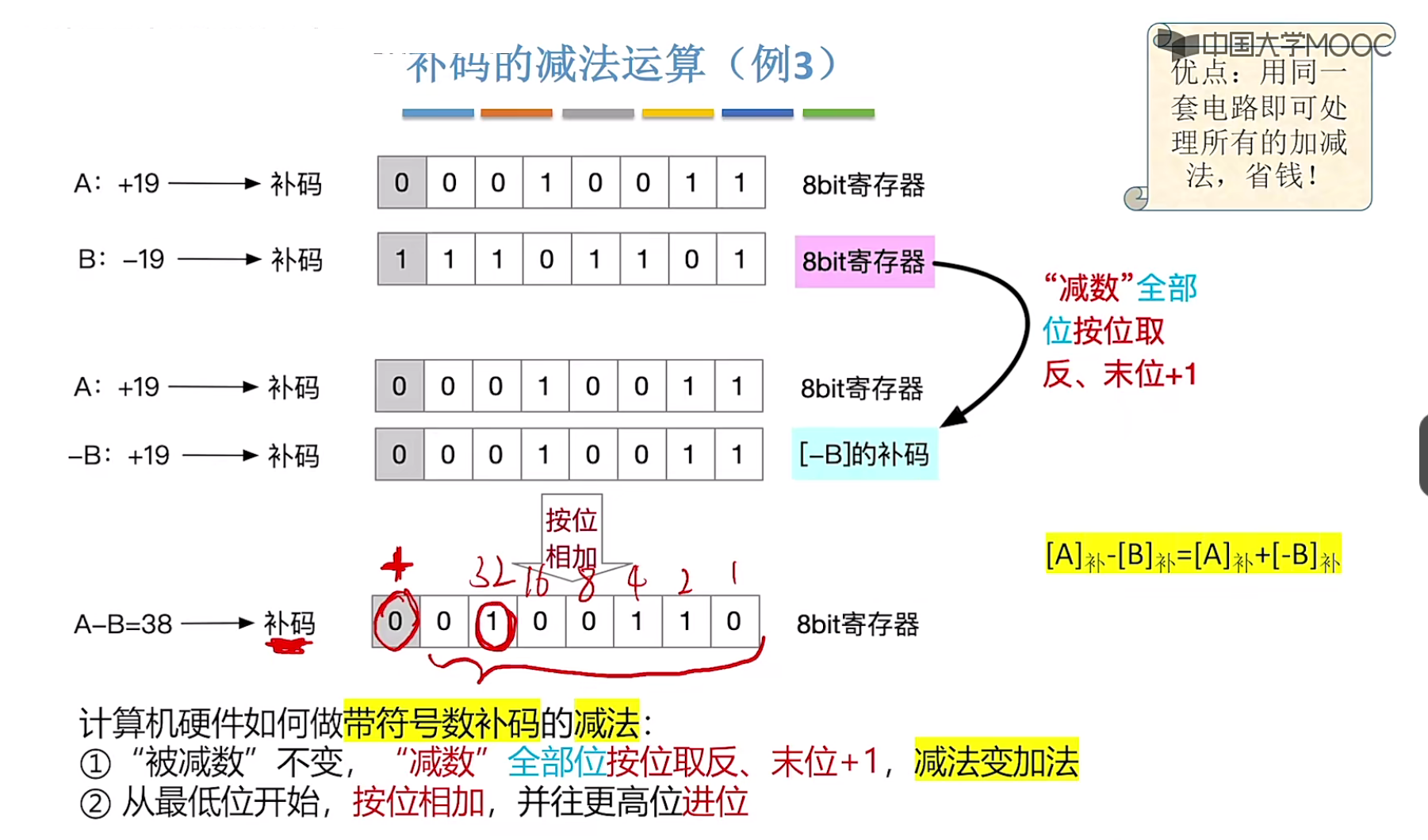

1.4.4、补码的减法运算

补码的减法运算如何实现:一句话原本[A]补 - [B]补 = [A]补 + [-B]补

示例1:

知识点回顾与总结

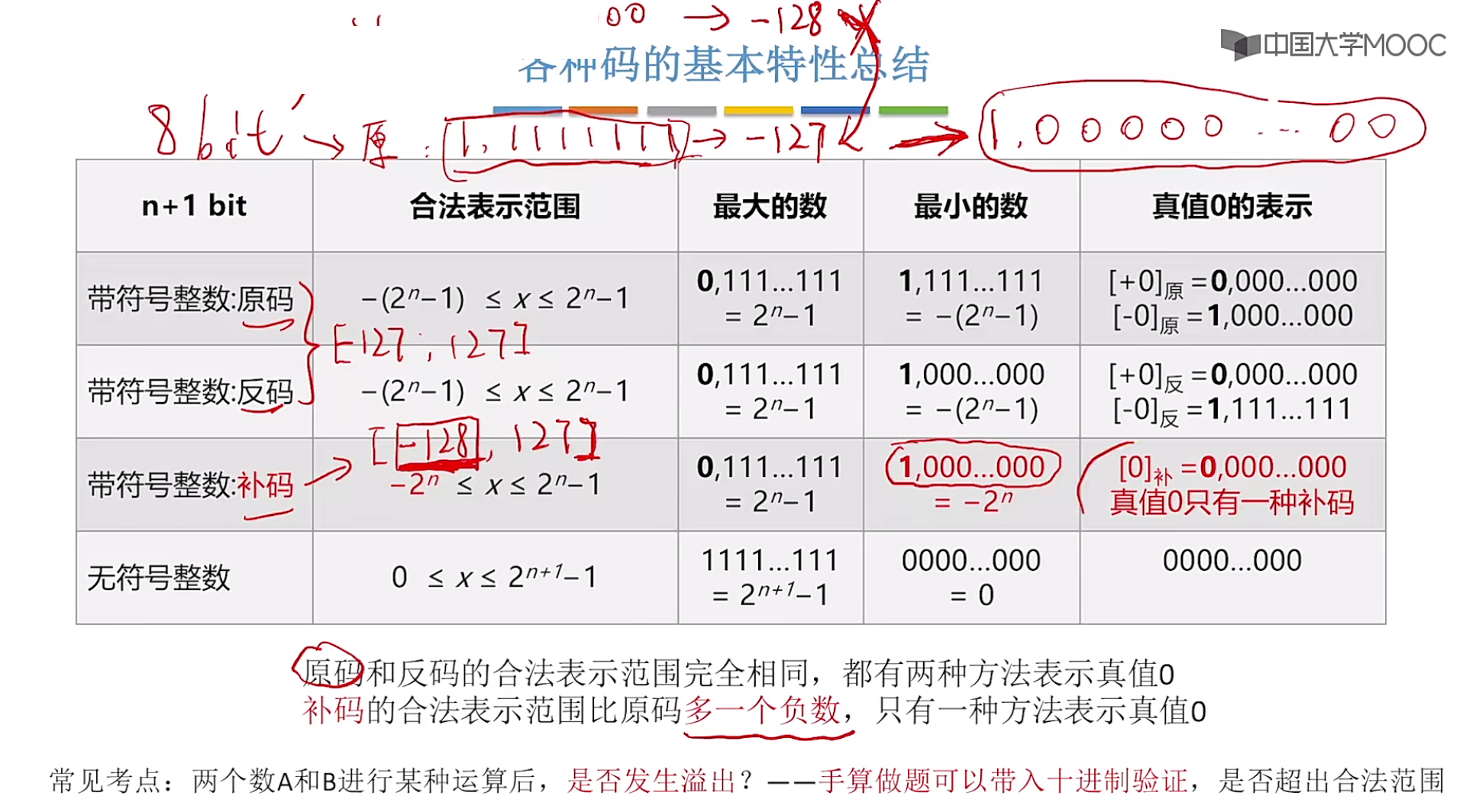

1.5、原/反/补码的特性对比

这里有一个小技巧:对于判断是否溢出,我们可以先手动计算他们的合并值,若是超过了对应码的范围,那么就表示溢出了。

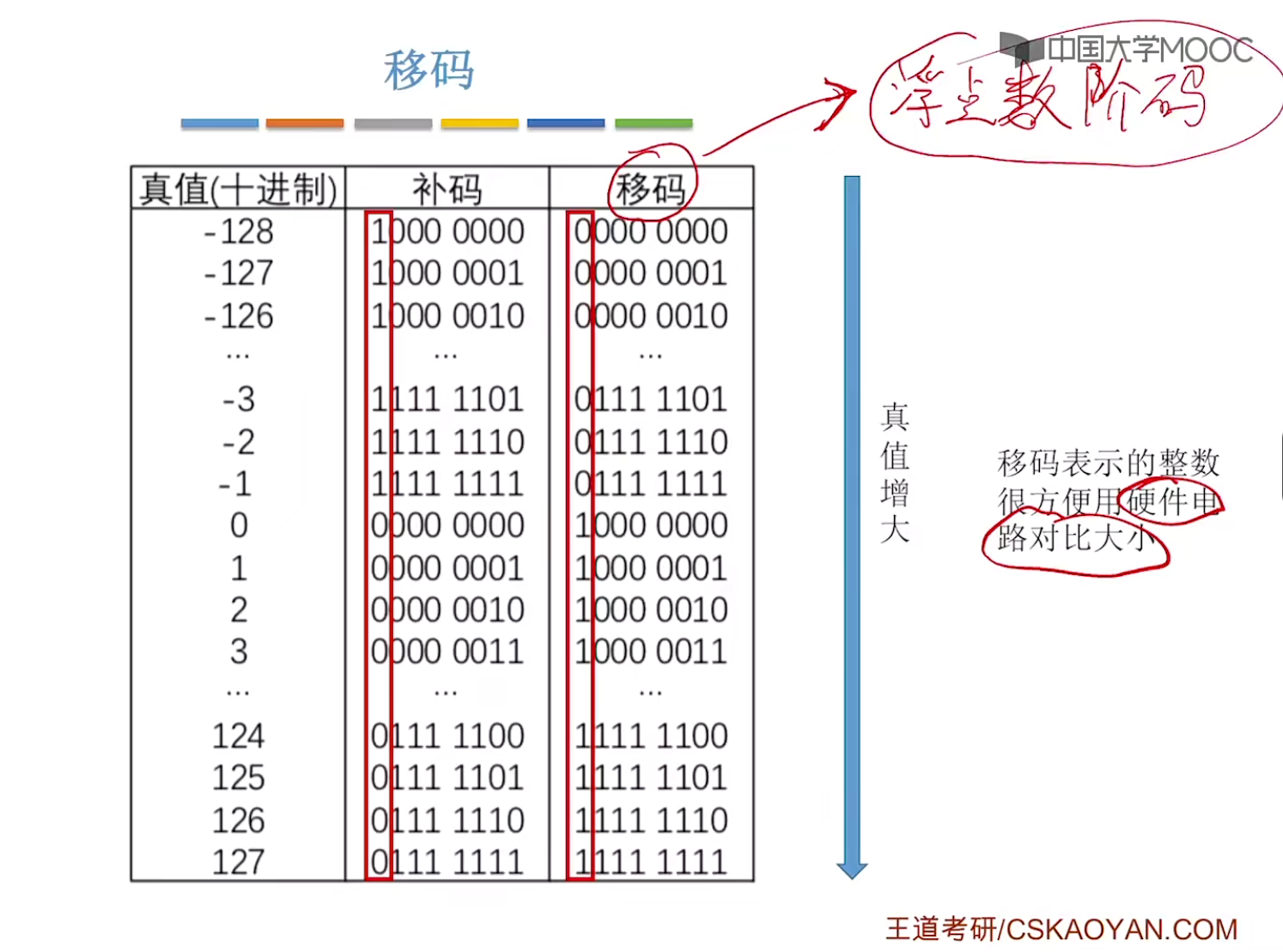

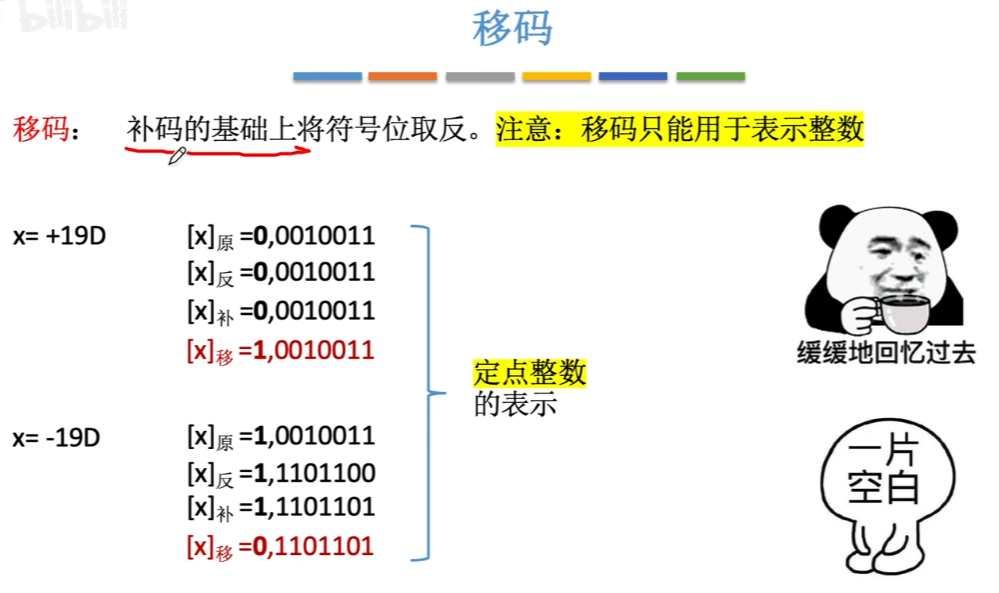

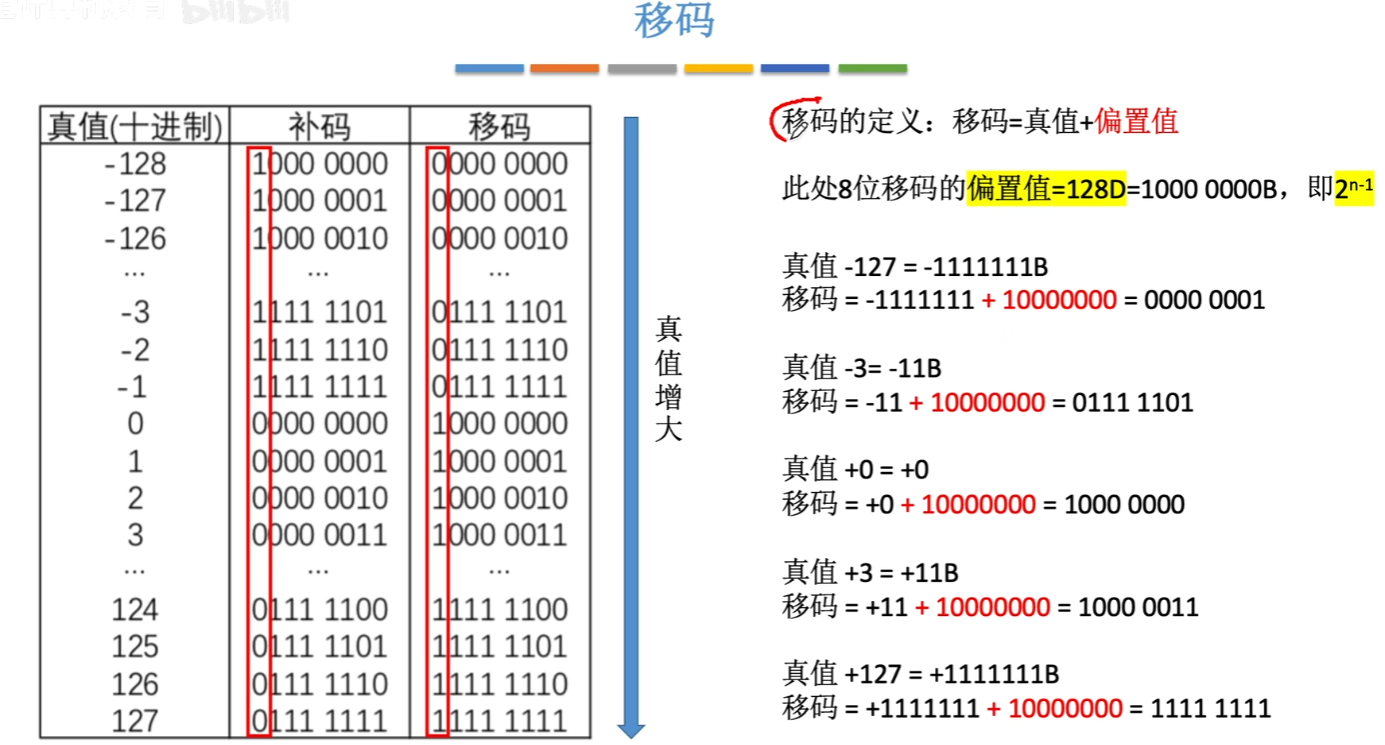

1.6、移码

1.6.1、认识移码

如何得到移码?从补码的基础上符号位取反就可以得到移码。

移码只能够表示整数,无法表示小数,真值0只有一种表示形式,其表示范围与补码一致!

按照无符号整数来解读的话,此时移码刚好位0-255。

移码应用:一般用于浮点数的阶码。

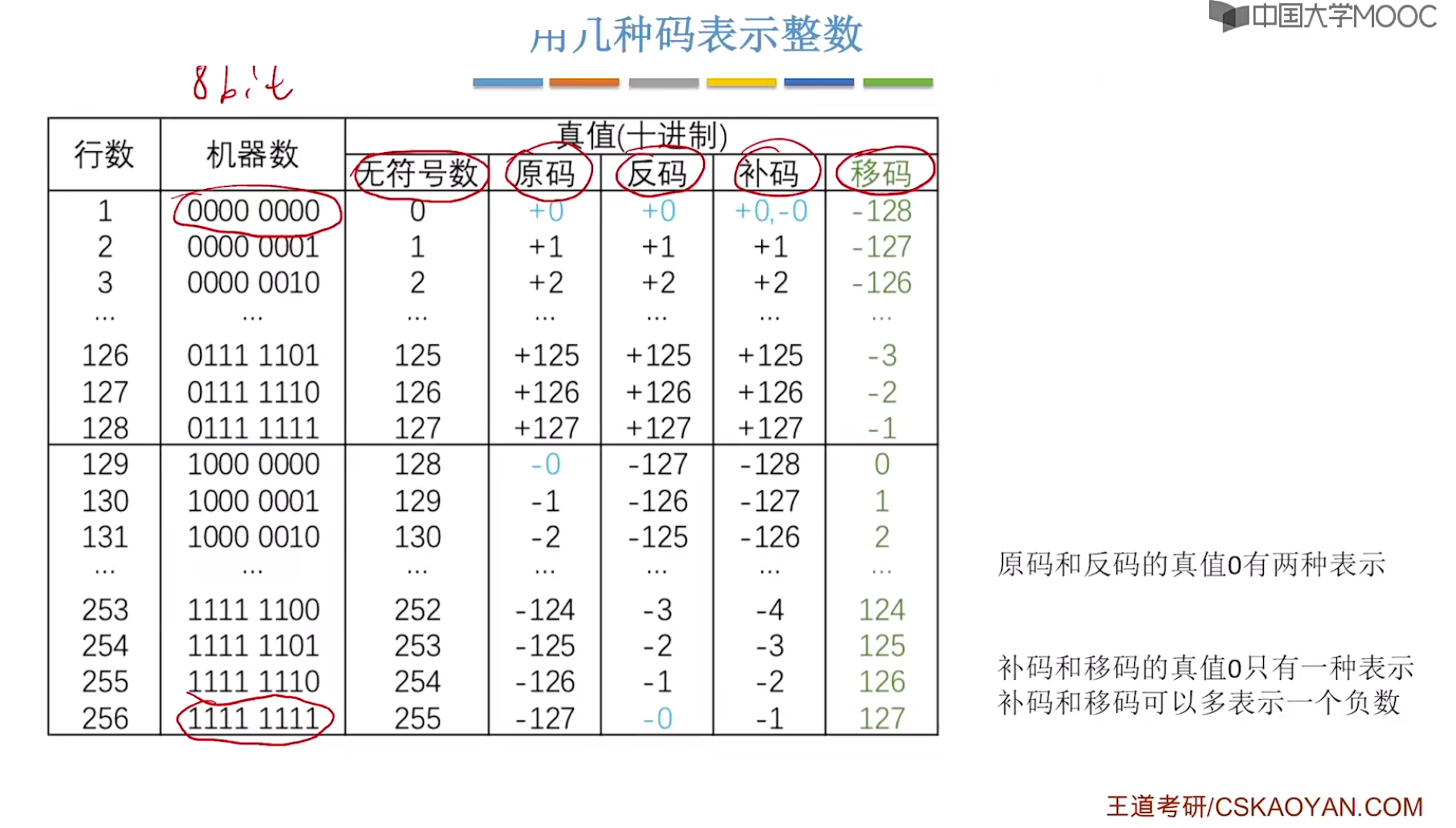

1.6.2、用几种码表示整数(新增移码部分)

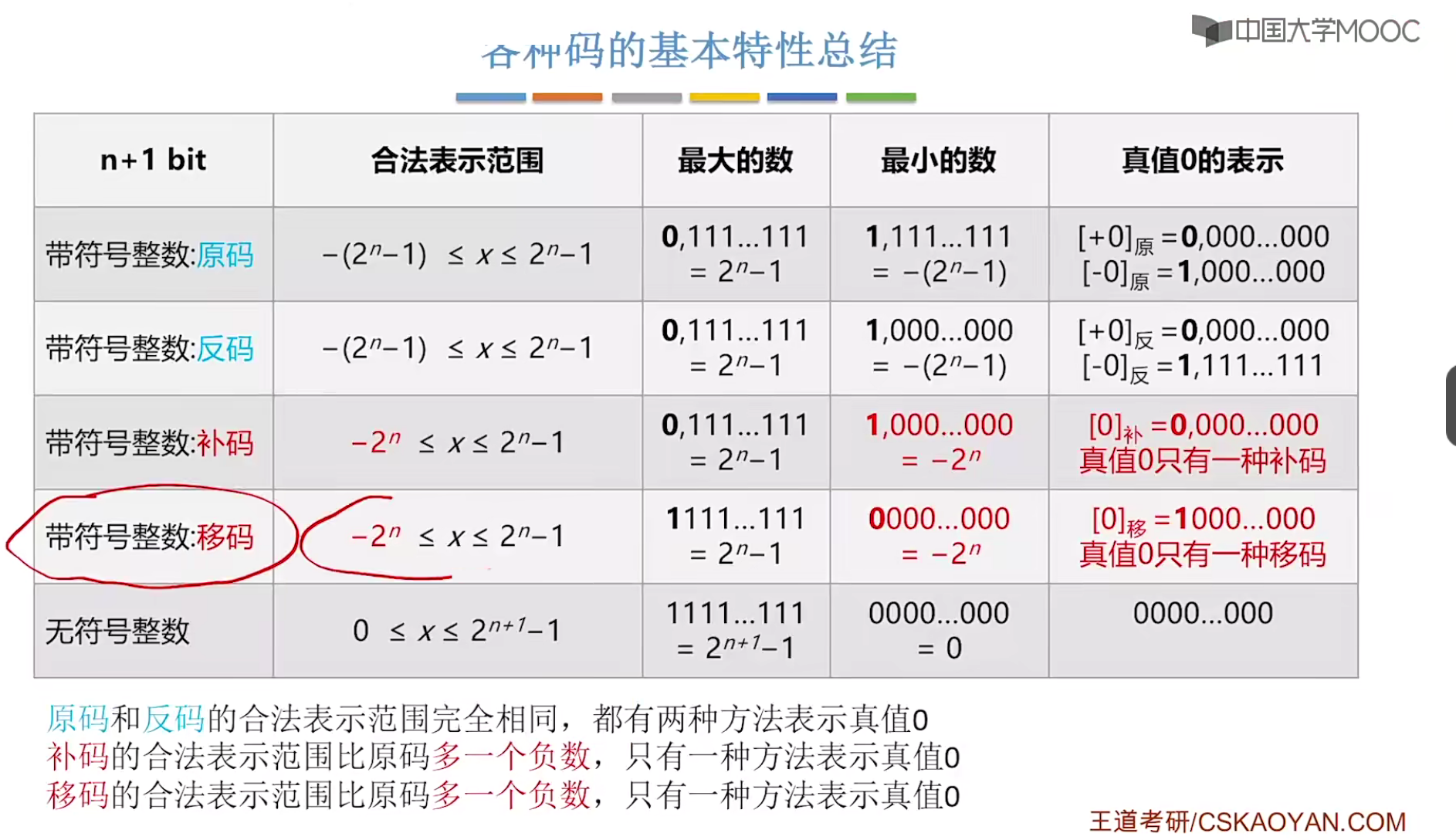

1.6.3、各种码的基本特性总结(包含移码)

各种码的对比包含移码:

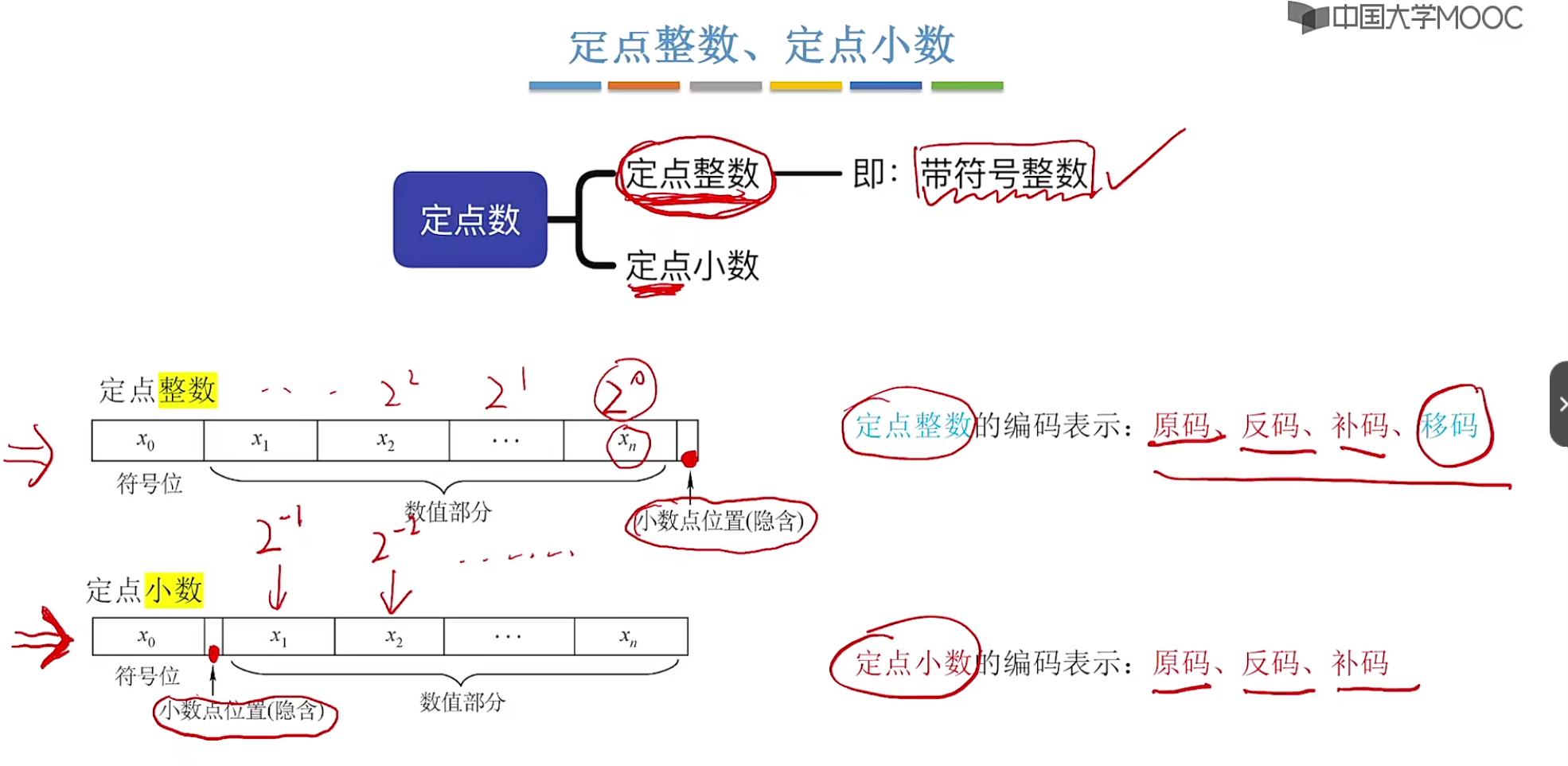

1.7、定点整数(带符号整数)、小数

1.7.1、定点小数的表示(包含原、反、补)

带符号整数默认称为定点整数,默认是定在最后一个位置。

定点整数:小数点位置在最后末尾。

- 编码包含:原码、反码、补码、移码。

定点小数:小数点位置在符号位后一位。

- 编码包含:原、反、补码。

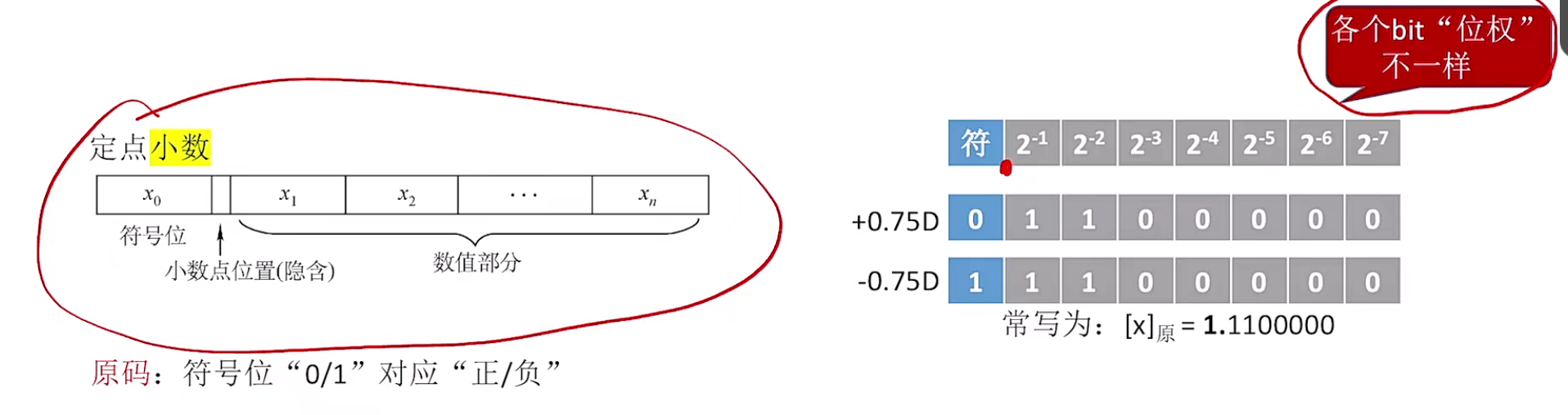

定点小数的原码表示:根据小数点的位置来确定位权。

关于定点小数的反码与补码:与定点整数一模一样

1.7.2、定点小数的加减法运算

定点小数的加减法运算:与定点整数一模一样

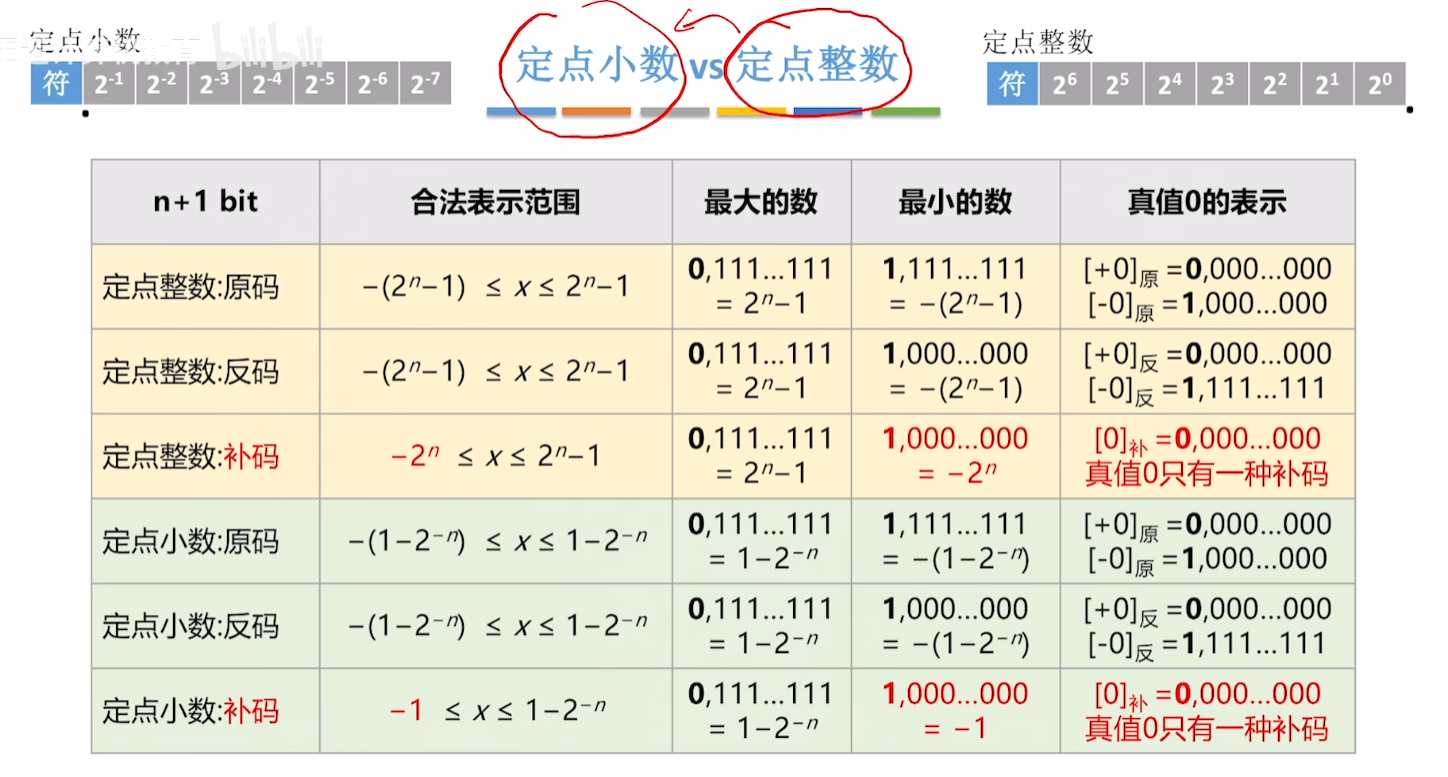

1.7.3、定点整数与定点小数的对比(合法范围、位数扩展位置)

合法范围:

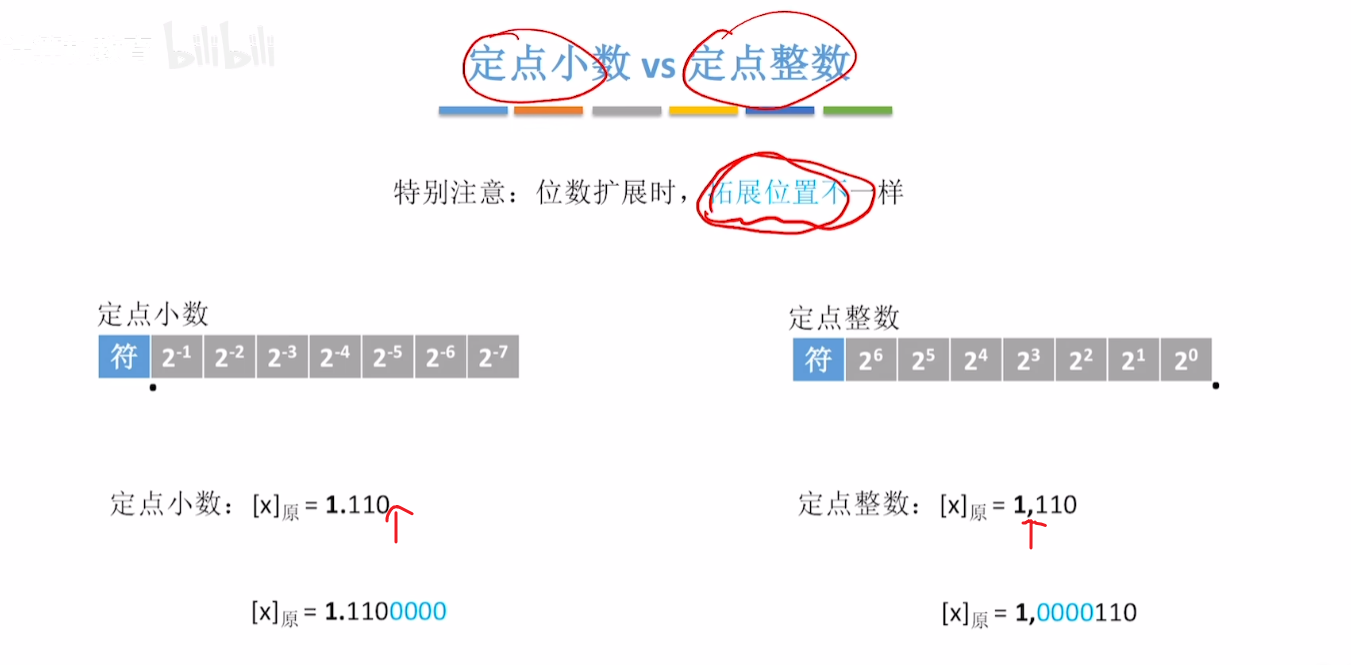

位数扩展位置不一样:小数直接扩展到末尾,整数扩展到符号位

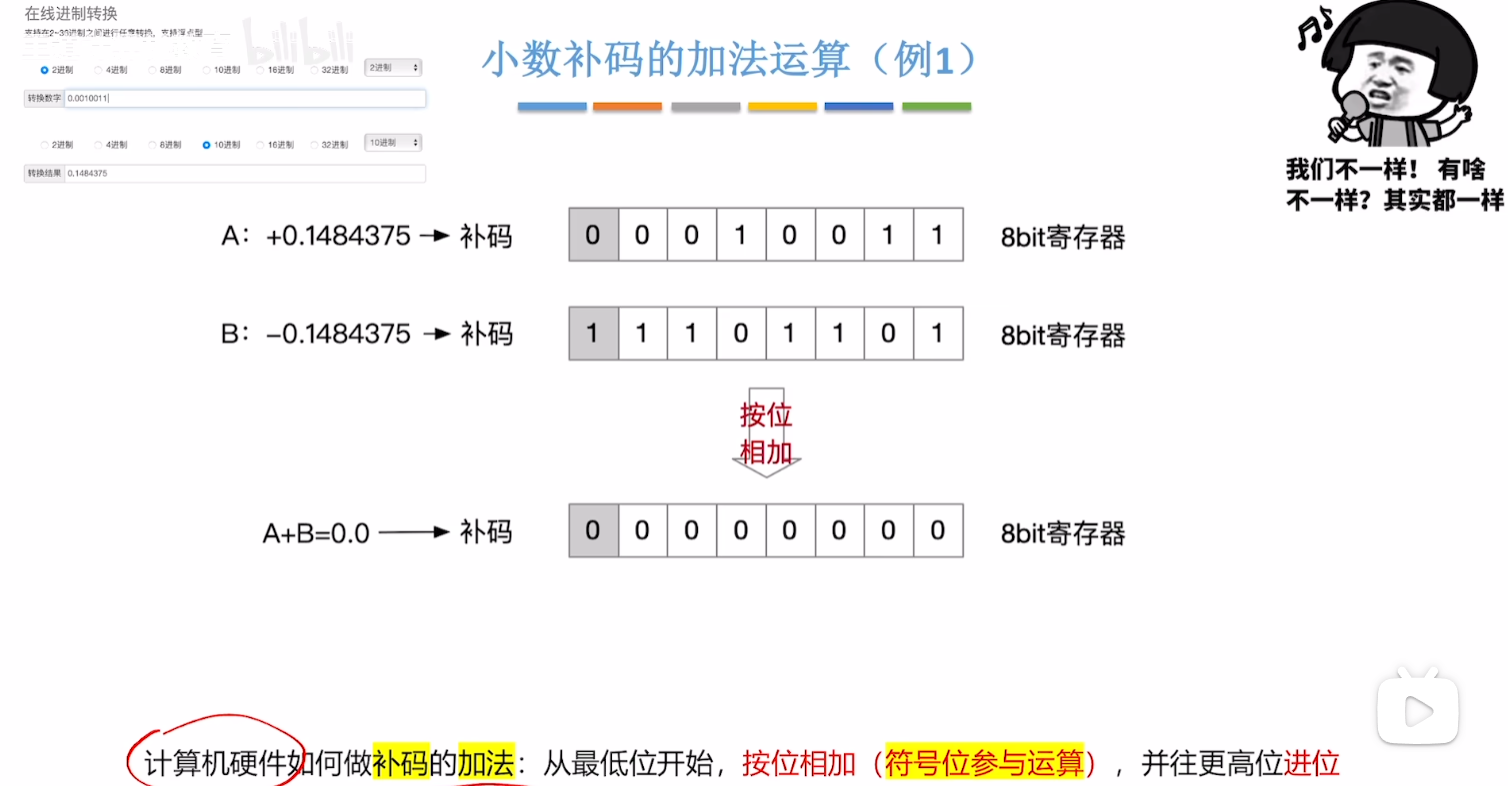

1.7.4、小数补码的加减法运算

加法运算

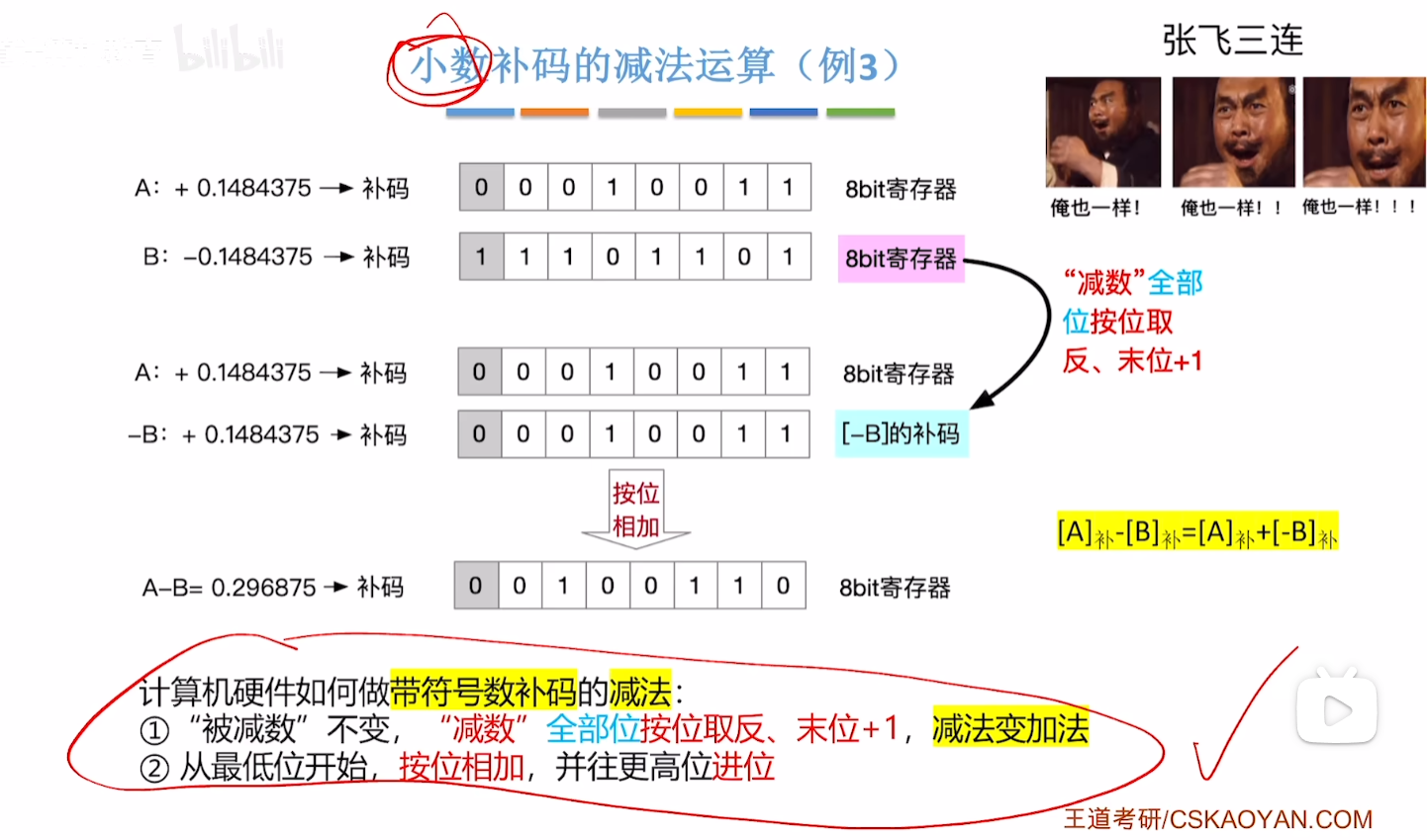

减法运算

小数补码的减法运算:与之前的整数一致

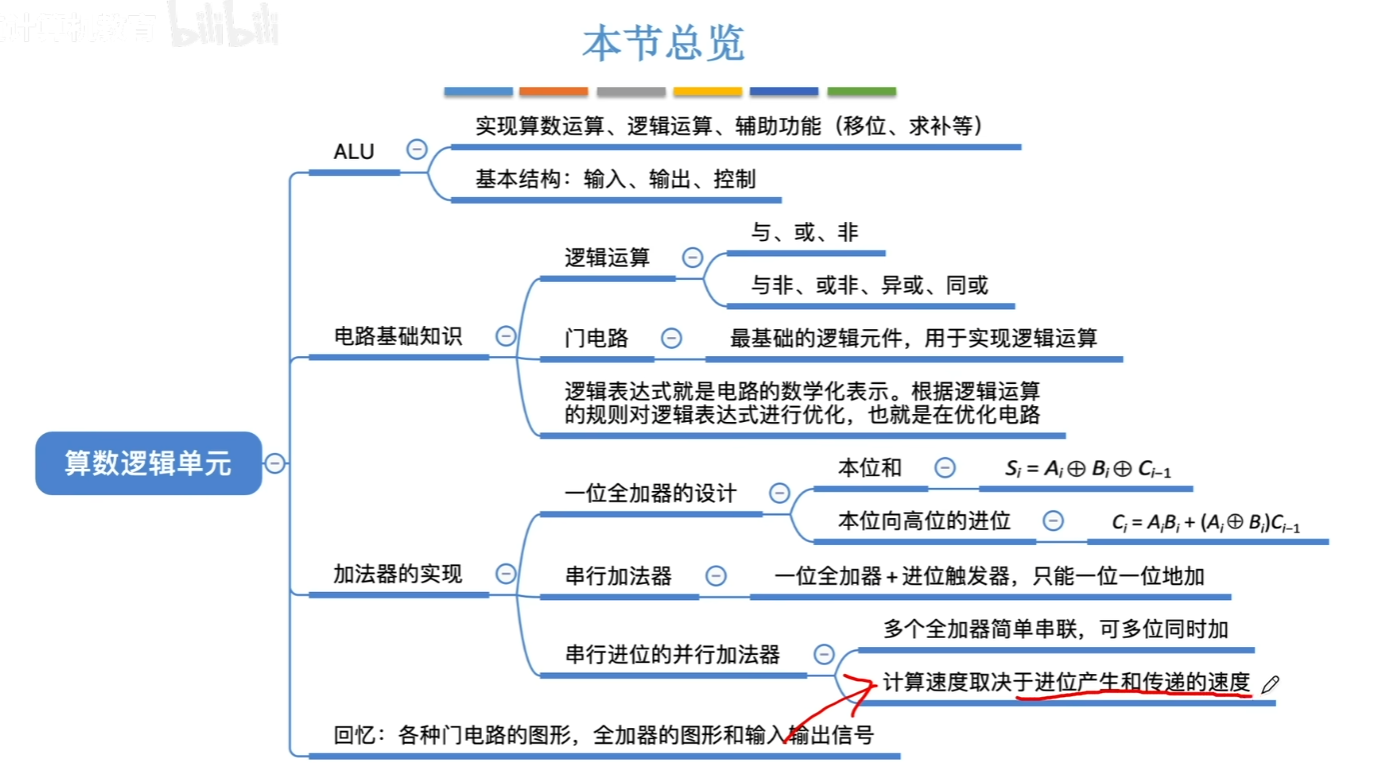

二、运算方法和运算电路

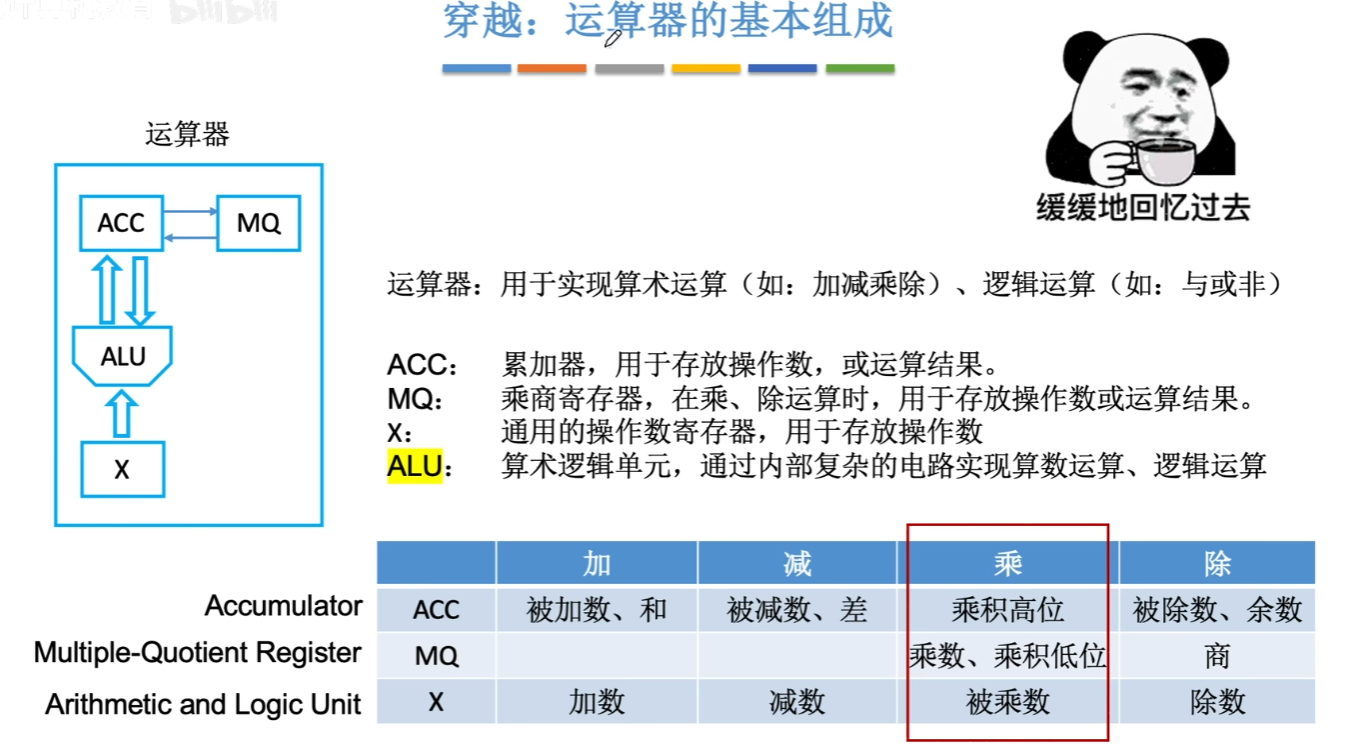

2.1、基本运算部件

如何使用硬件实现加法是一个重要探讨的问题!

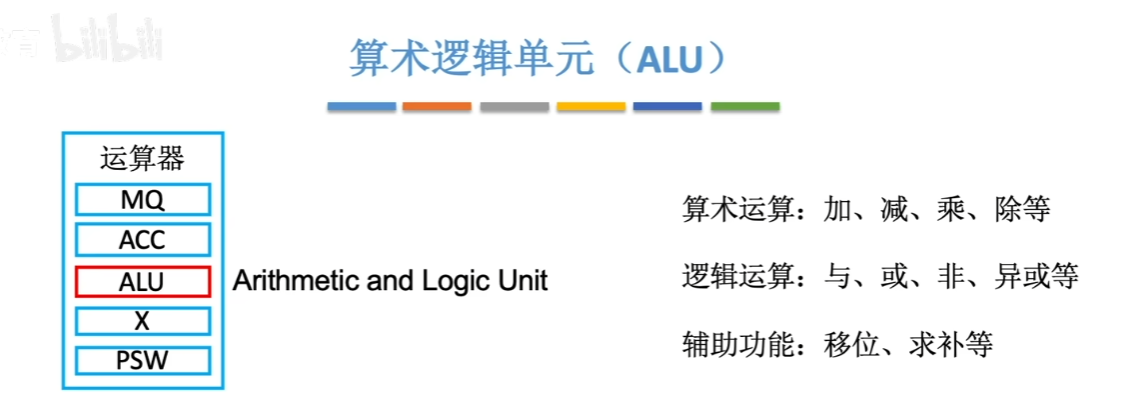

2.1.1、认识ALU算数逻辑单元(包含部件及ALU实例)

算数逻辑运算单元:

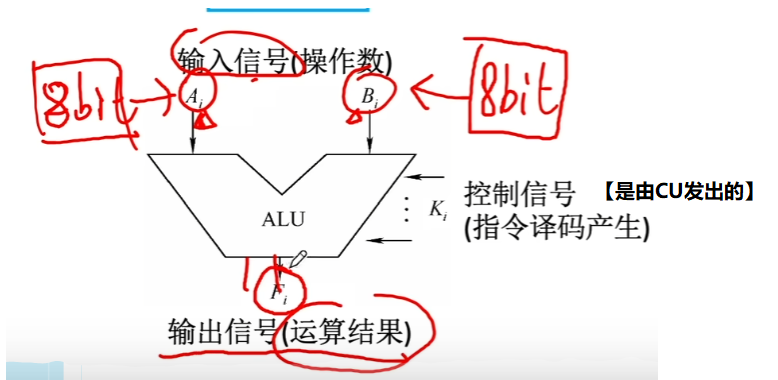

ALU控制信号部件:

- 其中Ai、Bi表示的输入信号,对应的Fi即为输出信号。

- 其中控制单元负责解析指令的含义,一条指令是加法、减法还是其他逻辑运算的指令,CU解析完指令之后会发出一些控制信号,每一个信号就是高低电平。

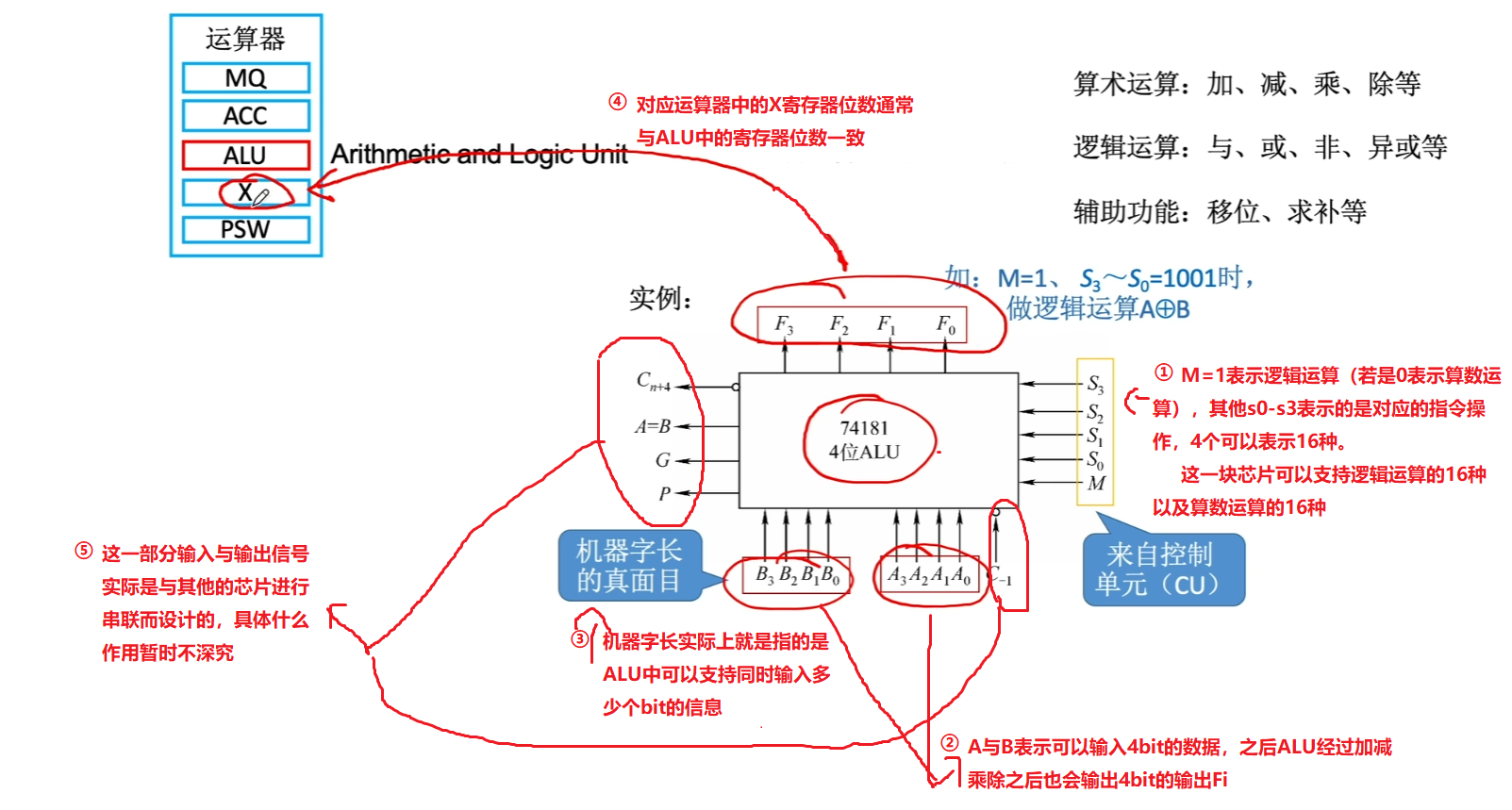

下面是ALU的实例:74181的4位ALU

①M=1表示逻辑运算(若是0表示算数运算),其他s0-s3表示的是对应的指令操作,4个可以表示16种。

- 这一块芯片可以支持逻辑运算的16种以及算数运算的16种。

②A与B表示可以输入4bit的数据,之后ALU经过加减乘除之后也会输出4bit的输出Fi。

③机器字长实际上就是指的是ALU中可以支持同时输入多少个bit的信息(本质)。

④对应运算器中的X寄存器位数通常与ALU中的寄存器位数一致。

⑤这一部分输入与输出信号实际是与其他的芯片进行串联而设计的,具体什么作用暂时不深究。

2.1.2、电路基础知识

2.1.2.1、逻辑运算

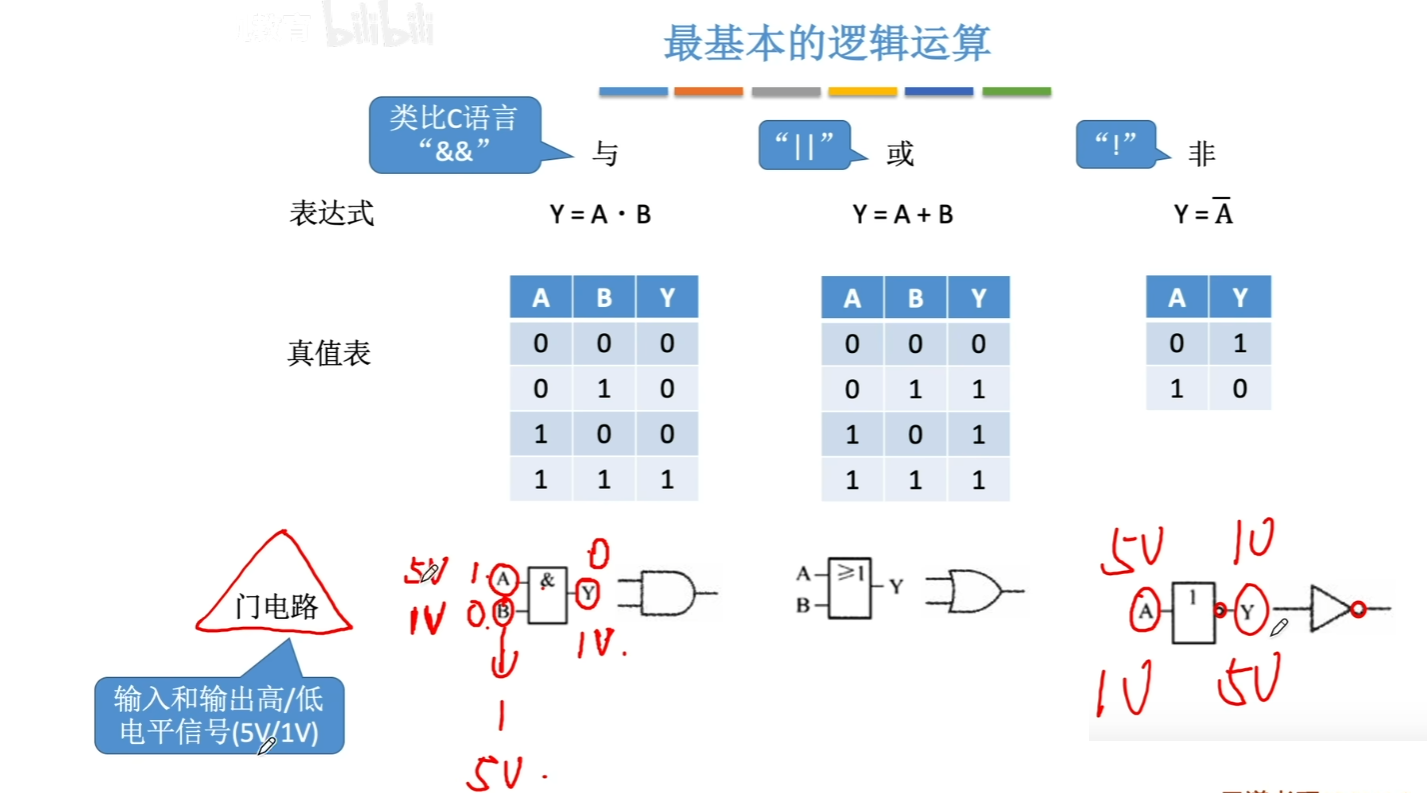

最基本的逻辑运算:无论在复杂的算数运算、逻辑运算都是通过最基本的逻辑运算实现的(1个bit位实现)

- 通过使用门电路来实现的逻辑运算(本质上就是高低电平)

通过不同的结合律我们可以使用不同数量的电路元器件来实现:

- 若是与逻辑与或逻辑同时出现,那么根据优先级来决定谁先执行。

- 可以看到左边的A(C+D)只需要使用两个元器件,而右边的AC+AD则需要三个元器件,那么通过这个例子实际就可以很明显的看出通过简化逻辑表达式可以减少电器元件的使用,从而实现节约开销。

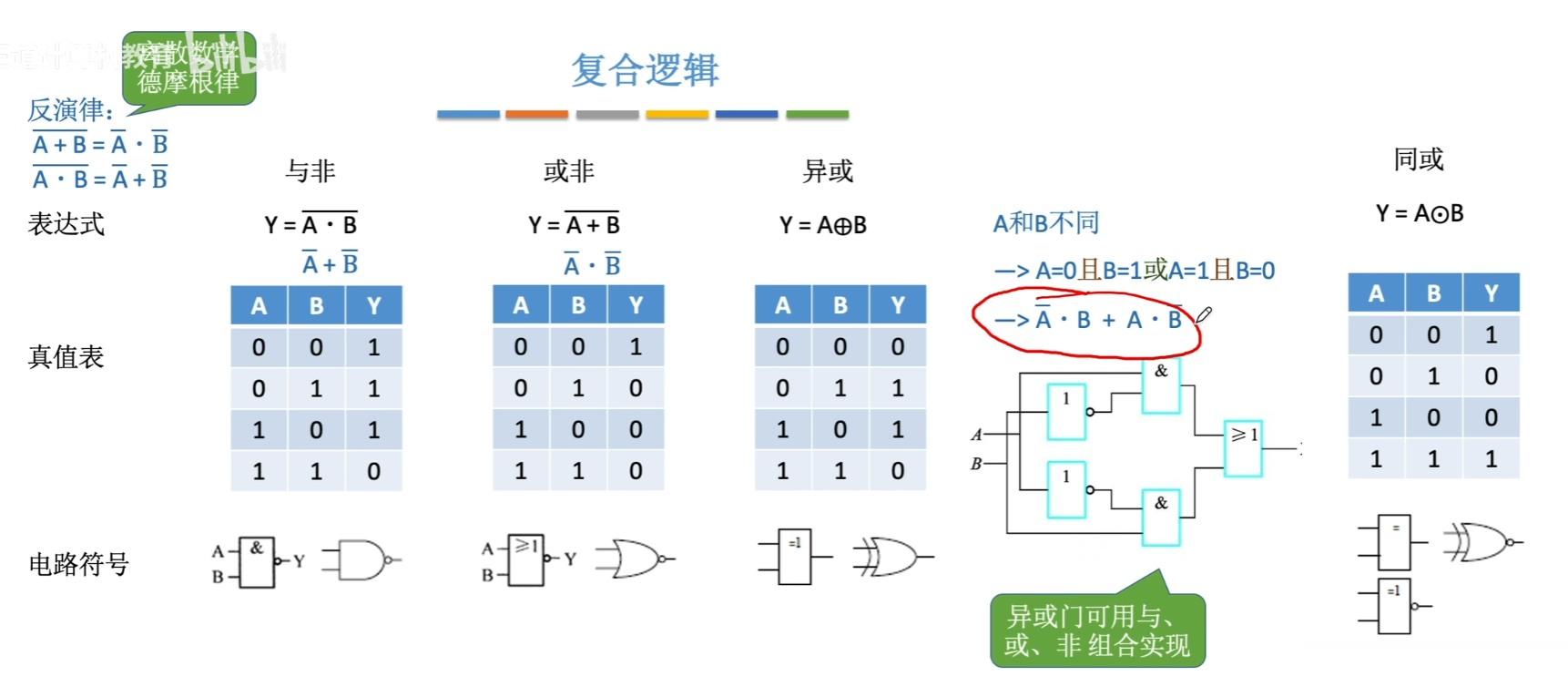

2.1.2.2、复合逻辑运算

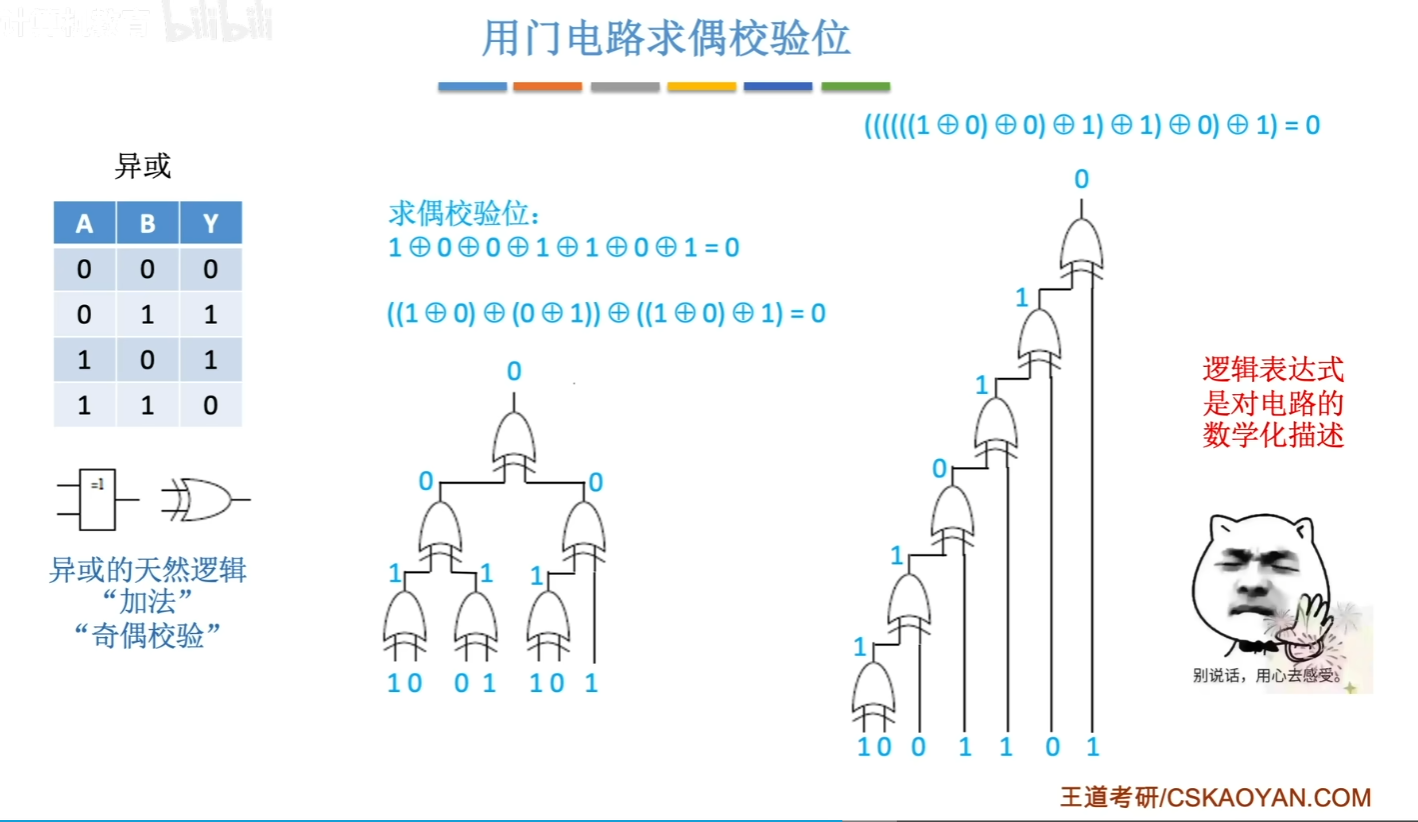

其中异或天然逻辑可以实现加法、奇偶校验。

2.1.3、异或门电路实际应用

2.1.3.1、门电路实现偶校验位例子

偶检验:1的数量有偶数个

- 对偶数个1进行异或结果为0。对奇数个1进行异或最终异或结果为1。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-tzIYRMi3-1685321272458)(C:\Users\93997\AppData\Roaming\Typora\typora-user-images\image-20230524115445312.png)]

如何用电路来实现?门电路来求偶校验位例子。

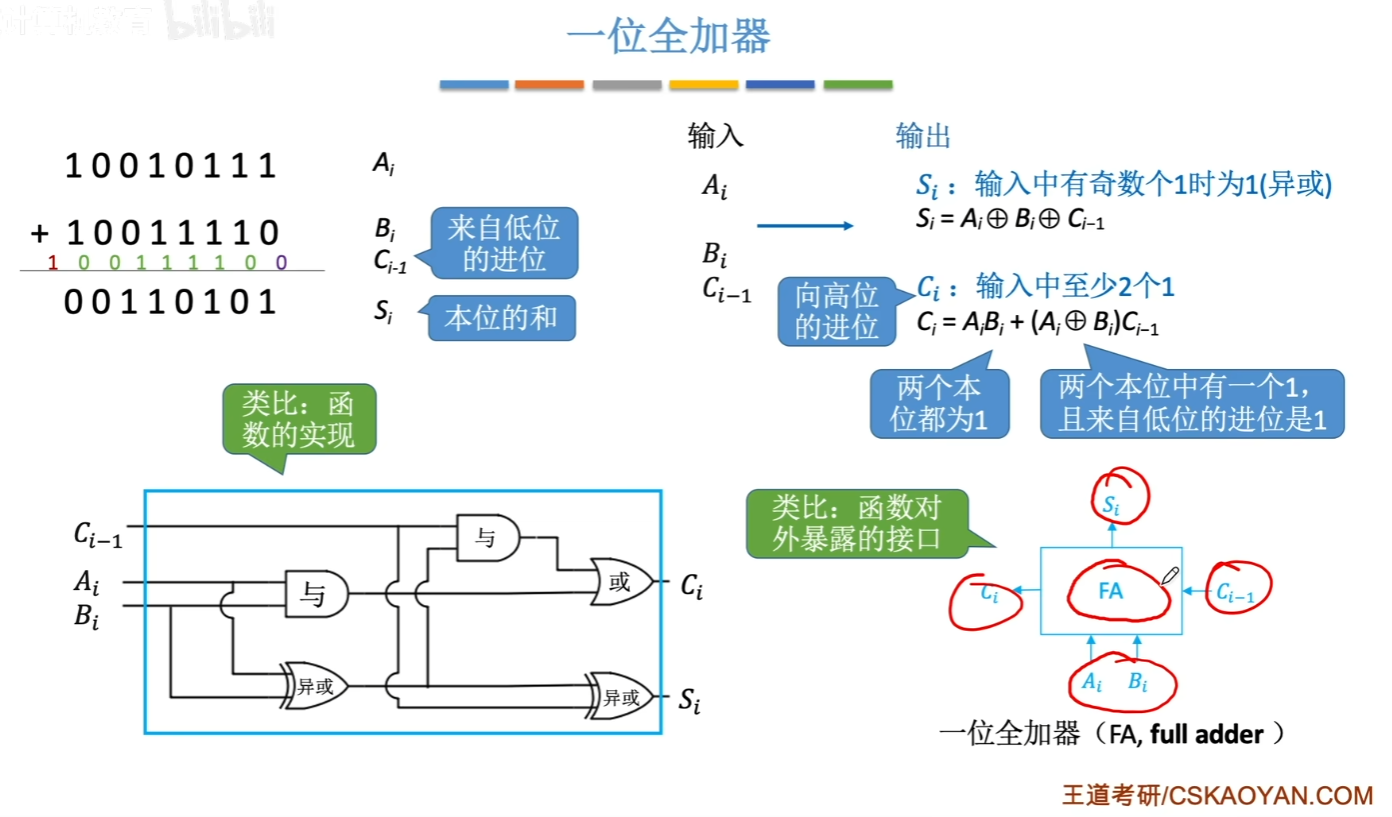

2.1.3.2、异或门实现加法运算(一位全加器)

异或门如何实现加法运算?一位全加器。

通过输入的Ai、Bi以及来自低位的进位Ci-1来去输出得到Si、Ci,这个过程我们是可以使用异或来实现的。

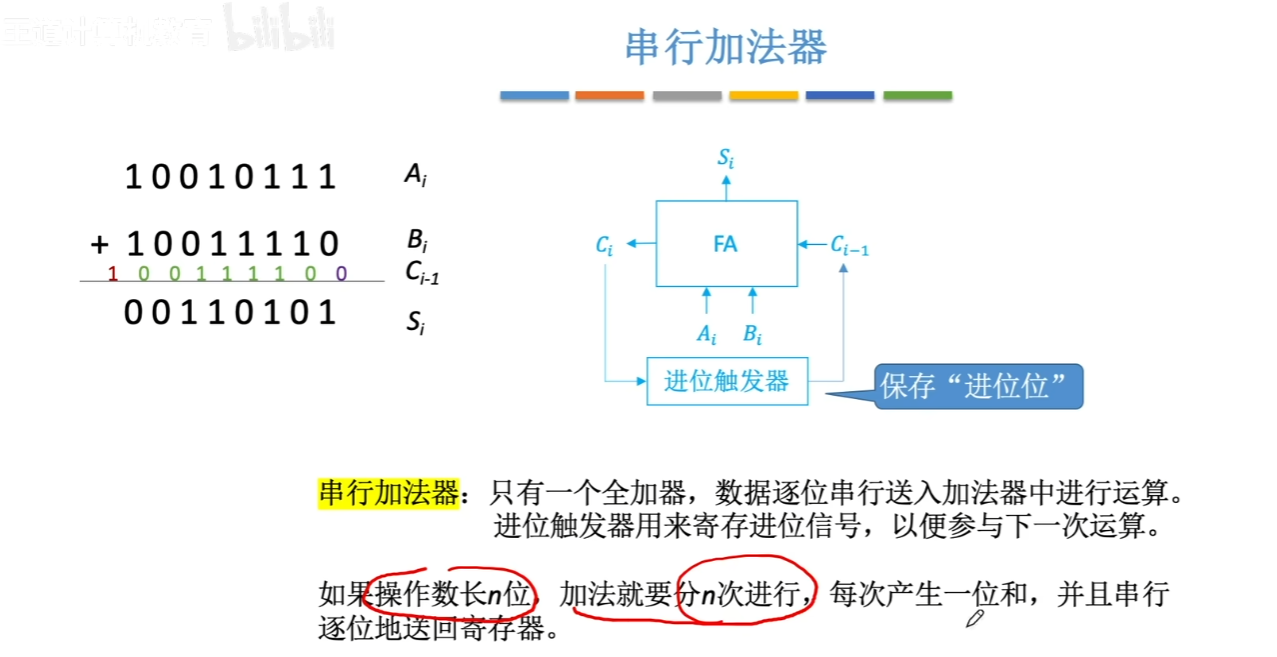

2.1.3.3、通过一位全加器来实现多位的加法(串行加法器、并行加法器)

第一种:串行加法器

实现过程:输入Ai与Bi接着读取到上次的进位值,进行一位加法器运算,得到的Ci进位值会保存到进位触发器中,之后再次进行一位加法器的时候就可以读取进行运算。

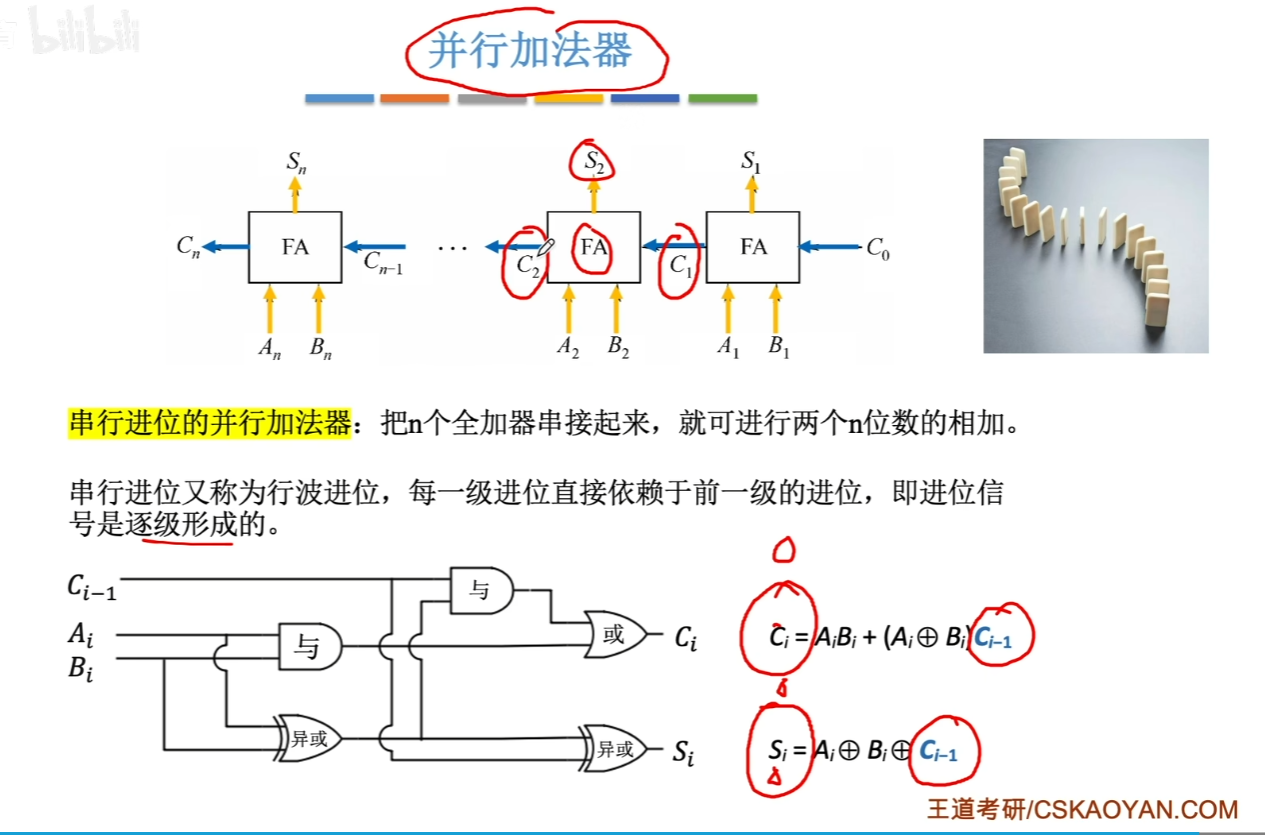

第二种:并行加法器

只有低位的算出来了,高位的才可以去进行计算:

运算速度取决于前一个进位的产生速度。

知识点回顾与总结

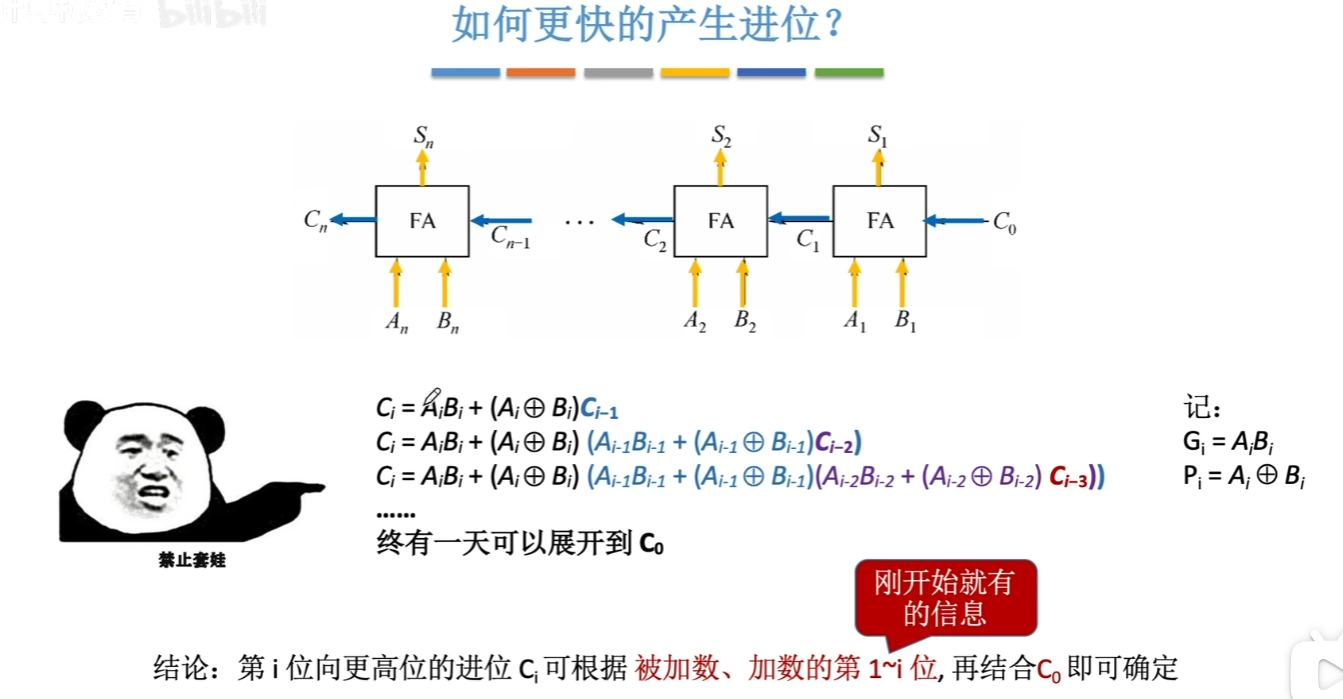

2.2、深入理解并行加法器的优化(实现并行的突破点)

基于之前的一位加法器,此时要探讨的问题是,如何更快的产生进位?、

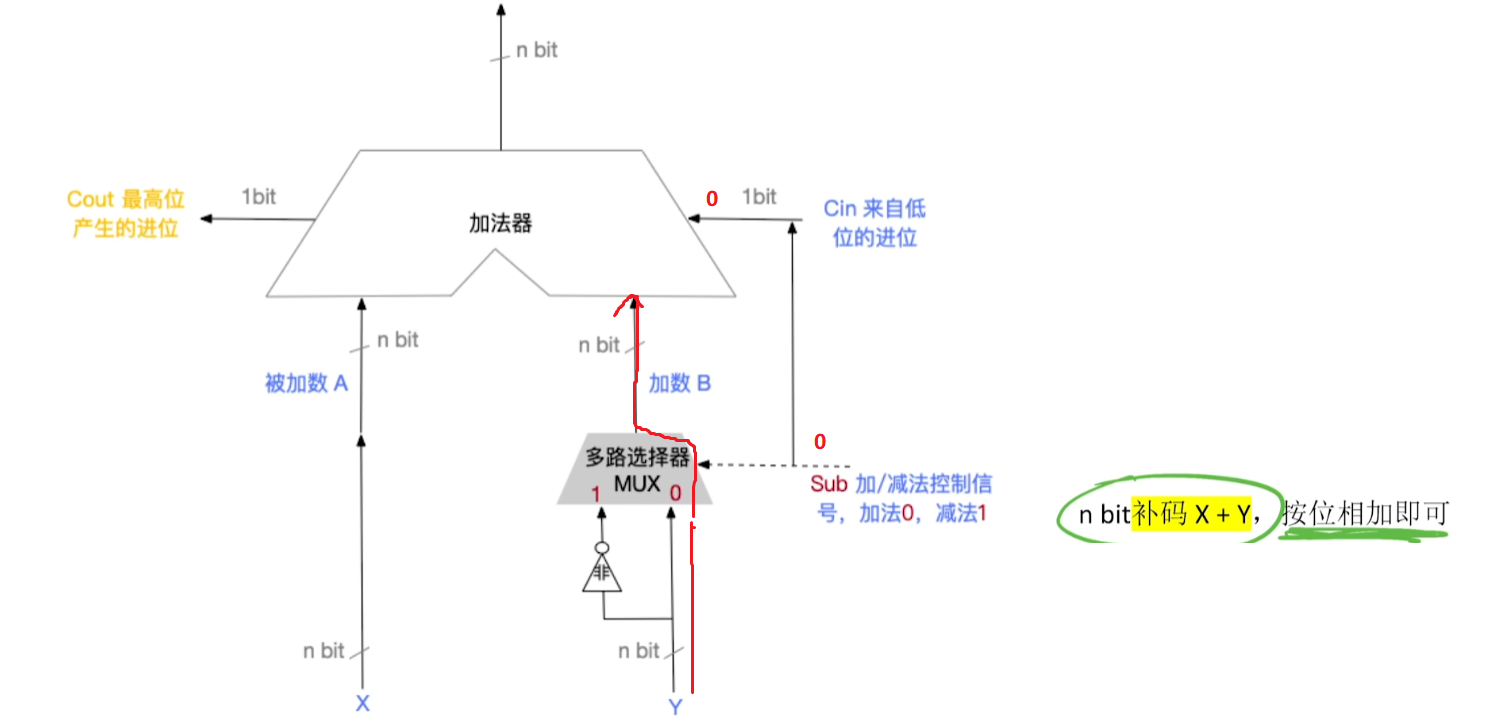

原本计算Ci的式子展开可以见下图,每一个Ci都会依赖上一个Ci-1,那么我们是否能够通过一些方式在计算每一个Ci的时候无需使用上一个Ci呢?

- 这就涉及到并行加法器的优化了,我们让Gi = AiBi,Pi = Ai 异或 Bi。

接着重新带入到Ci的式子当中去,举个例子,我们将C1=G1+P1C0代入到C2当中去,可以看到C2的式子:

我们可以惊奇的发现此时C2中仅仅依赖的只是最原始的C0,按照这样的方法同样带入到其他的Ci当中去呢?同样每一个新的Ci都仅仅只依赖于最原始的C0,这样子有什么好处?

- 我们这样设想,对于计算Ci我们可以不再依赖之前的串行顺序,而是可以通过并行来进行同时计算多个Ci,直到最后计算完成所有的Ci之后,此时统一再进行处理。

最终构成就是上图的4位CLA加法器,其中多是由FA和一些新的线路、运算逻辑组成。

所以并行加法器的优化我们可以总结一下:原本Ci在没有进行式子完全展示开始时貌似是依赖于上一个也就是Ci-1,实际我们进行展开后实际每个Ci仅仅只是依赖于C0,那么对于Ci的计算无需按照串行顺序,可以使用并行技术来进行计算,直至所有的Ci计算完成后统一进行计算处理。

2.3、补码加减运算器

2.3.1、加法器原理

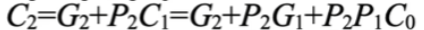

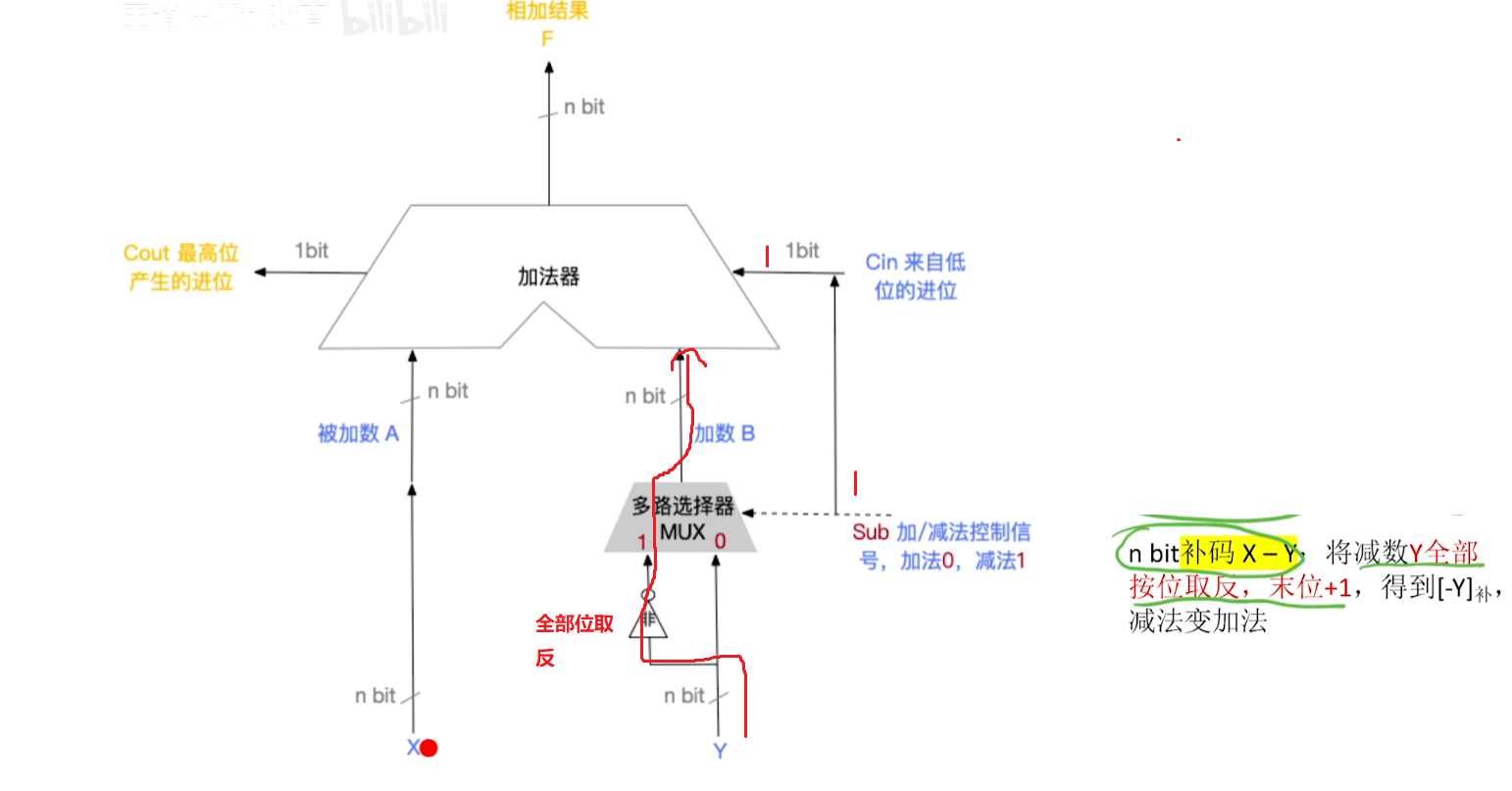

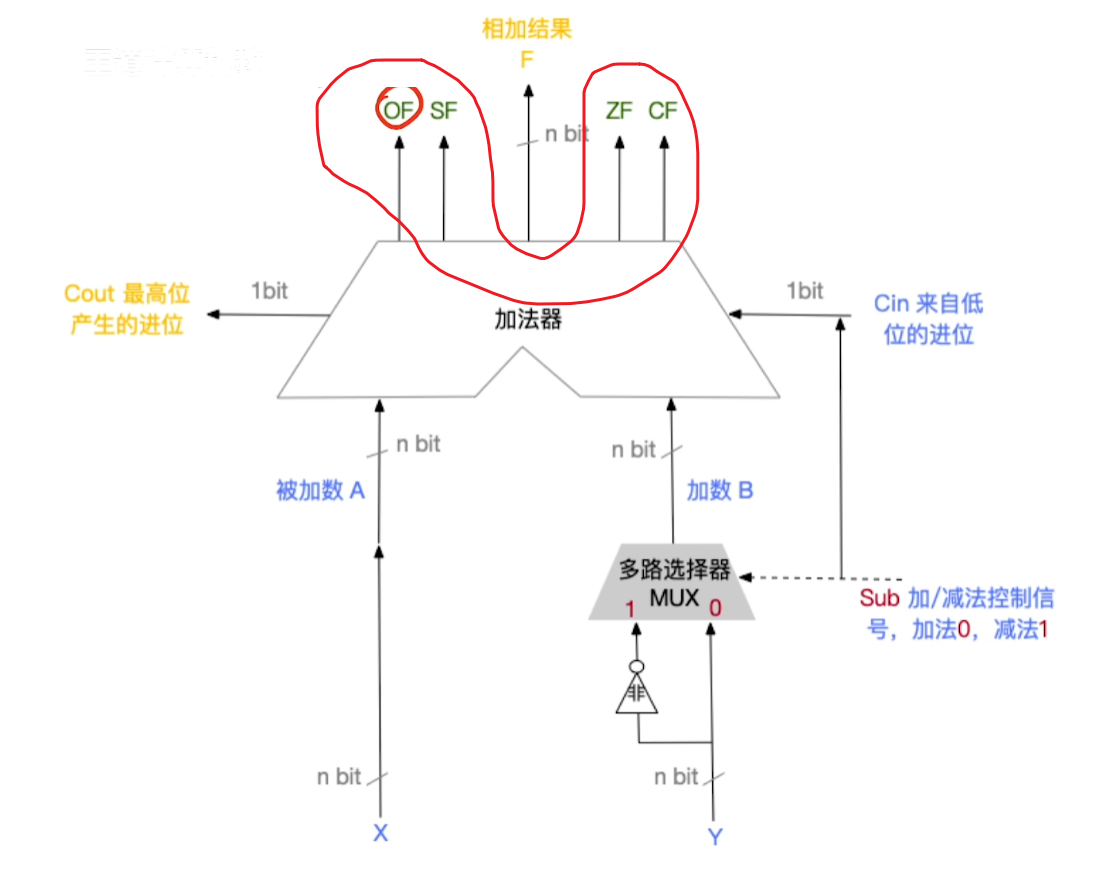

加法器主要包含下边的两个输入端被加数A与被加数B,右边是低位的进位,左边是最高位的进位,上边则是相加的结果:

2.3.2、补码加减运算硬件电路实现

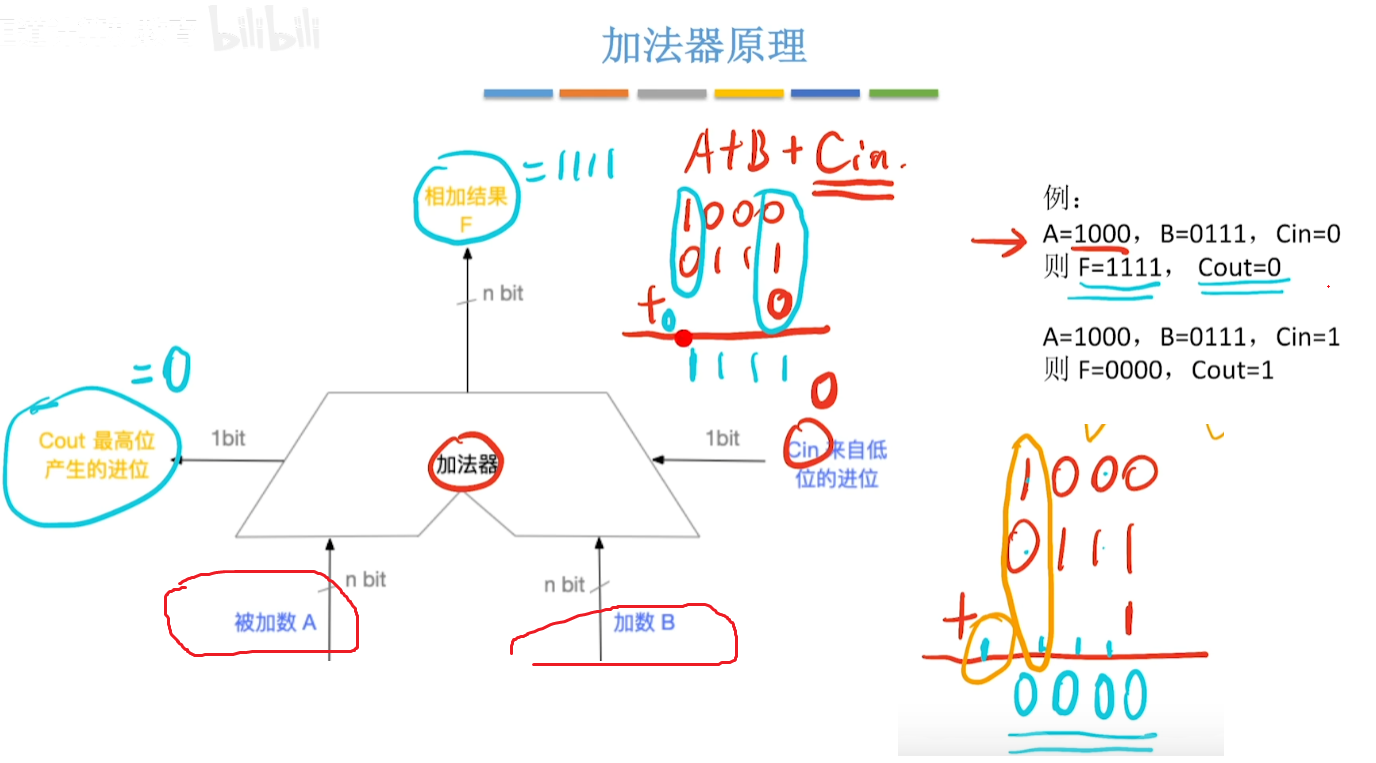

①补码加减运算的手算方式

下面例1:计算X-Y得到的结果为-15,实际上已经小于最小的值了,溢出了

②补码加减法运算硬件实现(溢出问题需要由标志位来决定)

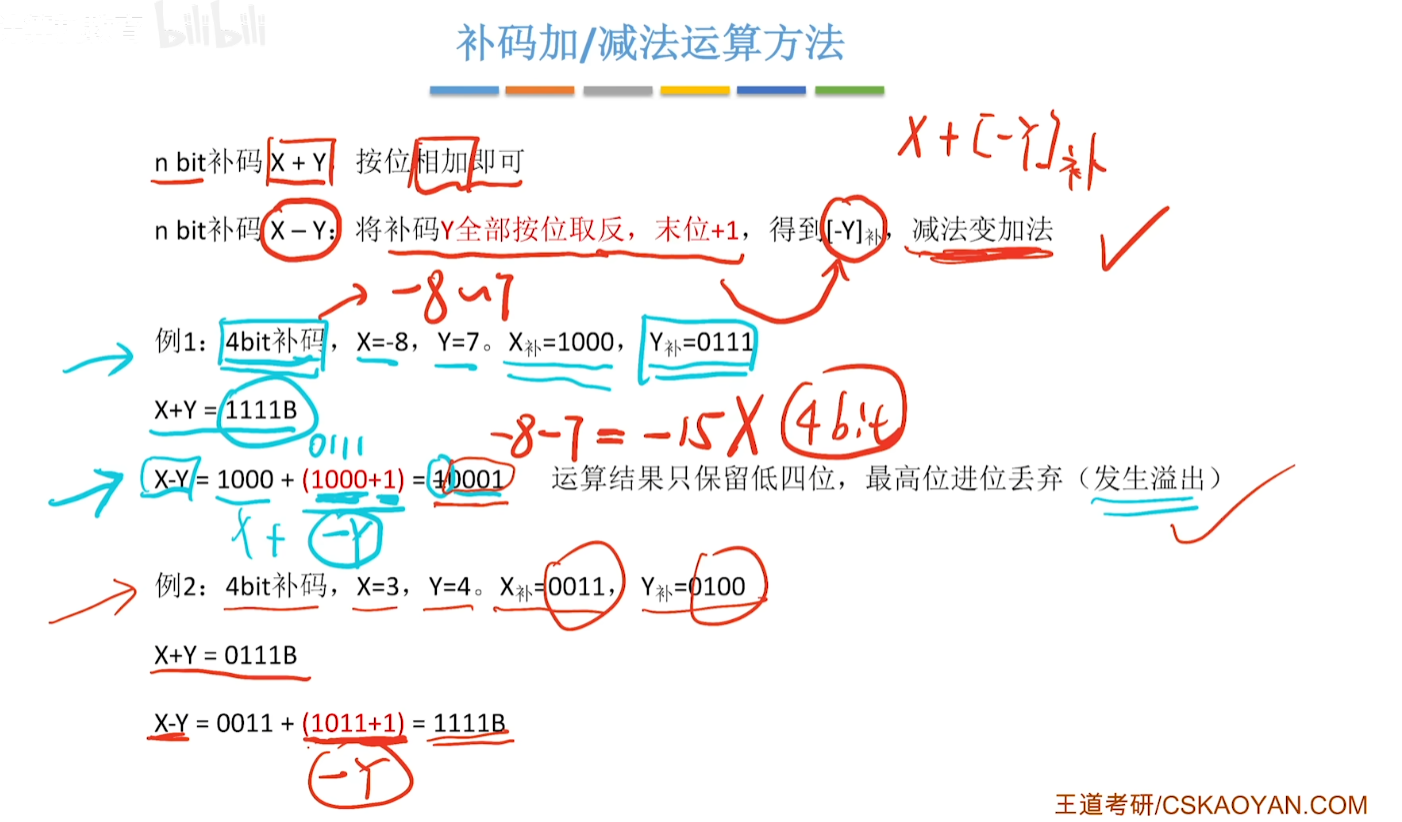

硬件实现思路(无标志位)

对于下方的加法器不仅仅对补码加减法有用,还可对无符号数加减法使用!

补码加减法运算在机器中的实现,下面同样是在之前介绍的加法器中 进行改进:

加法运算如下,由于是+,那么右边的Sub即为0,同样Y输入的减数由于控制信号传来的是0直接传入到加法器中参与运算,此时加法器右边的Cin=0,最终会将A、B、Cin加起来:

若是进行减法,手算的思路是令B的各个位全部取反+1,此时在加法器中怎么实现呢?

由于是减法,此时Sub控制信号为1,那么当Y输入进来的时候会走1这条路,会对所有位进行取反后传入到加法器里,在对于Cin此时由于是减法传入的值是1,那么也就相应的与我们的手算思路一致,只不过这个1是由Cin来传入的:

上述逻辑规则如下:

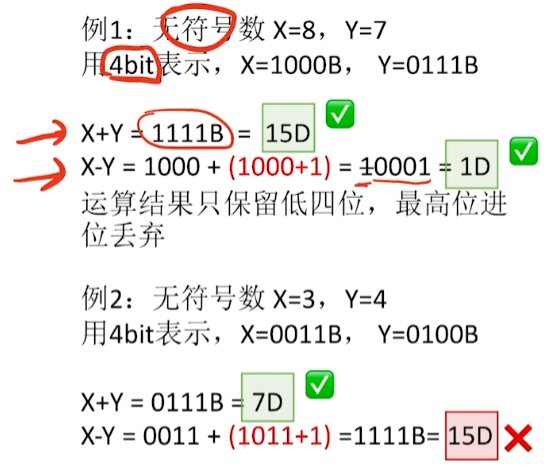

但此时还是有一个问题,那么就是在进行加减法过程中,对于溢出情况如何判断呢?我们各自对无符号数以及有符号数进行举例:

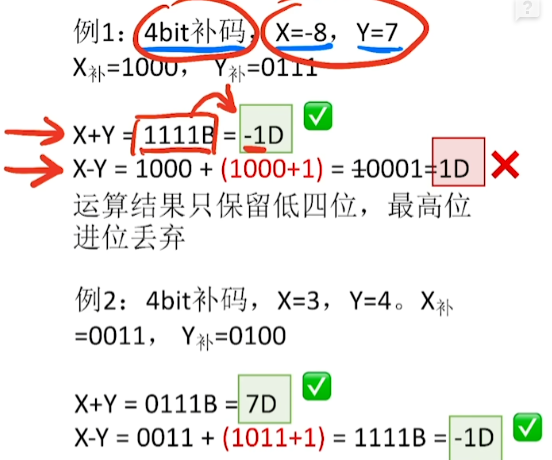

有符号数举例:

无符号数举例:

溢出情况举例梳理:

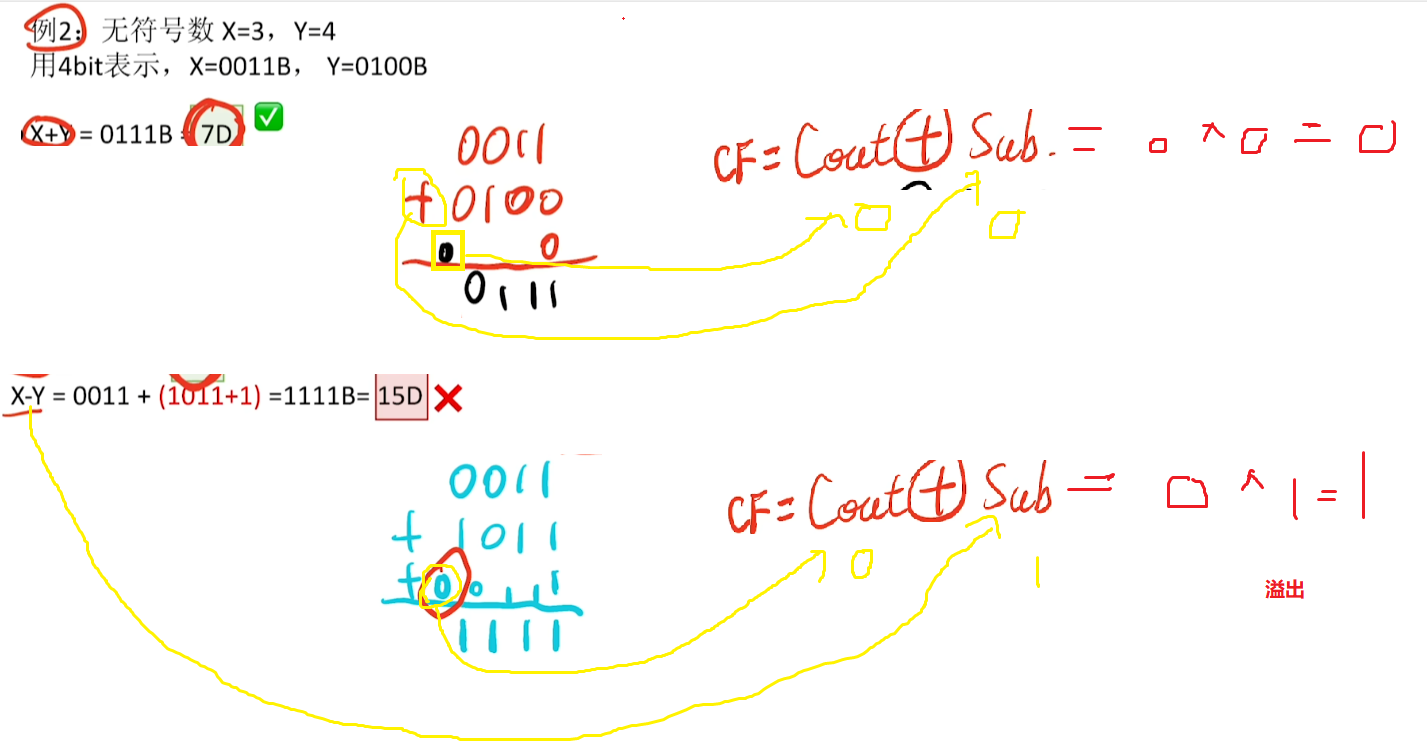

无符号数 X=3,Y=4

用4bit表示,X=0011B,Y=0100B

X-Y=0011 + (1011+1) = 1111B=15D ×

解释:实际最终求得的值为-1,而通过目前加法器流程可直接得到15是有问题的

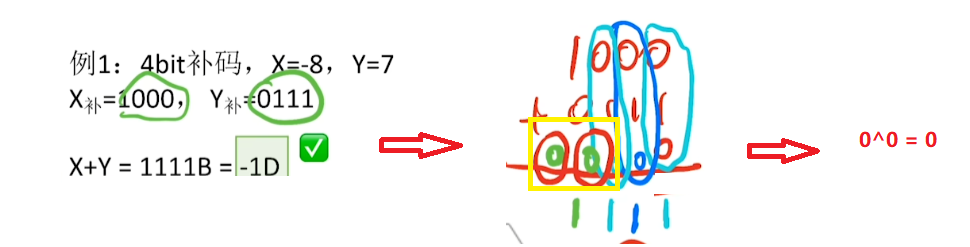

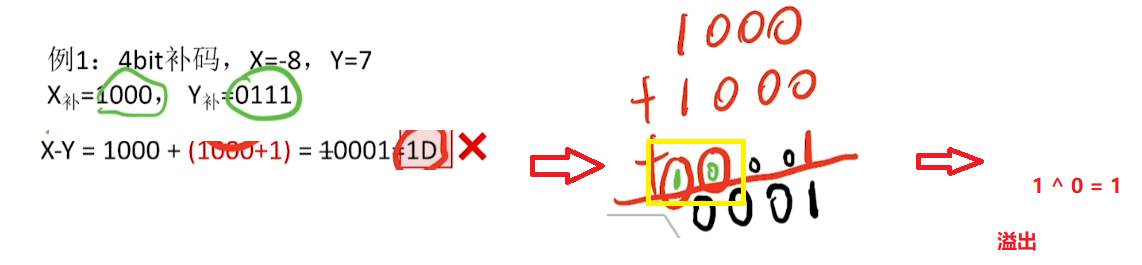

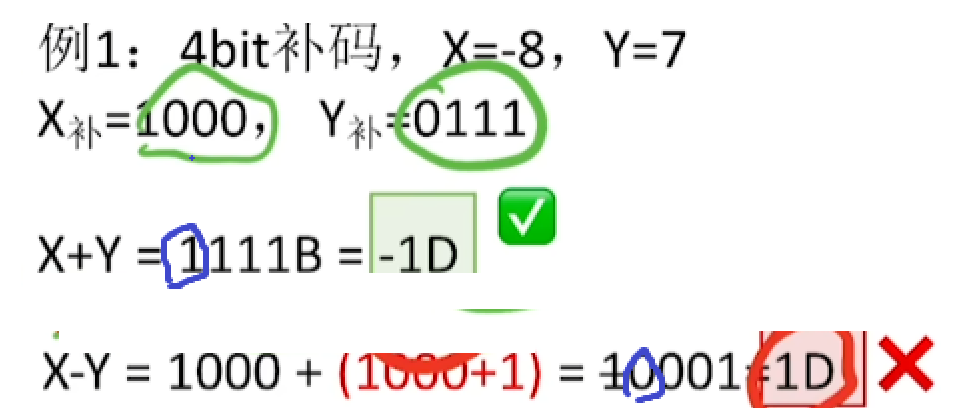

有符号数举例:

4bit补码,X=-8,Y=7

X补 = 1000,Y补=0111

X-Y=1000 + (1000 + 1) = 10001 = 1D

解释:实际最终求得的值为-15,表示数的只有3位,直接溢出了

对于上面的溢出情况,作为硬件的机器如何判断呢?下面是就出现了我们要介绍的标志位。

③标志位的生成(含义及详细示例解释)

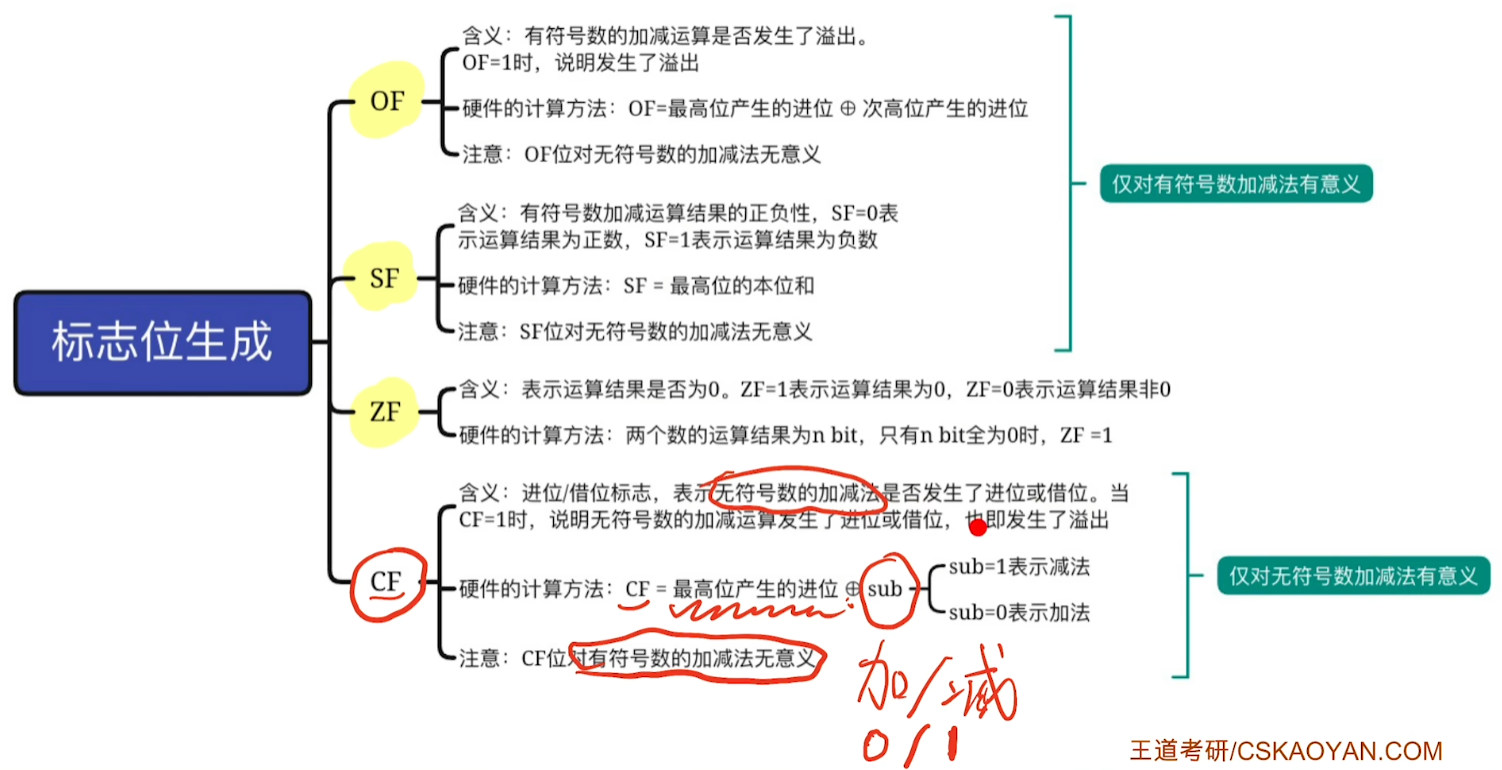

四个标志位如下画圈的位置:

四个标志位:

- OF标志位(Overflow Flag溢出标志):为最高位以及次高位的异或结果值。若是OF为1表示溢出,为0表示没有溢出。与无符号位无关。

- SF标志位(Sign Flag符号标志):结果为负时置1,否则置0。与无符号位无关。

- ZF标志位(Zero Flag零标志):运算结果为0置1,否则置0。

- CF标志位(Carry Flag进位/借位标志):发生进位/借位时置1,否则置0【CF= Cout ^ Sub,其中Cout值得是最高位进位值,Sub指的是加法还是减法,加法就是0,减法就是1】,若是最终CF为1那么就表示溢出。与有符号数无意义。

根据上面的标志位来进行一一解释:

①示例:针对有符号数,下面黄色框选出来的就是最高位与次高位

无溢出情况:

有溢出情况:

②示例:针对有符号数

下面紫色圈出来的我们就可以去得到SF标志位了,若是1则表示负数,SF置1,若是0表示正数,SF置0:

③示例:若是最终结果n个数都为0,那么就置为1,否则置为0。

④示例:针对于无符号数

是拿最高位进位与当前是进行加法还是减法操作(加法为0,减法为1)进行异或得到的值判断是否溢出,若是为1表示溢出,若是为0表示没有溢出。

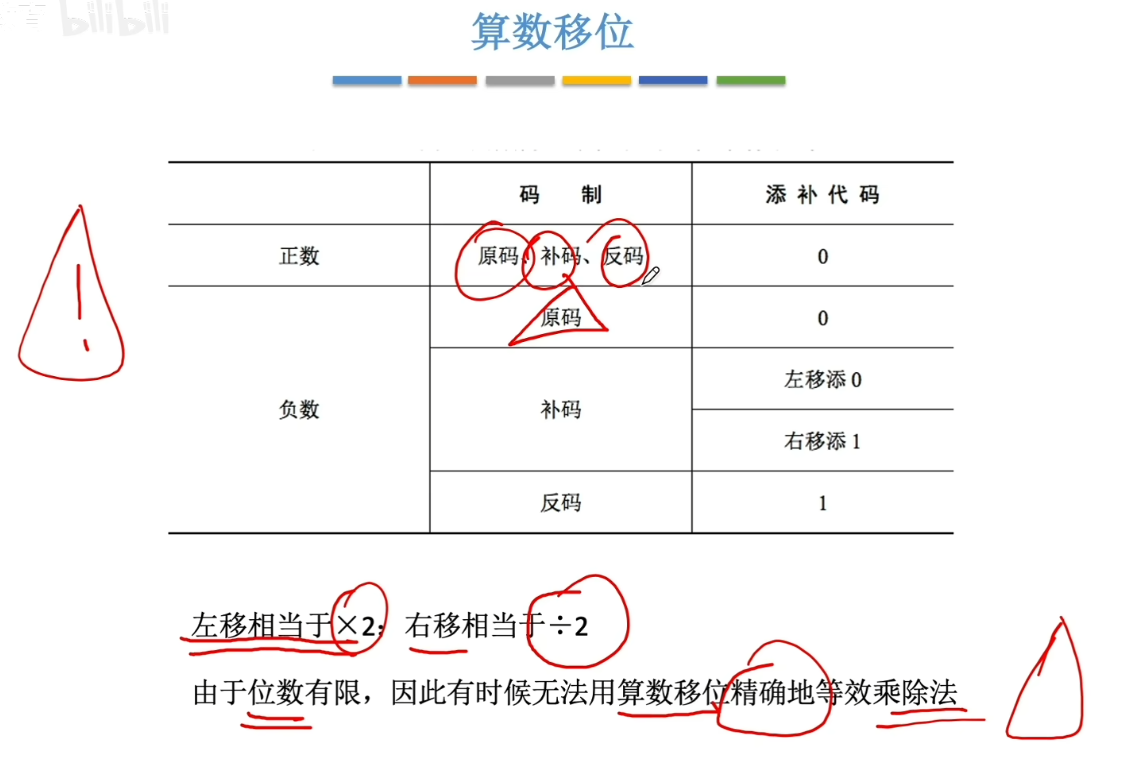

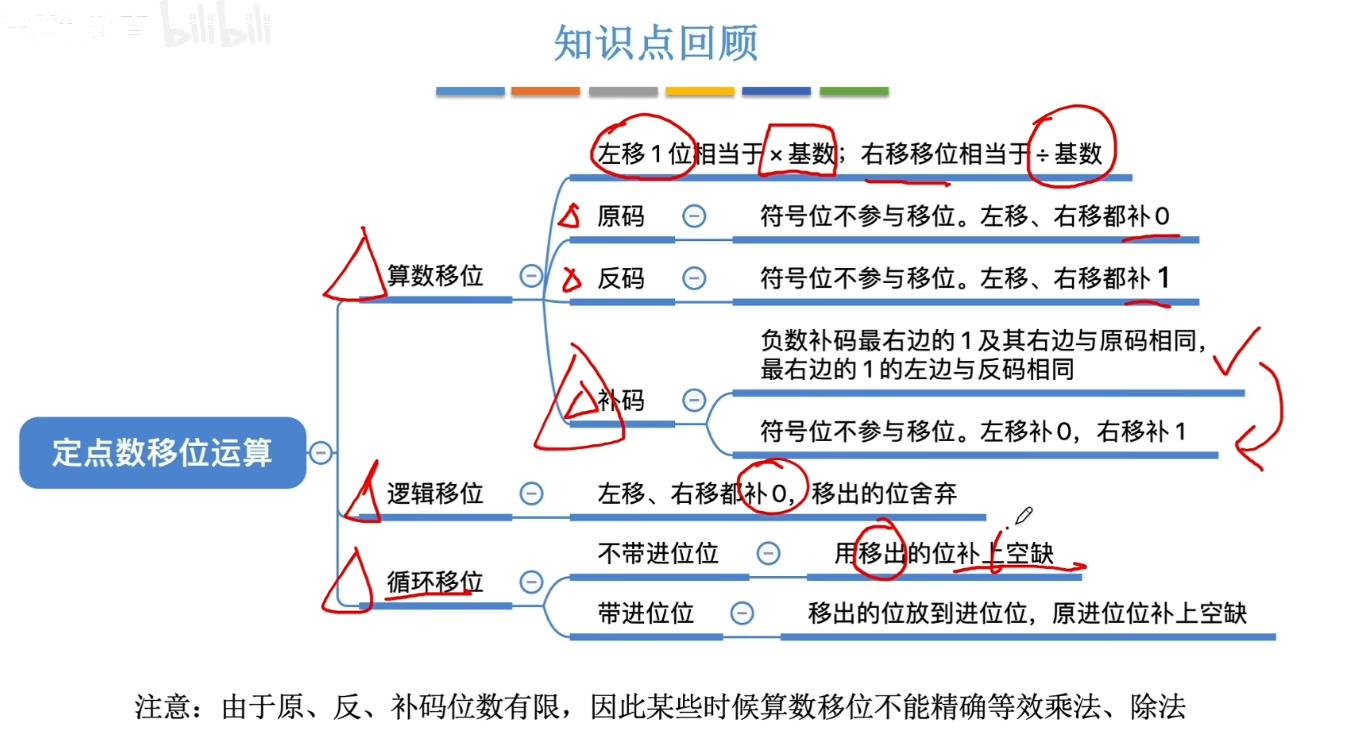

2.4、定点数的移位运算

2.4.1、算数移位

2.4.1.1、认识算数移位

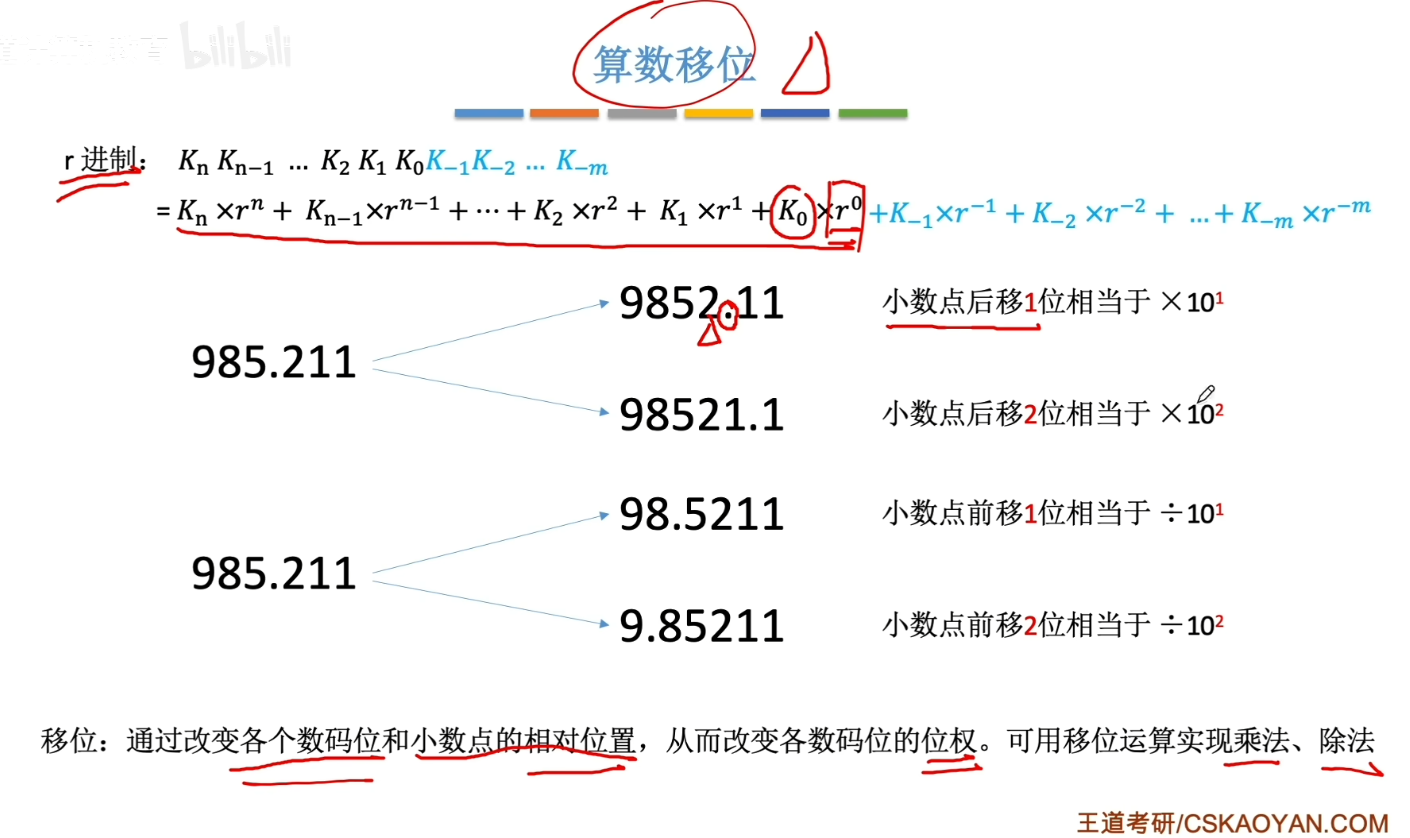

可以通过算数移位来实现乘法、除法运算:

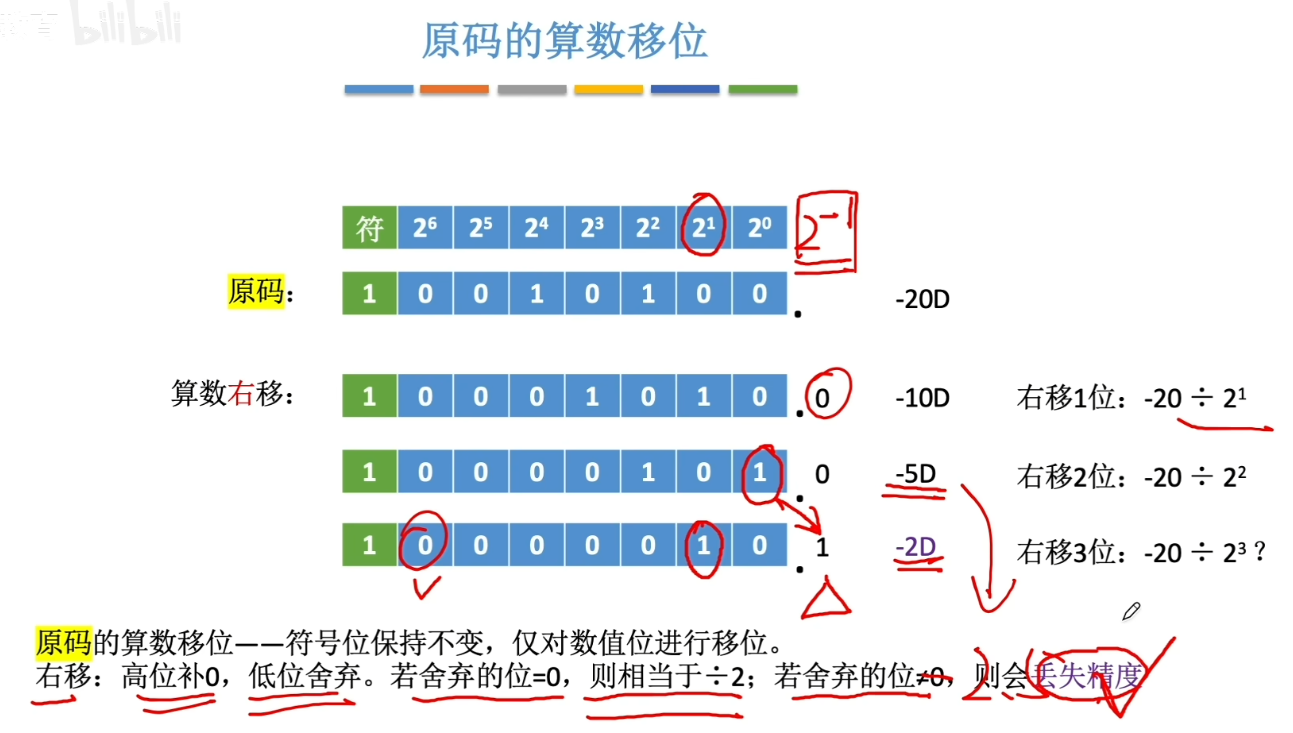

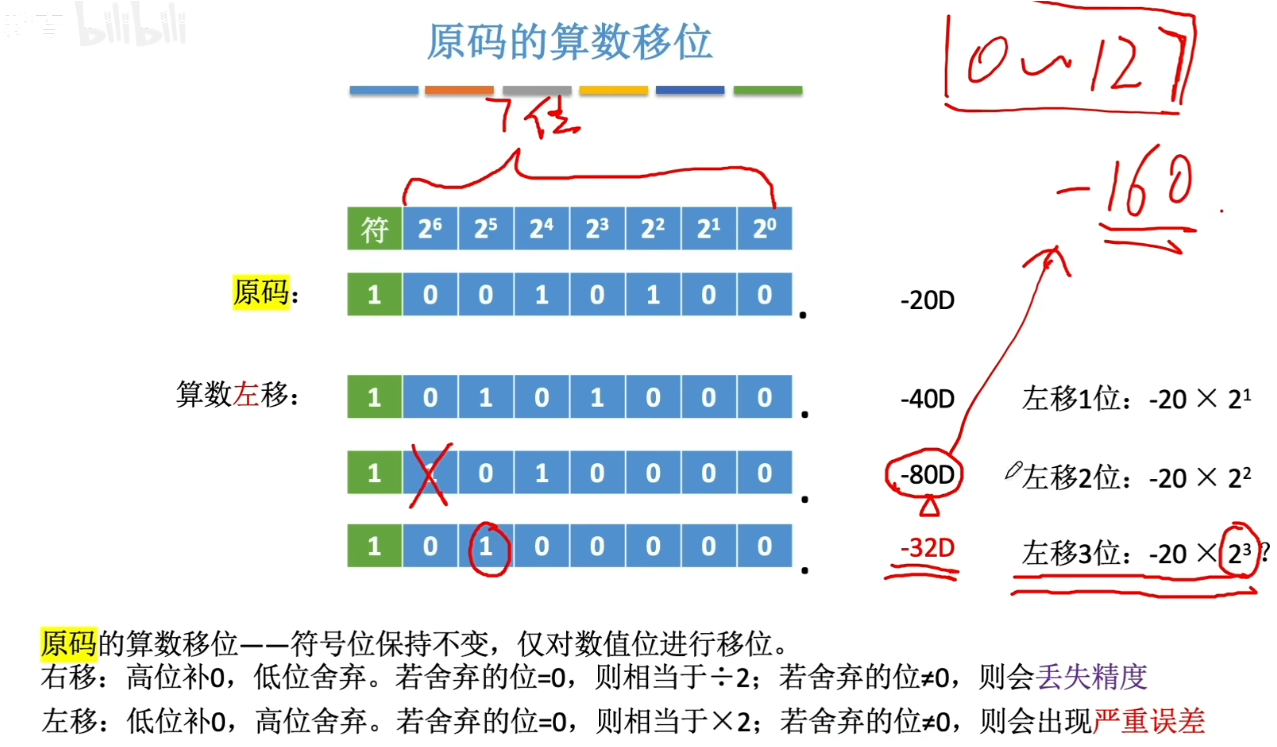

2.4.1.2、定点整数与小数的算数右移与左移(原码)

定点整数

算数右移(实现除法):①其中移出2位时,移出去的一位我们可以省去;②移出3位时,由于范围有限,就需要将移出的1省去,此时则丢失精度。

算数左移(实现乘法):①其中左移2位时,由于2倍乘为160,超过了原本范围的最大数127,此时就会出现计算出错的情况,实际省掉了最前的1。②其中左移3位时再次省略掉了前缀1,此时为-32。

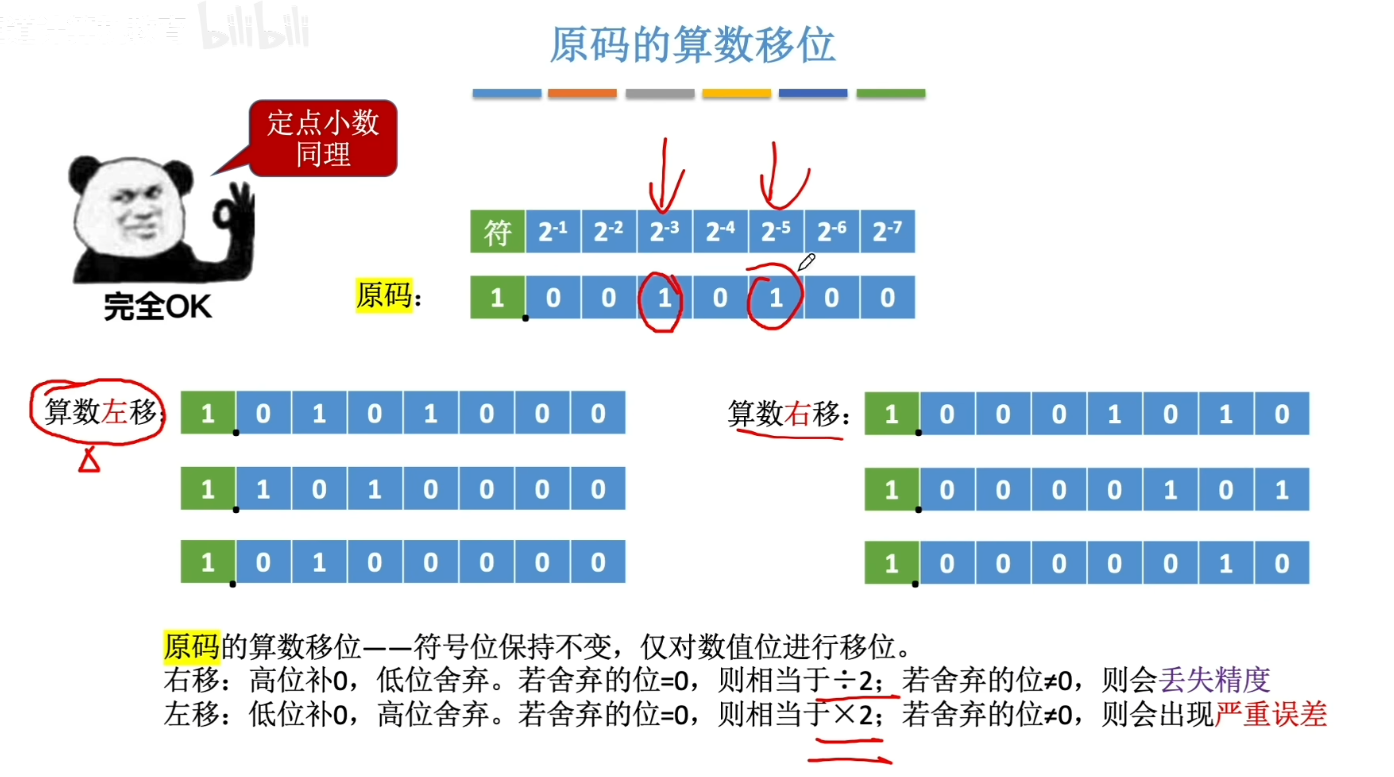

定点小数

定点小数:算数移位与定点整数一致

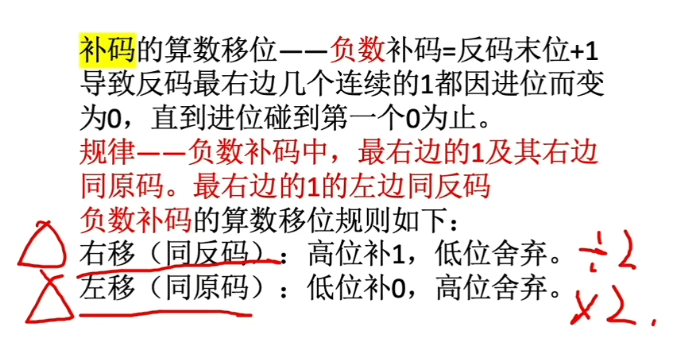

2.4.1.3、算数移位(补码)

2.4.1.4、算数移位的精简总结(原、反、补)

2.4.1.5、算数移位的应用

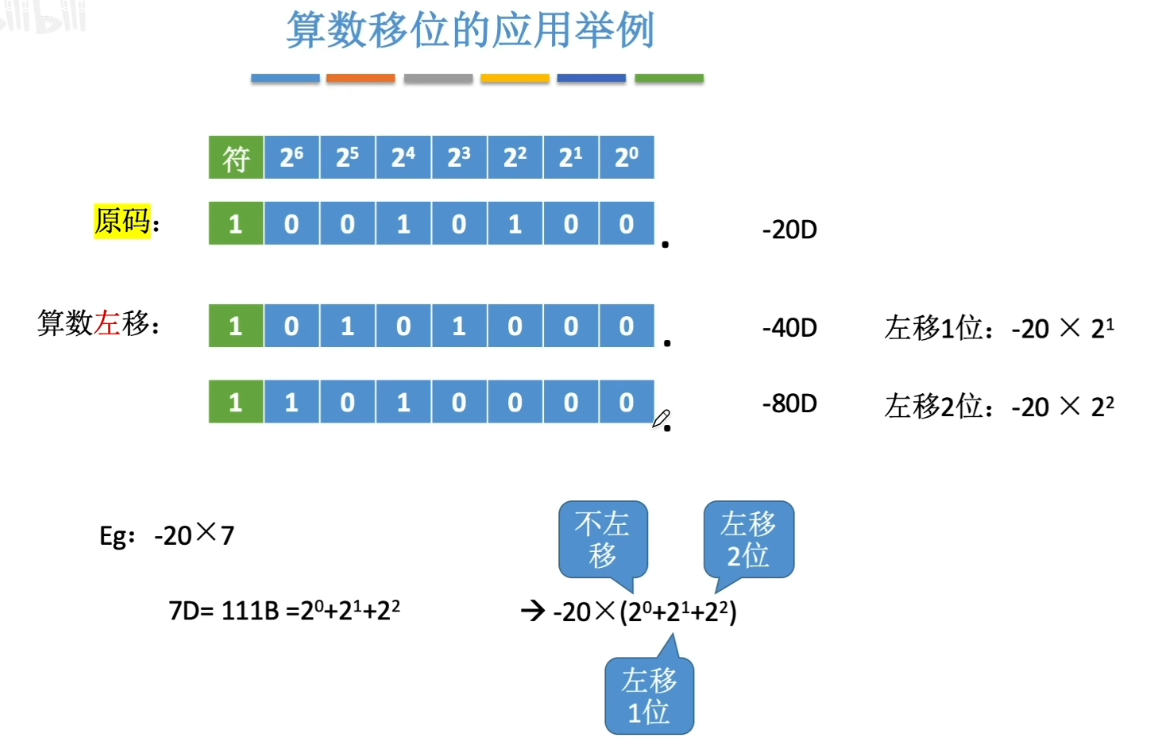

通过进行左移操作我们来实现乘法,如下:我们将乘数7可拆分为2的倍乘形式,拆好之后我们实际上可以看做是多个左移运算动作最后进行相加即可求得最终的乘积值

2.4.2、逻辑移位

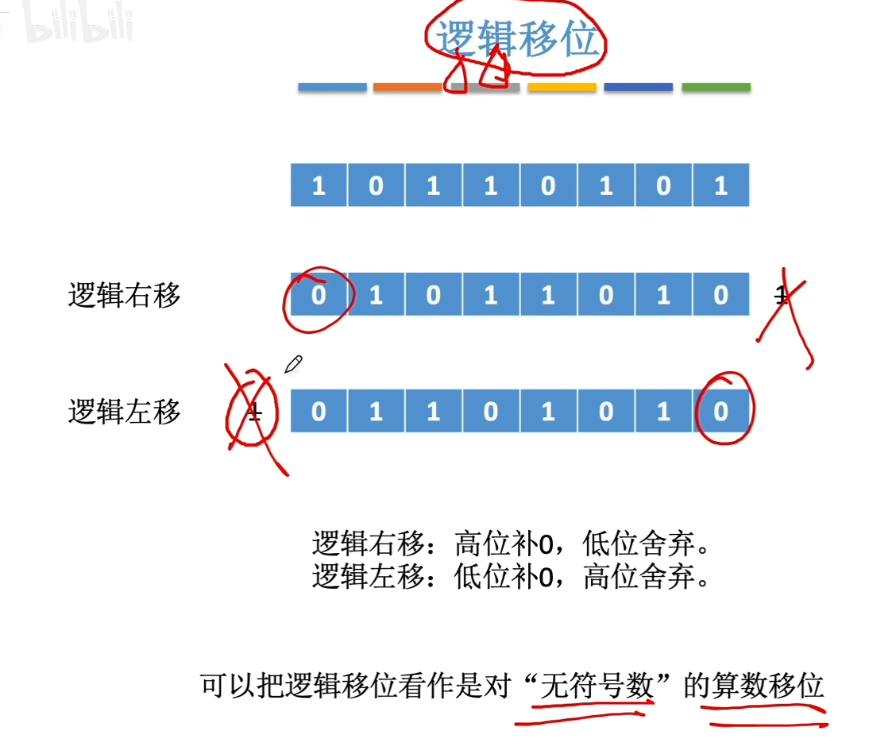

2.4.2.1、认识逻辑移位

2.4.2.2、逻辑移位的应用

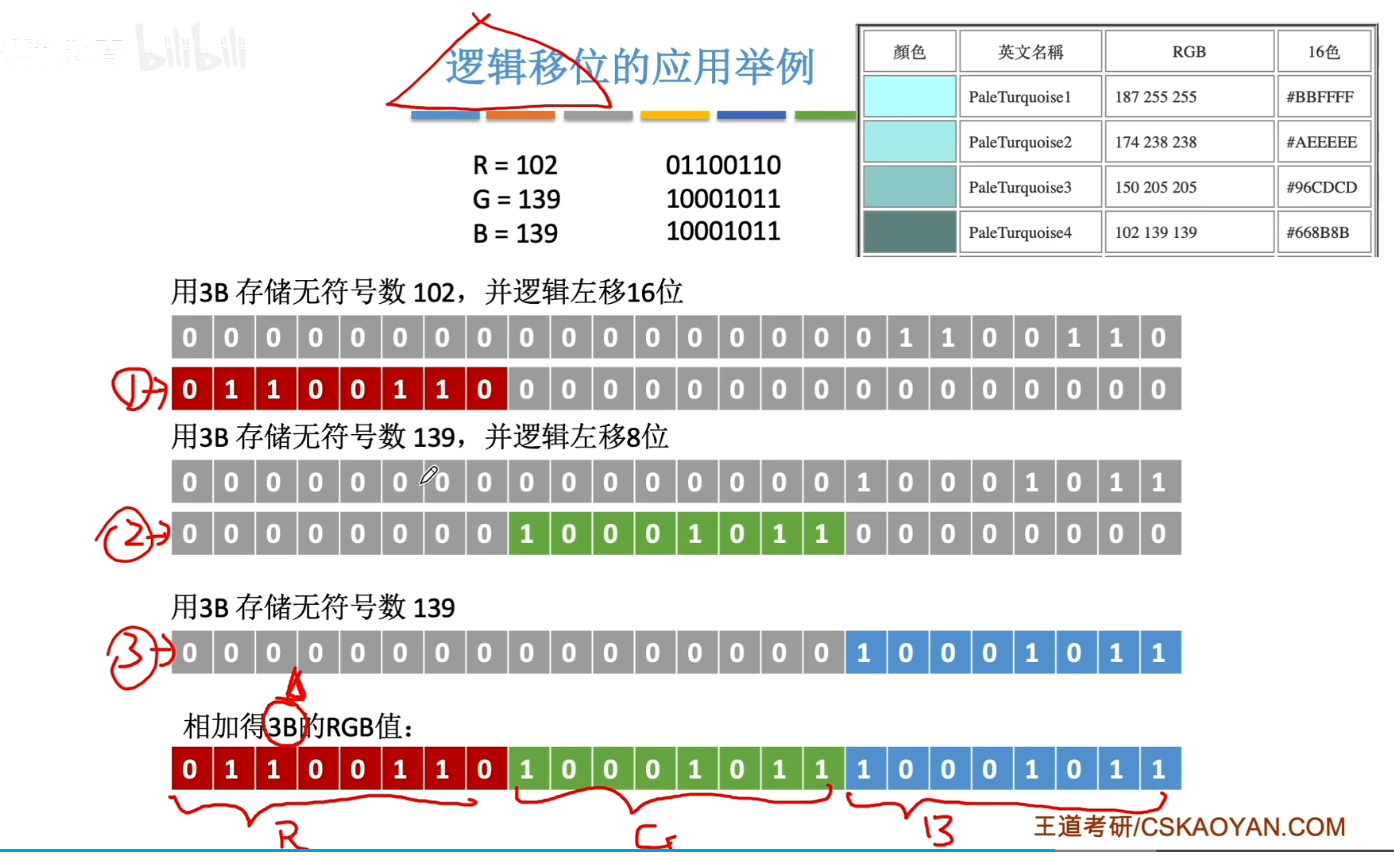

对于使用三个bit字节来存储RGB值,可以通过进行逻辑左移来实现移动高8位,中8位,低8位的值,最终相加得到一个完整的RGB。

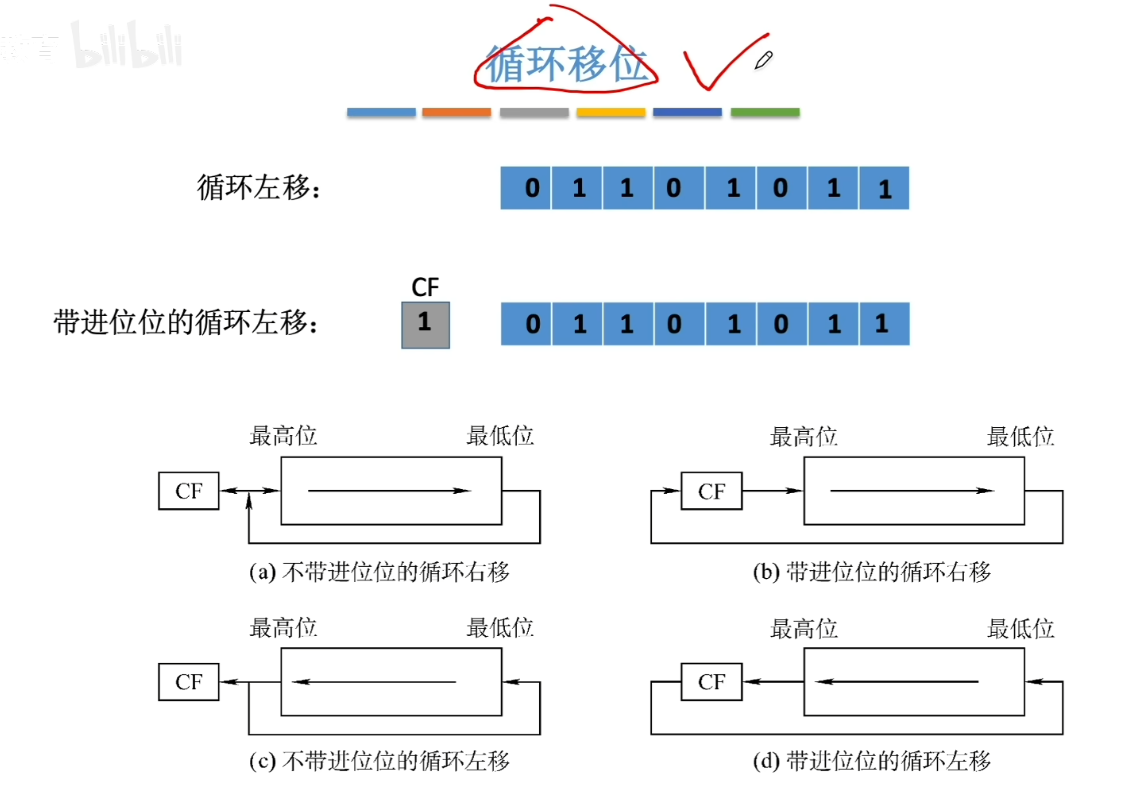

2.4.3、循环移位(含介绍与应用)

循环移位:左移与右移移出去的数字会在原本的末尾补上,达到循环的效果

实际应用:通过对一个字形编码其大端到小端之间的状态转换可以使用循环移位。

知识点总体回顾

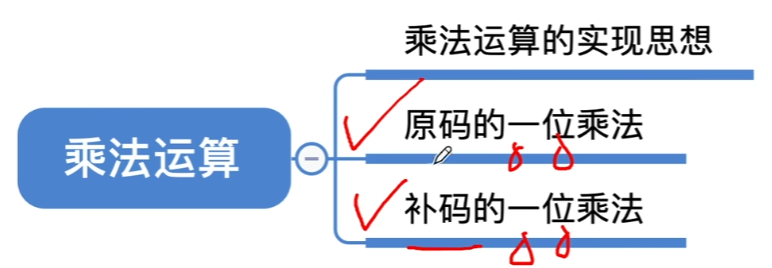

2.5、乘法运算

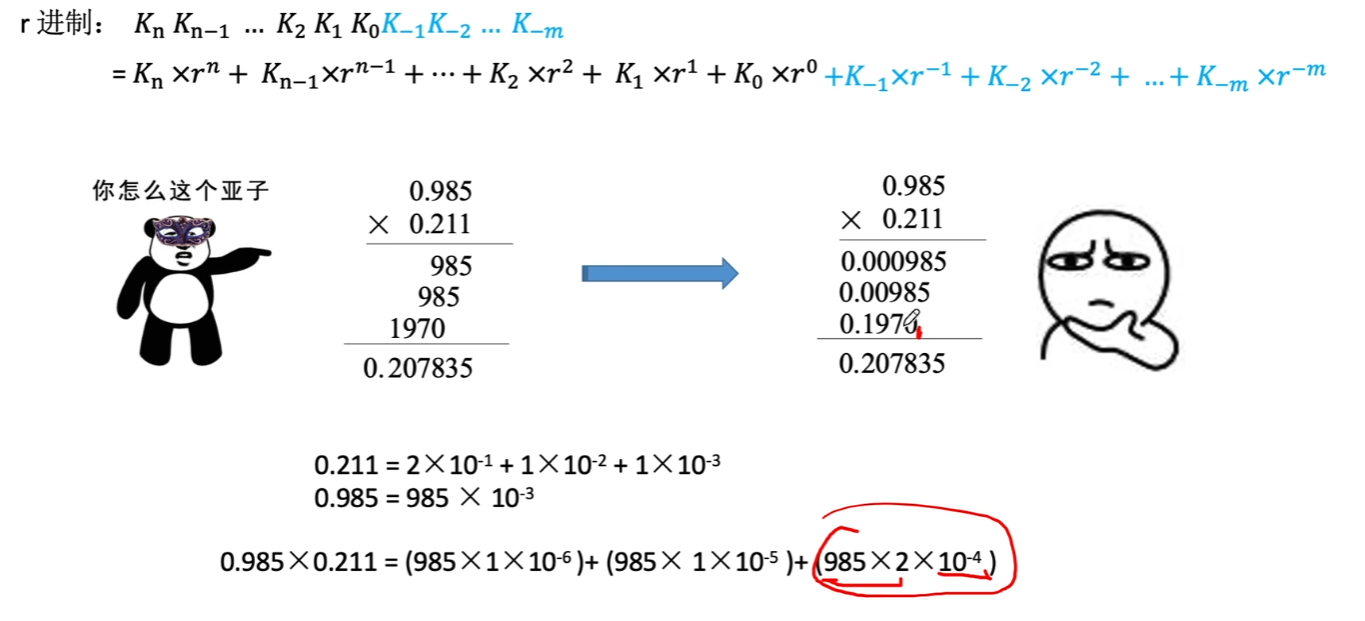

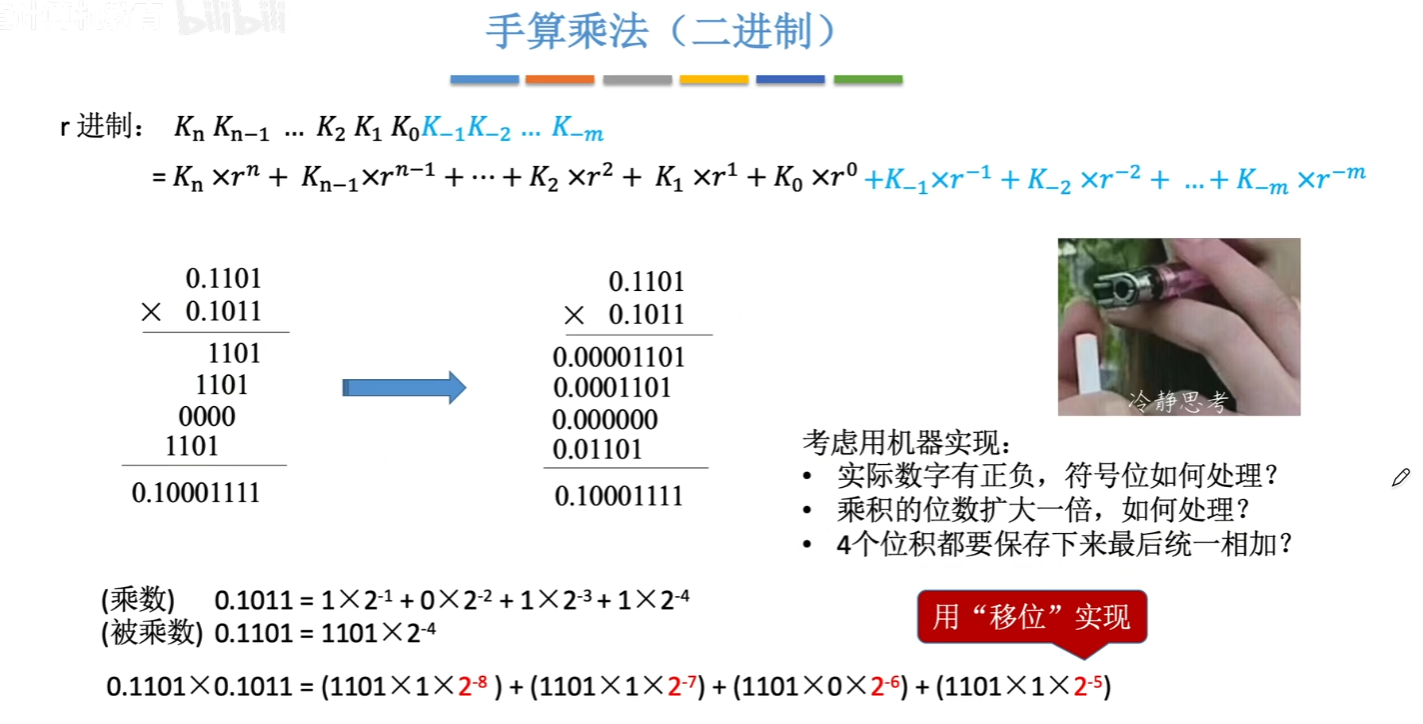

2.5.1、手算十进制与二进制乘法运算

手算十进制乘法:

手算二进制乘法:

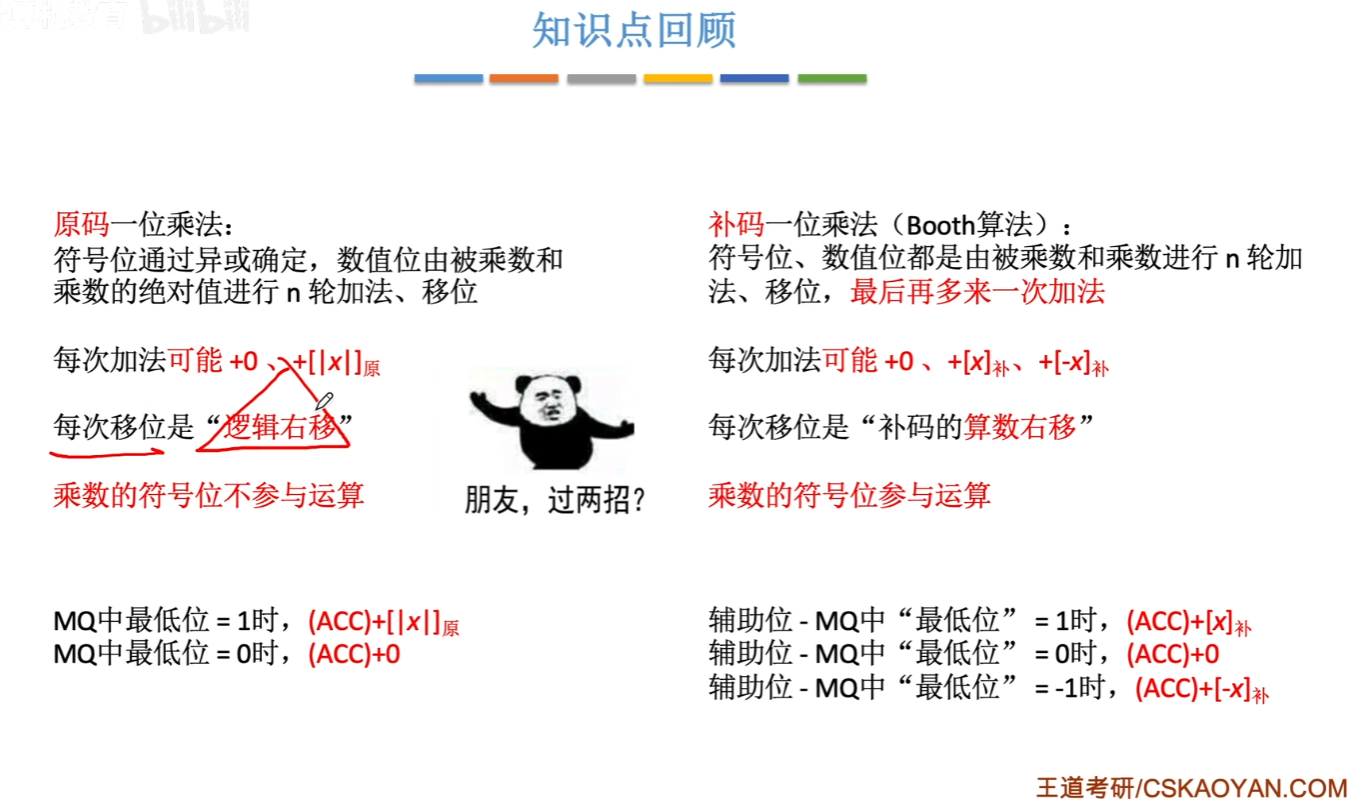

2.5.2、原码一位乘法

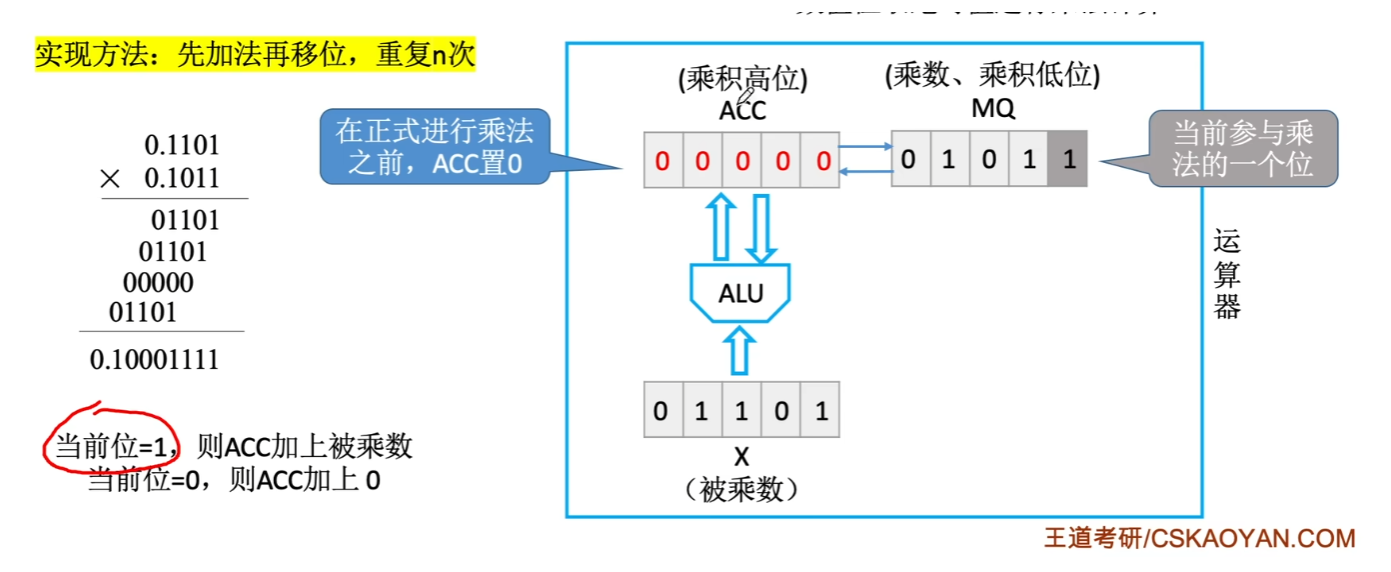

2.5.2.1、硬件机器实现原码一位乘法(详细)

硬件机器实现原码一位乘法:

初始时ACC寄存器会清零:

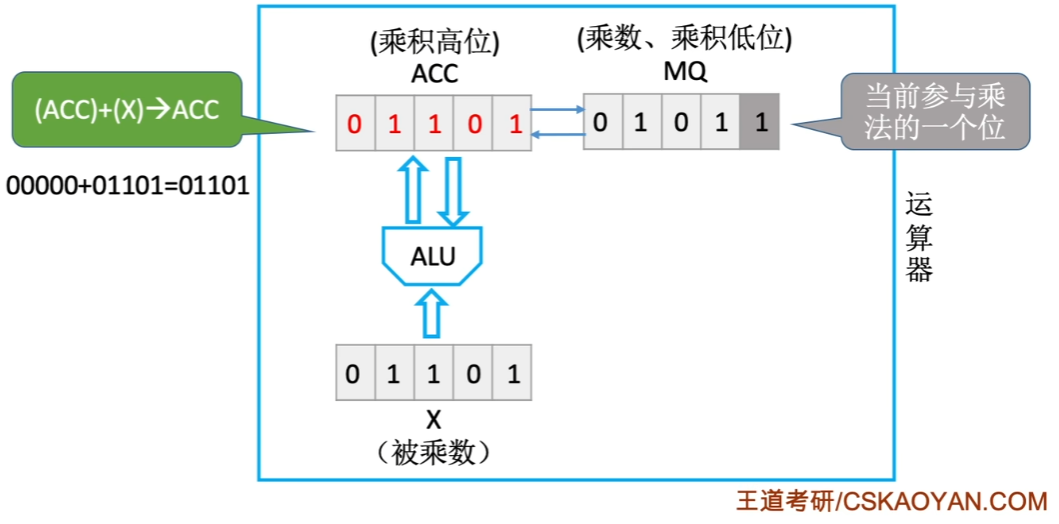

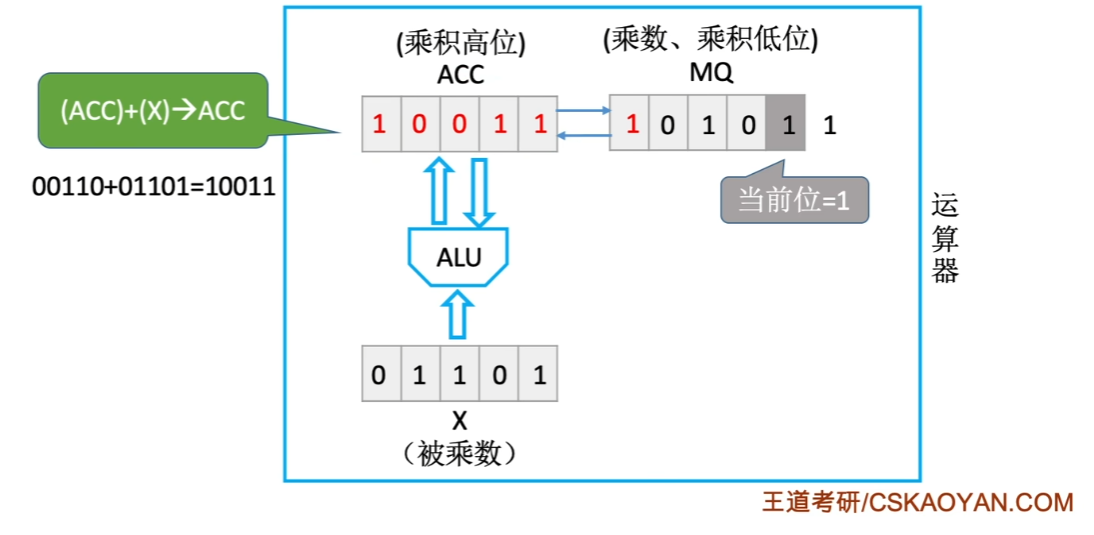

清零之后MQ的最后一位开始参与运算,最后一位为1,1 * 0.1101,此时进行相加:

00000 + 01101 = 01101

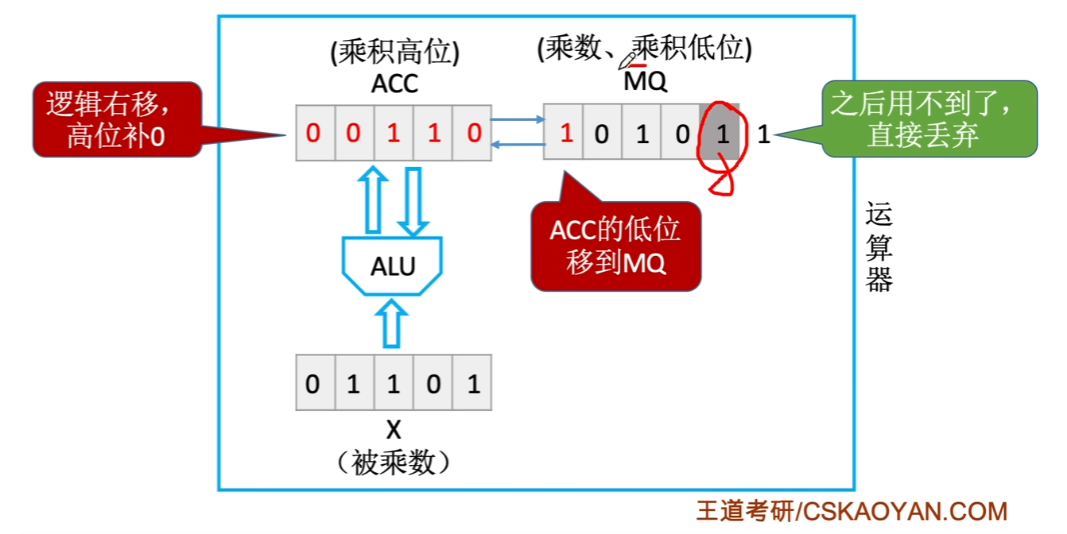

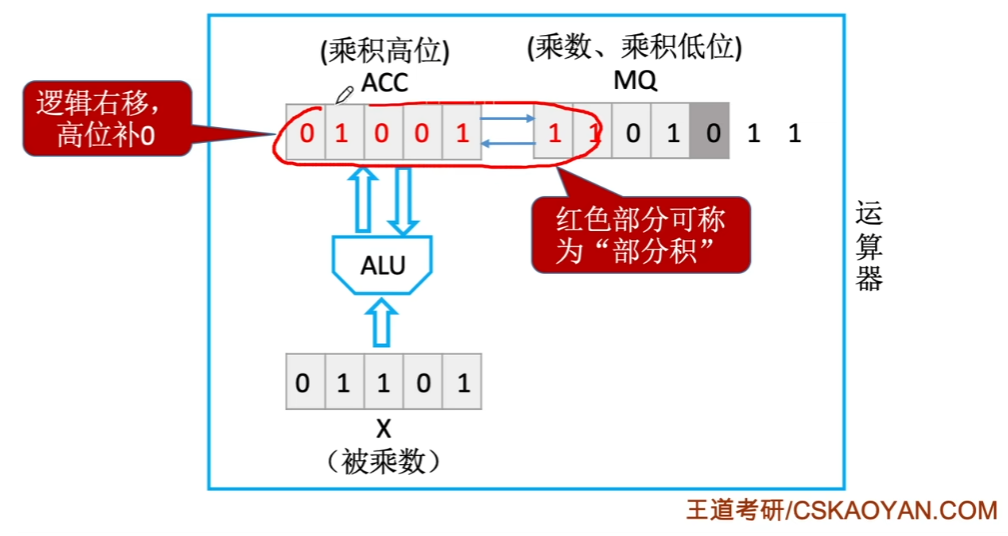

此时开始进行逻辑右移:这一步实际上我们将之前参与MQ最后的一位移除,因为这一位已经用过了所以可直接省略,让ACC的第一位来填充0,方便之后添加新的数据

此时我们完成的运算可以如下图所示:也就是得到的乘积,然后补了一个0,方便之后进行算数移位乘法后进行相加

此时MQ最后一位还是1,接着进行乘法运算后再次进行加法运算,完成加法运算后我们进行逻辑右移:

加法运算:

逻辑右移:

之后的过程如上面一样,进行剩余数的乘积…

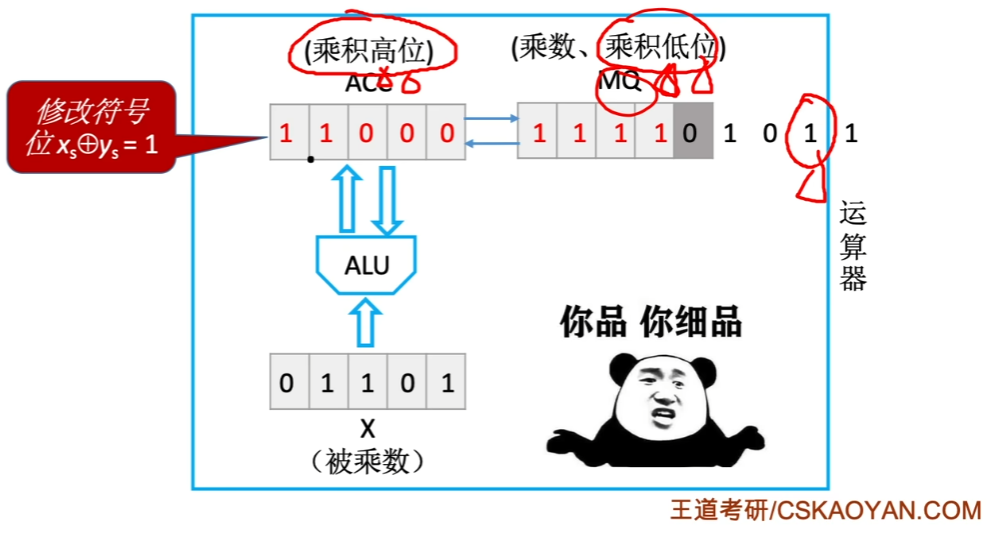

最终将MQ中的01011都进行乘法运算后进行累加到ACC中即可完成得到最终的一个乘积值:

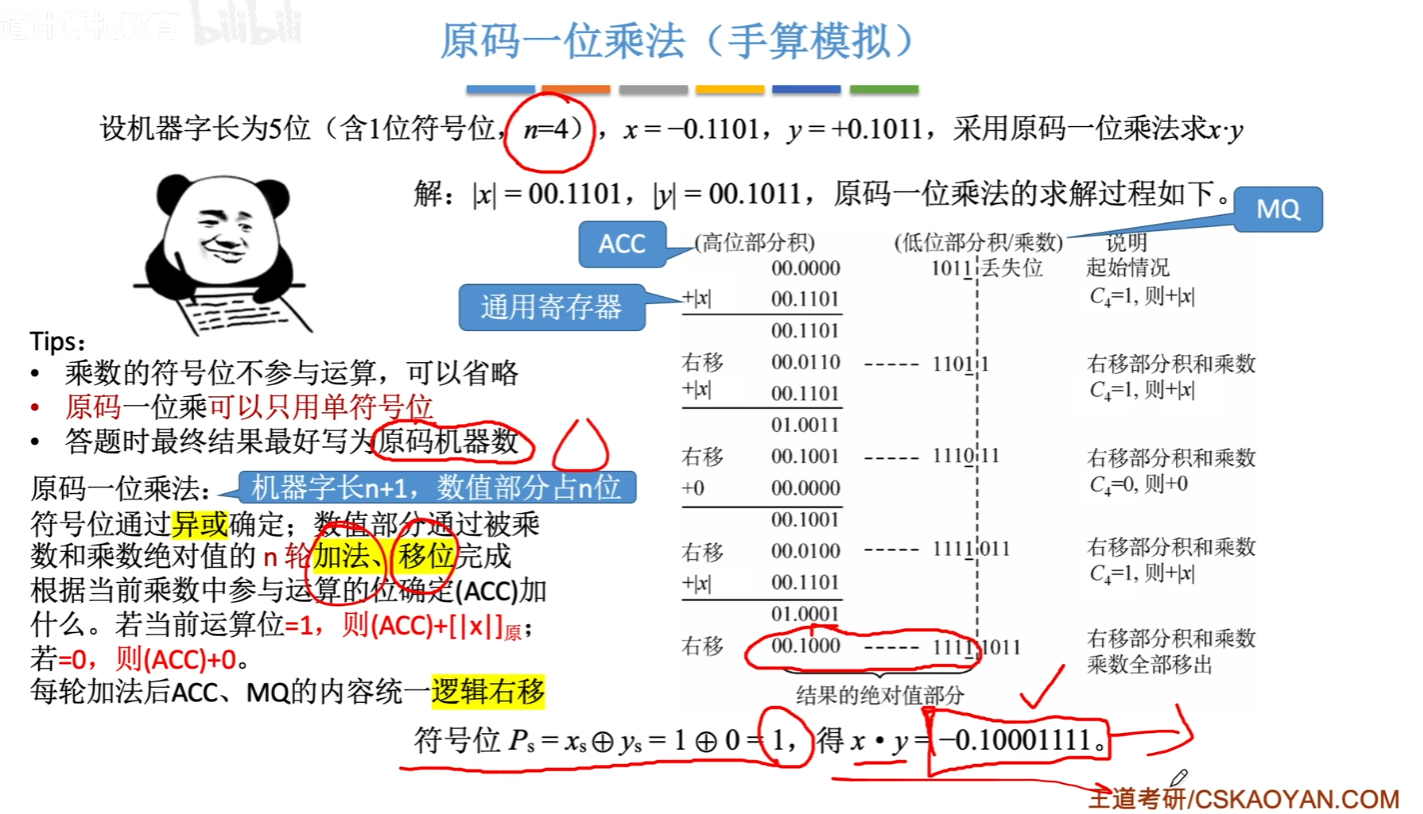

2.5.2.2、手算模拟原码乘法

手算模拟:实际我们的手算也就是来对机器硬件进行模拟计算,详细过程如下展示

1、求得x与y的绝对值,初始ACC从0开始。

2、使用MQ最后一位来乘上被乘数相加ACC,最后进行逻辑右移操作,即可完成一轮乘法。

3、最终MQ的各个数都完成了乘法累加后,我们来使用乘数与被乘数的符号值进行异或确定乘法的标志位。

下面使用的是小数乘法的例子,对于整数原码乘法也是类似的:

2.5.3、补码一位乘法

对比原码一位乘法进行计算:

2.5.3.1、硬件机器实现补码一位乘法

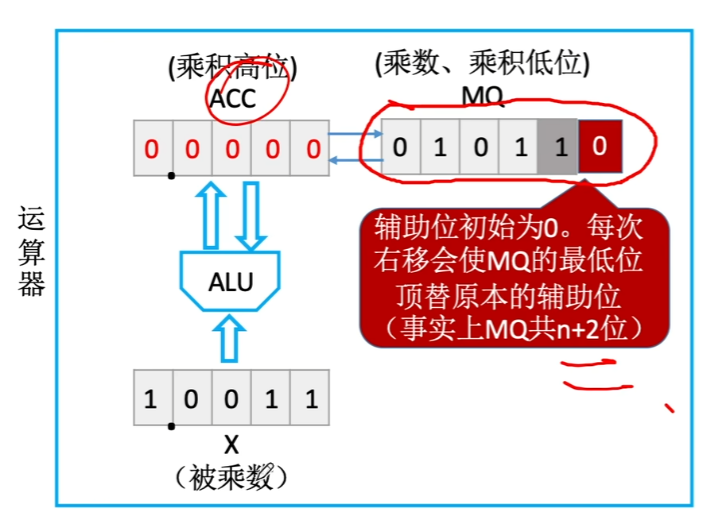

硬件实现运算:对于MQ多加了一位用于存储辅助位,实际MQ共n+2位

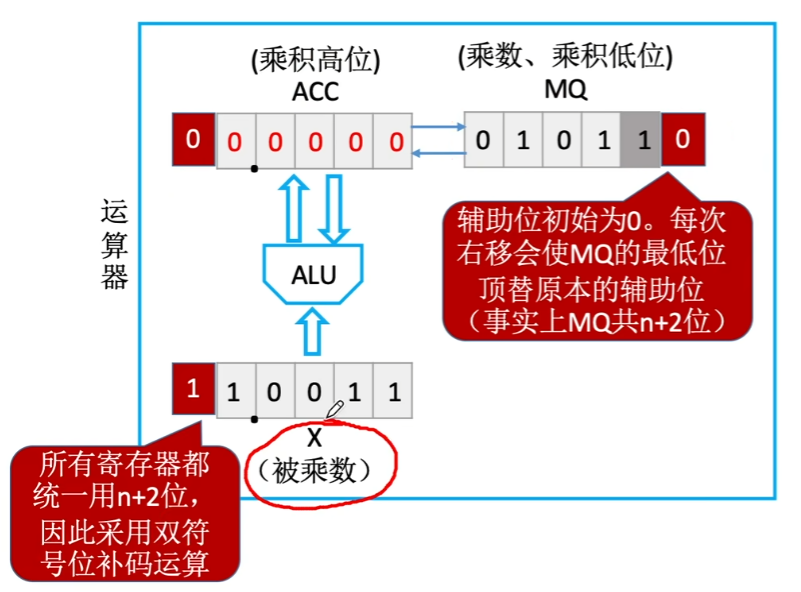

对于这种情况由于MQ多增加了一位,此时对于ACC与X都会增加一位,此时多出来的一位则采用双符号位来进行运算:

在这个过程中,每次加法可能会+[x]补、+[-x]补,这个[-x]补会有辅助电路来给我们快速转换实现,通过辅助电路的处理之后送到ALU!

2.5.3.2、手算模拟补码乘法

手算模拟的实现过程:

1、初始ACC从0开始,符号位直接参与运算,ACC多增加一位。

2、通过比较Yi - Yi-1来确定+[x]补、0、+[-x]补来相加ACC,最后进行算数右移,即可完成一轮乘法,总共进行n+1轮。

3、最终求得的值即为最后的补码乘法结果值。

知识点回顾

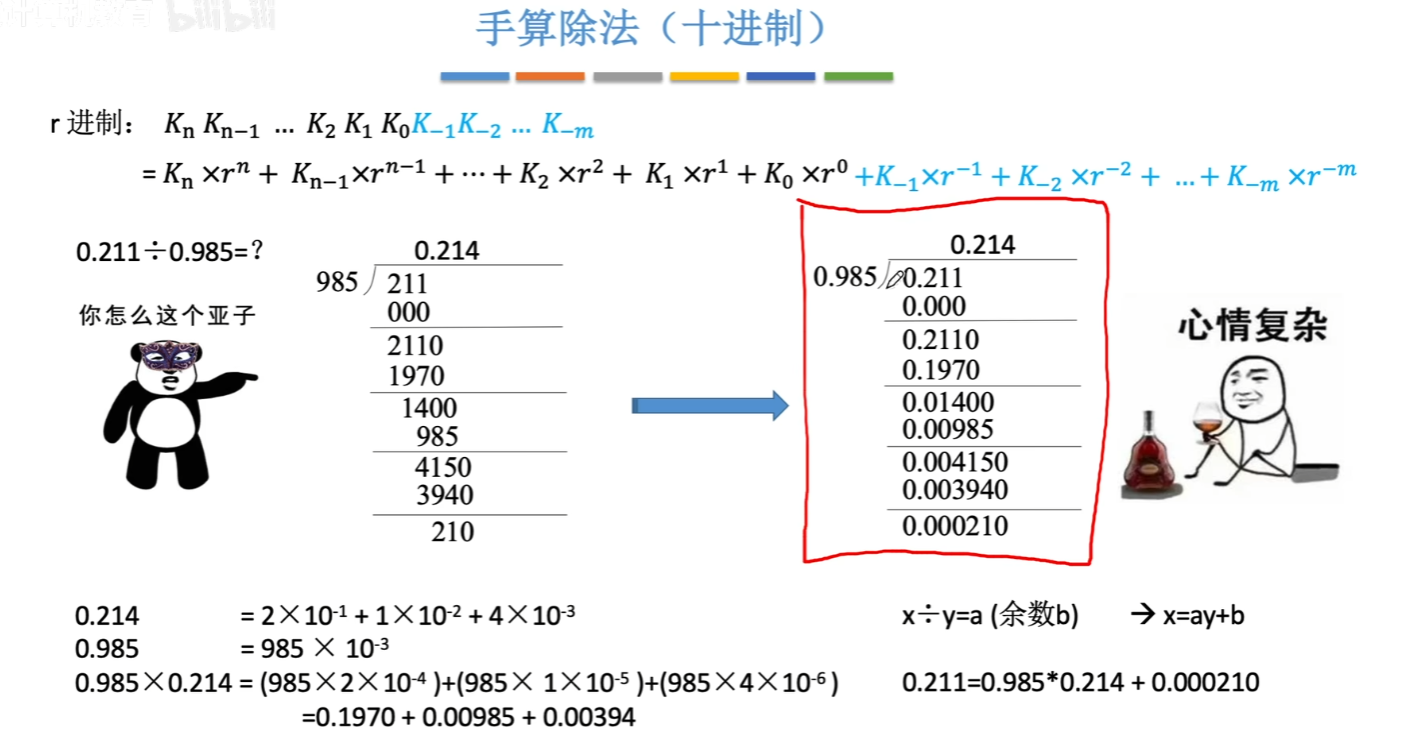

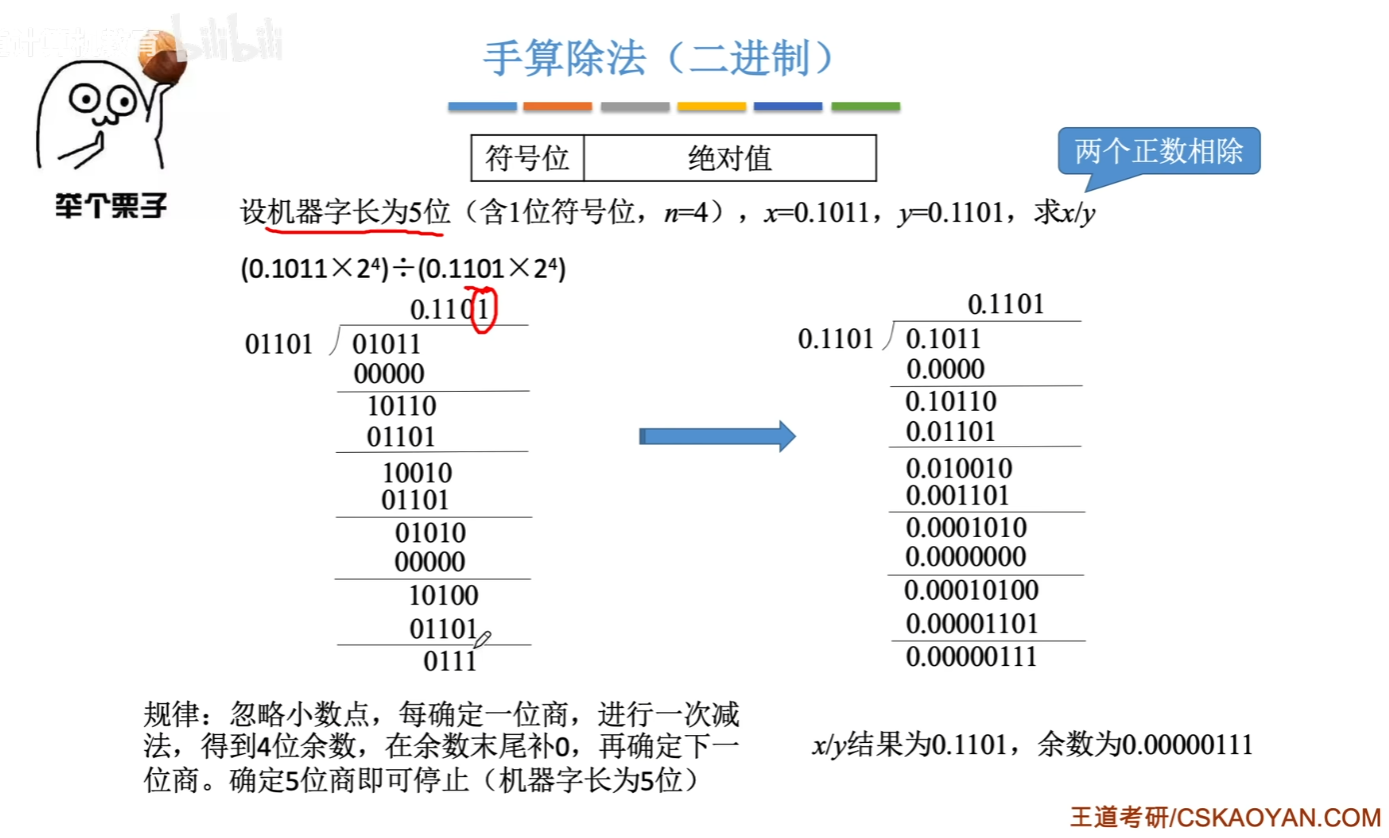

每次算得到的一位乘除数来最靠近当前的被除数的值:

手算二进制除法:每一位要么是0要么就是1,来去不断拼凑

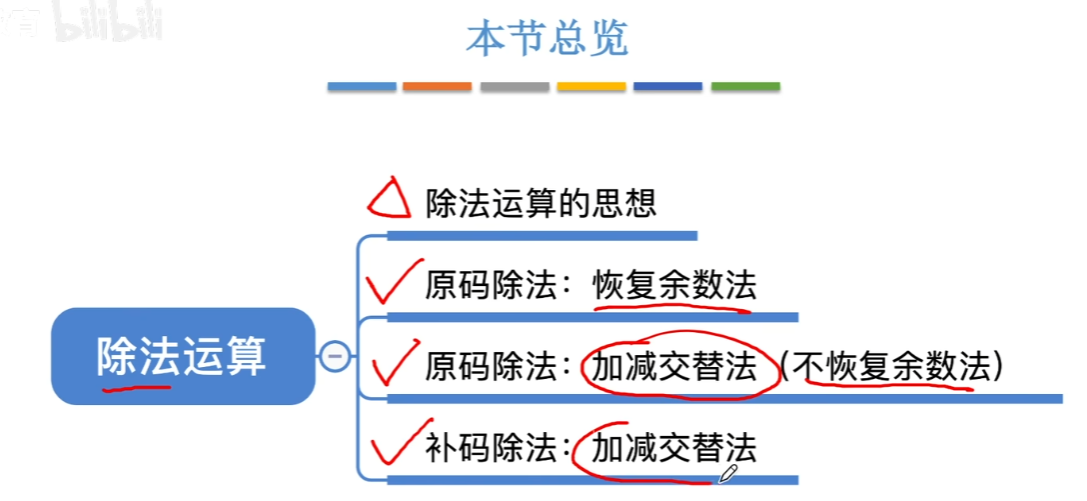

2.6、除法运算

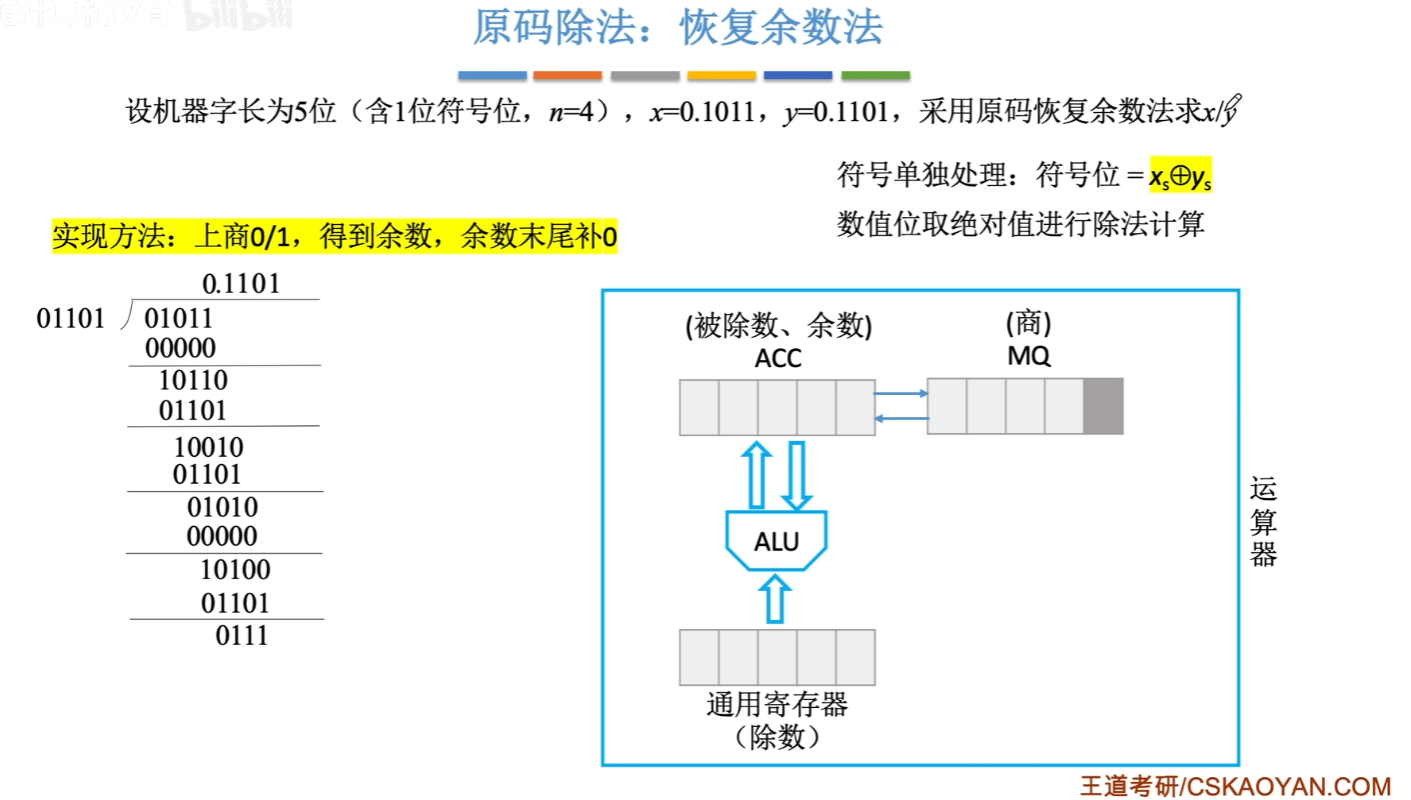

2.6.1、原码除法计算(恢复余数法及加减交替法)

2.6.1.1、机器硬件模拟实现原码除法(恢复余数法及加减交替法)

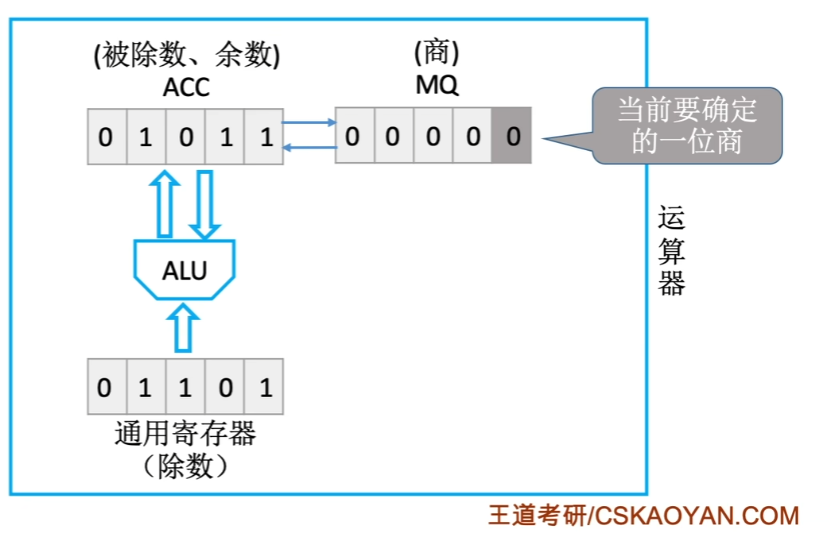

机器硬件实现:

首先商会进行初始化:

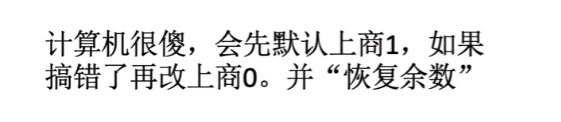

接着对于恢复余数法,计算机会默认先直接商1,若是得到的结尾为负数,则会更改商0:

这个商1后发现结果为负数,又改为商0得到的结果如下:

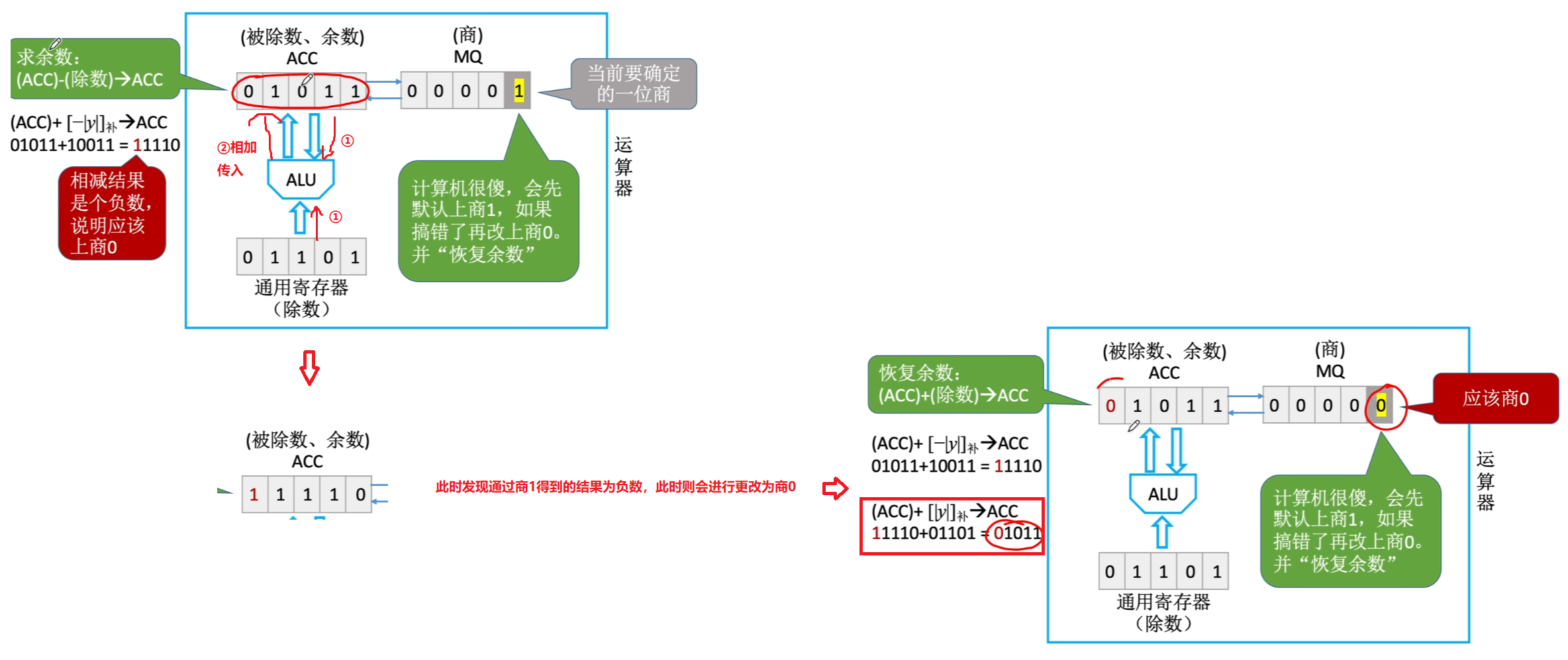

此时则ACC、MQ会进行统一的逻辑左移:

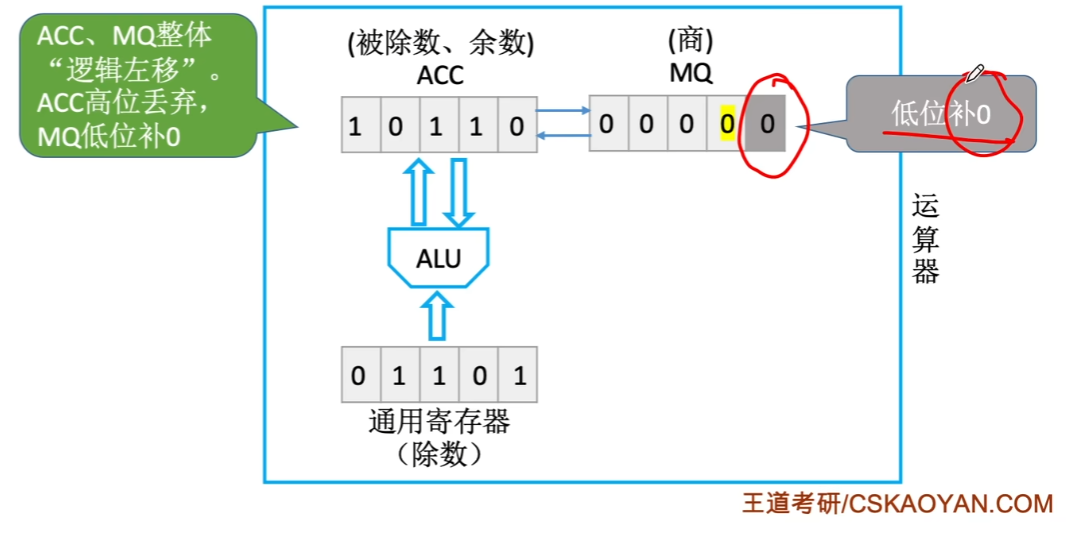

之后的步骤同样如此,最终即可得到最后的结果:

其中符号位是根据被除数、余数的符号位异或得到的。

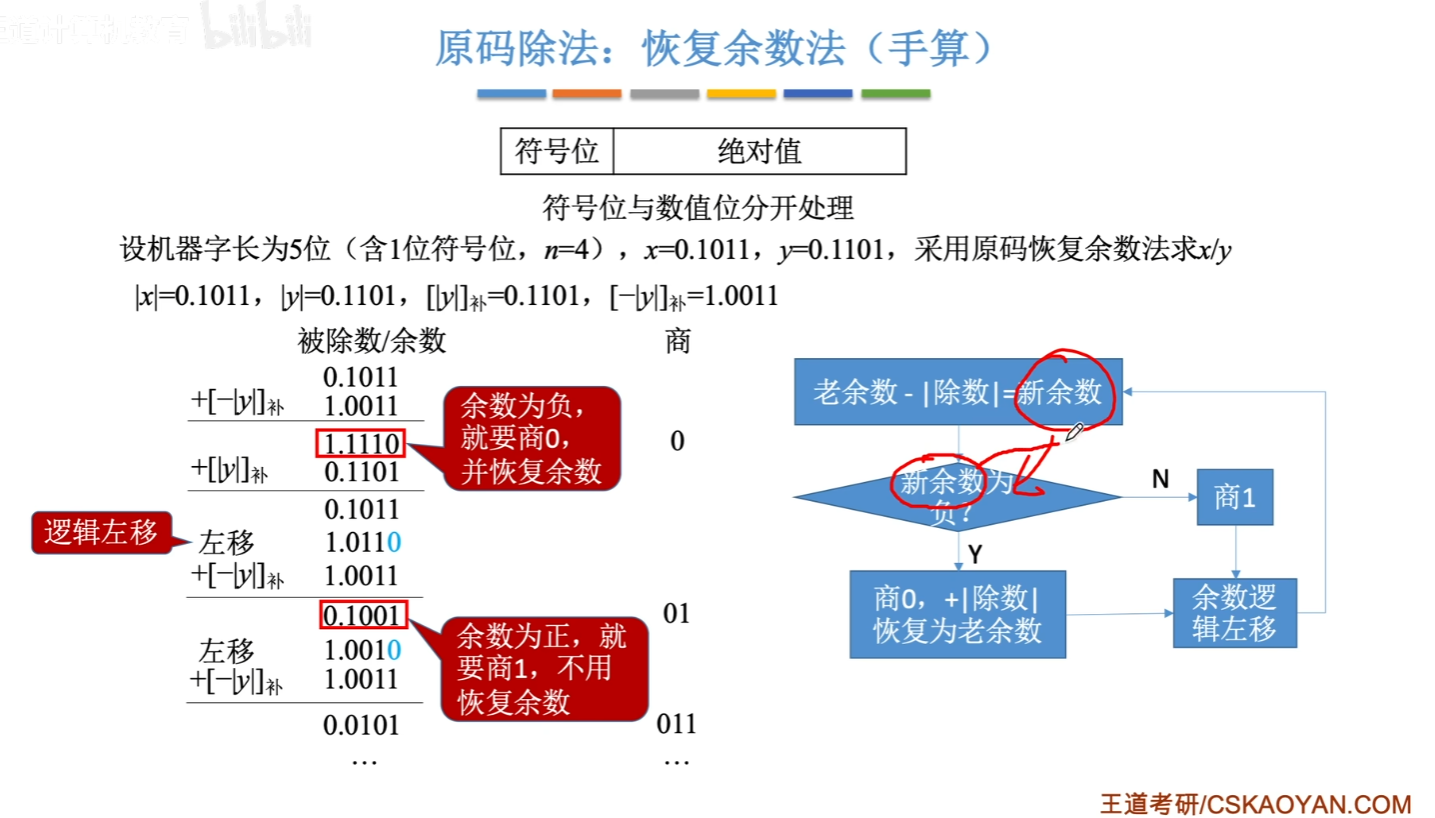

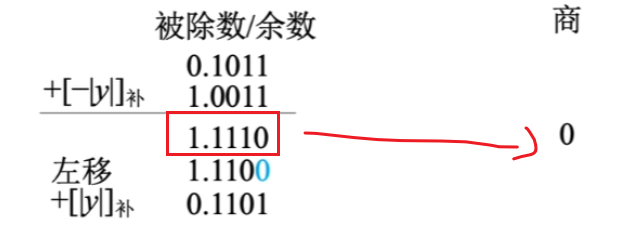

2.6.1.2、手算原码除法(恢复余数法)

手算模拟恢复余数法:一开始直接商1,若是结果为负数,表示商错了改为0,此时之后的步骤则是根据第一次的结果值来进行+[y]补、+[-y]补。

可以看到第一次直接商1,得到负数后我们修改重新为商0,此时需要重新进行计算,如下:

- 其实上图中的后两个左移是由于直接商1得到的是负数,才不需要恢复的,这个点一定要注意下!

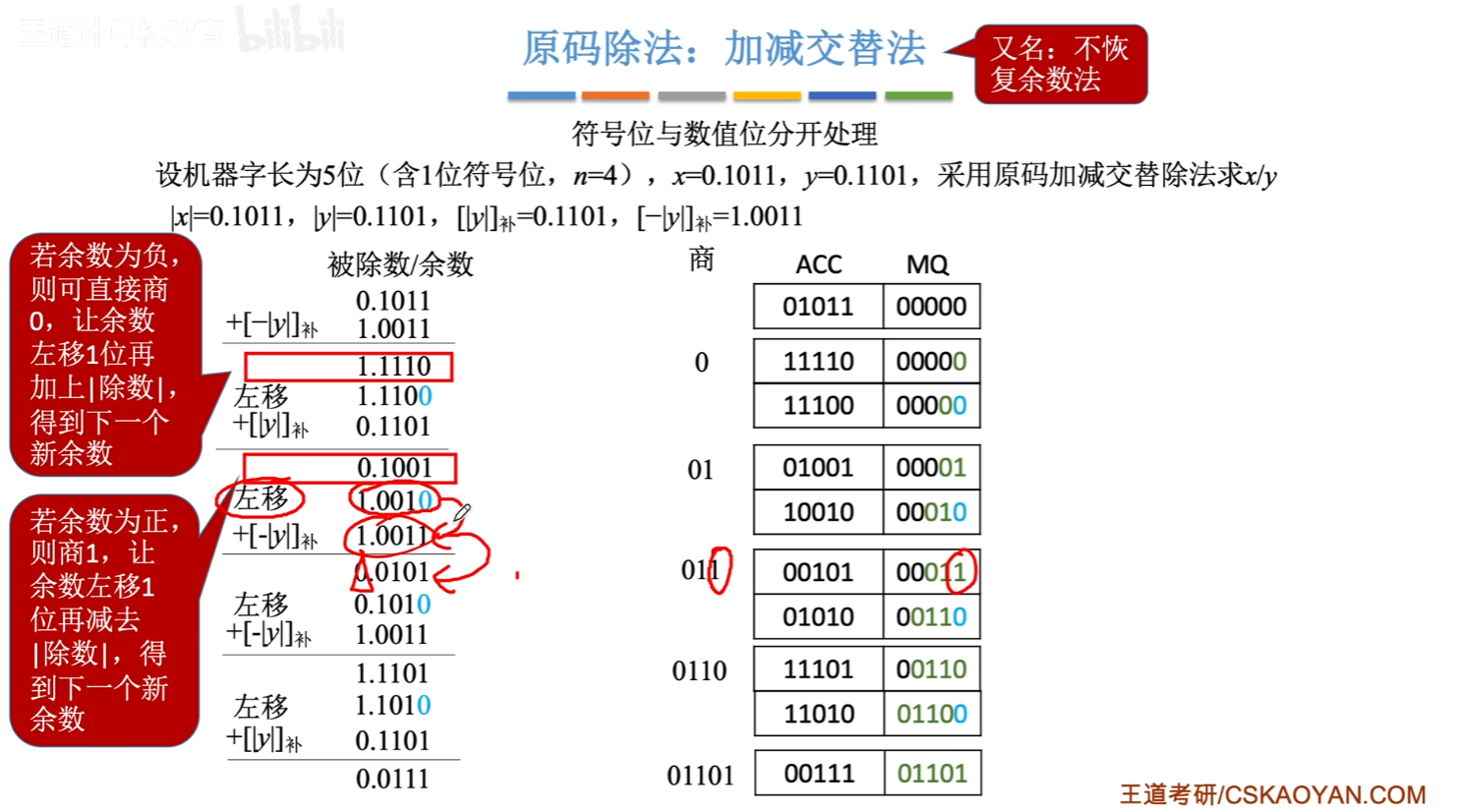

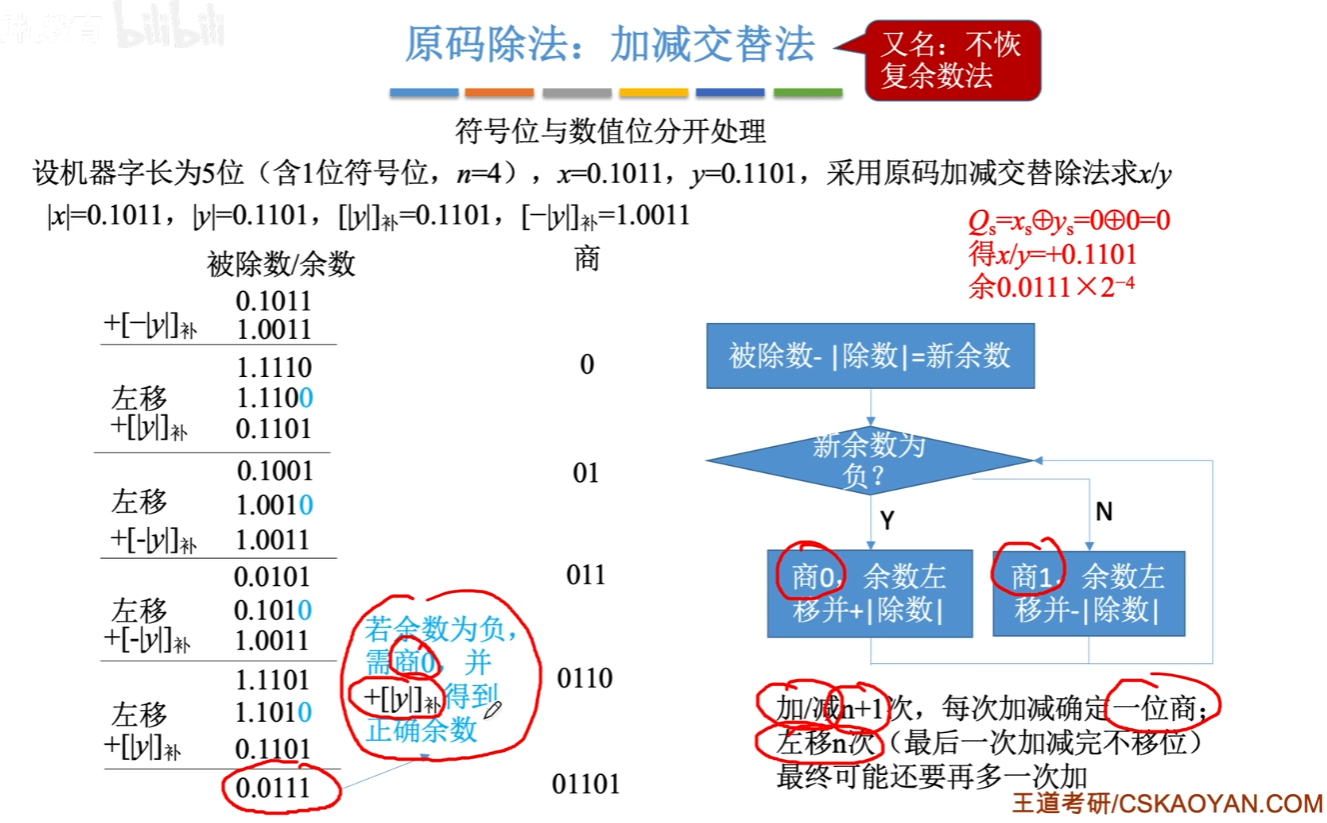

2.6.1.3、优化恢复余数法采用加减交替法(也称不恢复余数法)

**对于恢复余数法有没有优化的点呢?**如:若是余数为负,则可直接商0,并让余数左移1位再加上|除数|。

- 在这个过程里并没有恢复余数,而是直接跳到下一步,基于这种思路的原码除法,叫做加减交替法(不恢复余数法)。

额外补充:

注意:若是使用加减交替法,则需要加减n+1次,左移n次,若是最后的余数为负,则需要商0,并+[|y|]补得到正确余数。

扩展说明定点小数问题(被除数要<除数)

定点小数的除法运算,最终得到的一个商也只能是一个定点小数,而不能够是一个整数。因此在定点数的除法运算当中,我们会规定被除数一定要小于除数,若是被除数大于除数,最终商的结果一定会大于1,而定点小数无法大于1,对于硬件如何检查被除数与除数的大小关系呢?

- 主要是通过第一步的商来决定的,若是第一次+[-|y|]补得到的值为正数,那么就表示被除数是>除数的,此时硬件电路会直接停止运算,这种除法是无法使用定点小数来表示的。

- 若是为负数,则表示是正常的,此时则表示0继续往下执行。

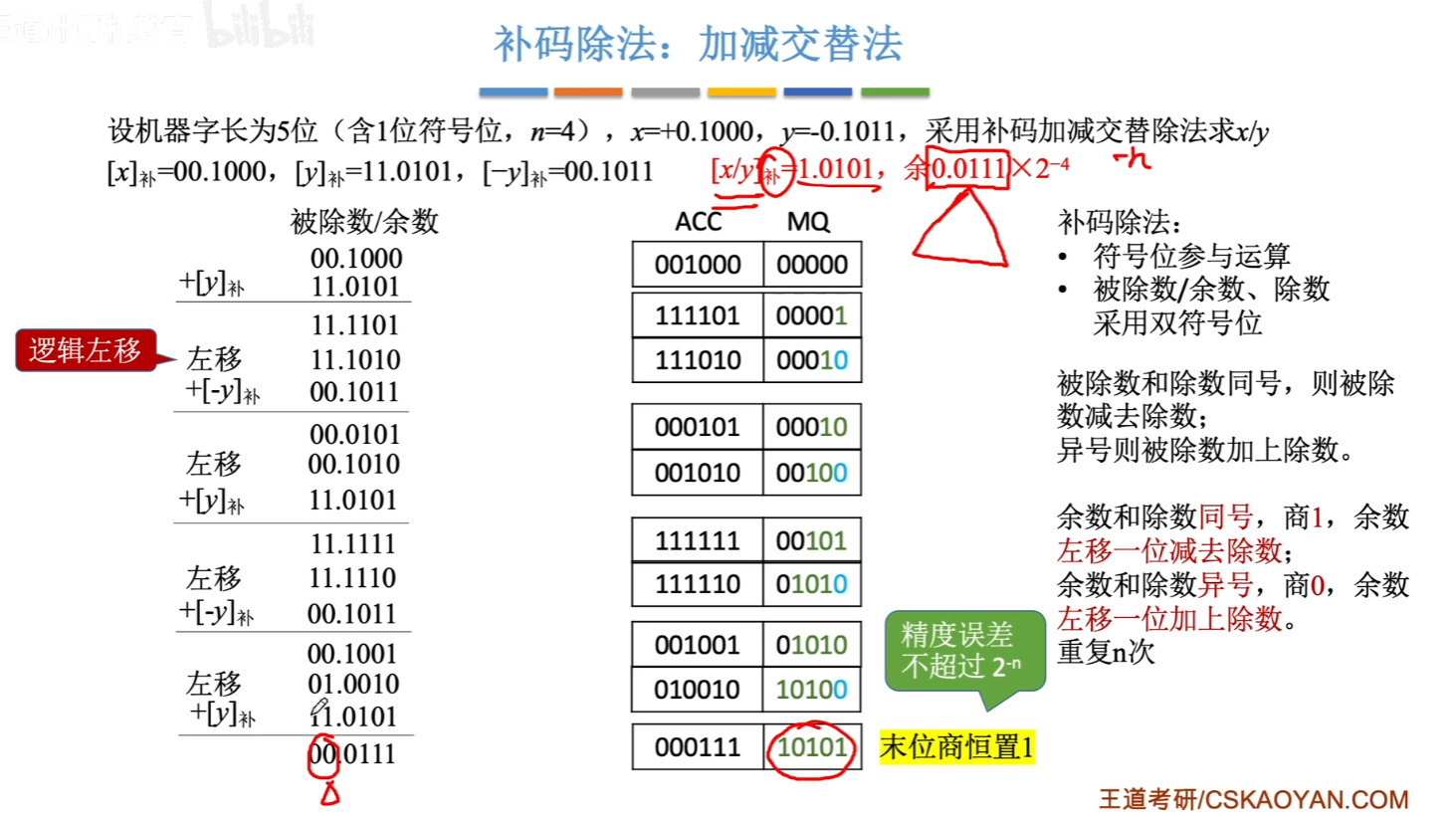

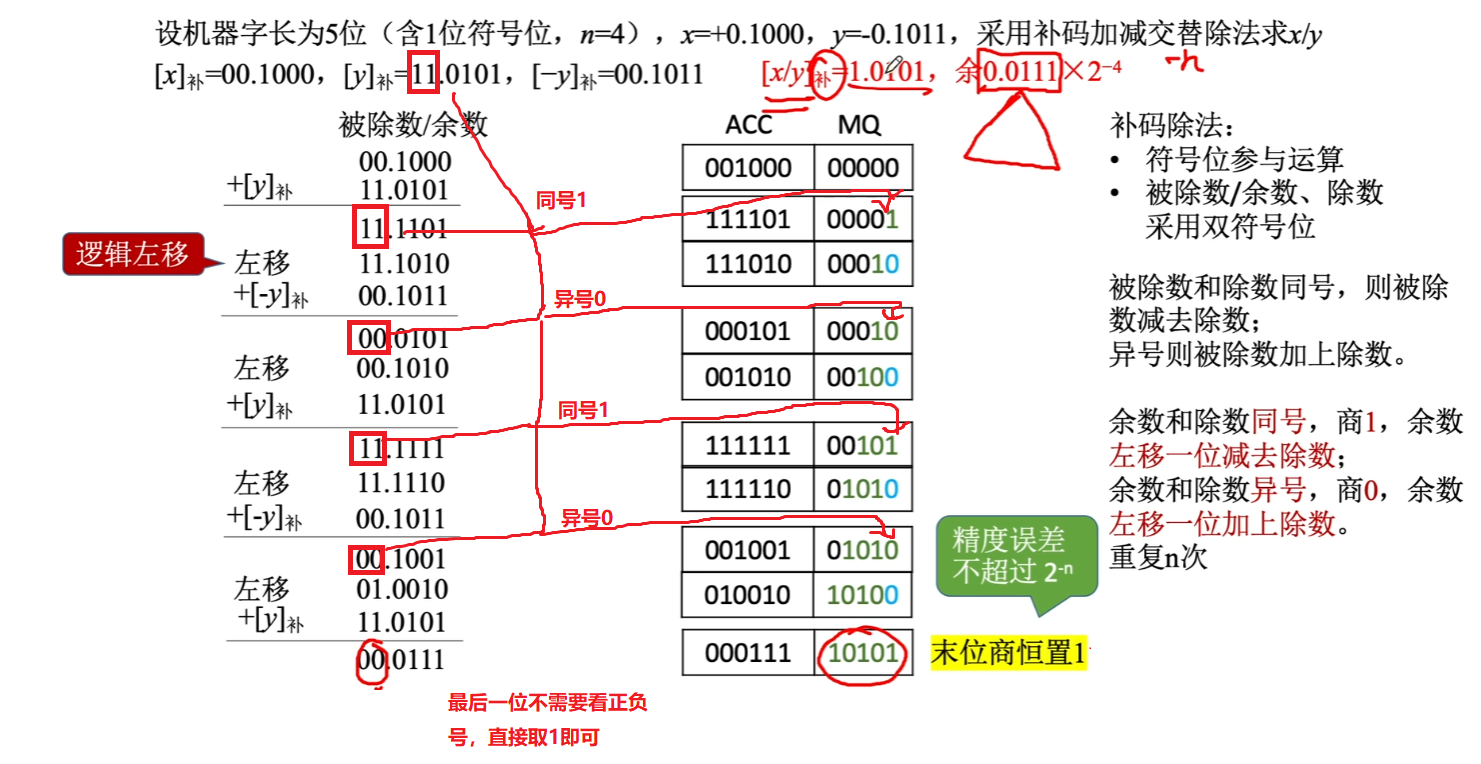

2.6.2、补码除法计算(加减交替法)

对于补码除法的细节点见如下的右边,包含补码除法的细节以及关于初始加减法及过程中商0/1情况:

注意点:

1、补码除法加减交替法与原码有些不同,初始加减是根据被除数与除数是否为同号,而对于商1还是商0,是根据余数与除数(这里除数指的是原本题目中的除数,而不是过程中的除数)。

2、最后一次左移加法完成之后,统一在最后末尾商恒置为1。这么做的目的就是省事,精度误差不超过2-n。

原码加减交替法与加减交替法的区别

2.7、C语言类型转换

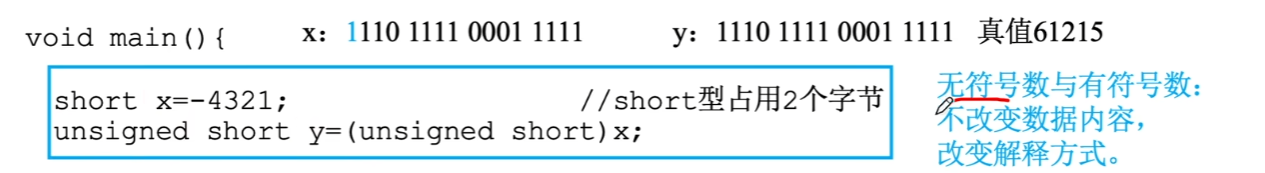

对于int、short、long都是采用补码形式来进行存储的,使用unsigned就表示是无符号数。

①short转unsigned short(无符号转有符号数同类型):也就是原本会把开头第一位看做是符号位,转为unsigned之后则不会将第一位看作是符号位

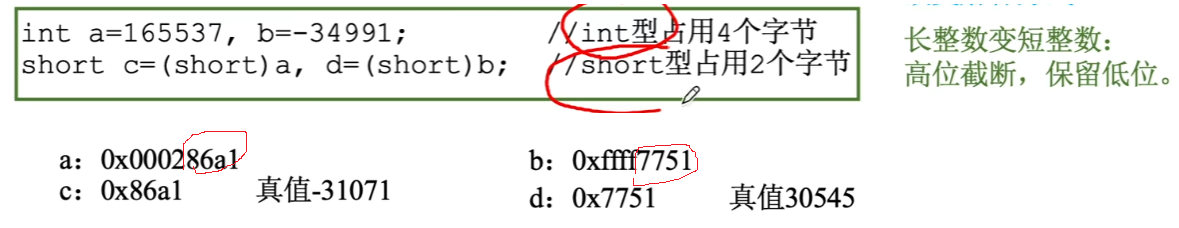

②int转short:也就是4个字节的转2个字节的,高位截断,保留低位

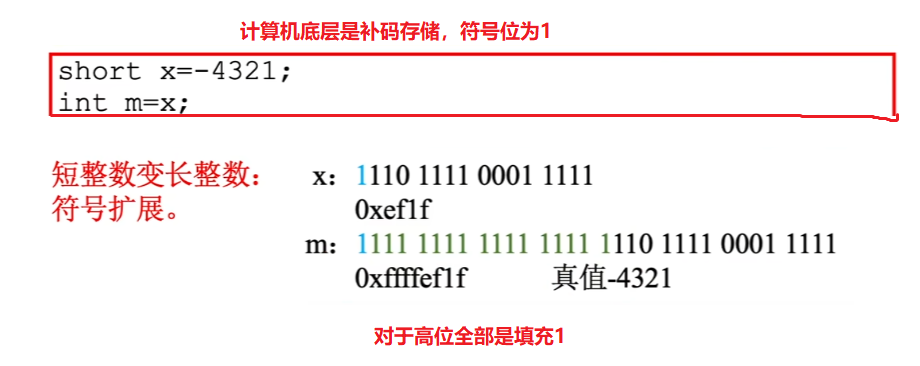

③short转int:2个字节的转为4个字节的

注意:对于定点整数补码来说若是一个负数,那么高位全部补1,若是为整数,高位全部补0。

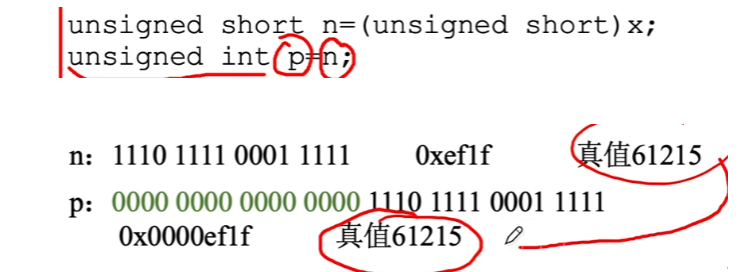

④unsigned short 转 unsigned int:2个字节的转为4个字节的

注意:在这里可以跟③有个对比,若是本身是正数,其符号位为0,那么高位也是填充0。

2.8、数据的存储与排列

2.8.1、大小端模式

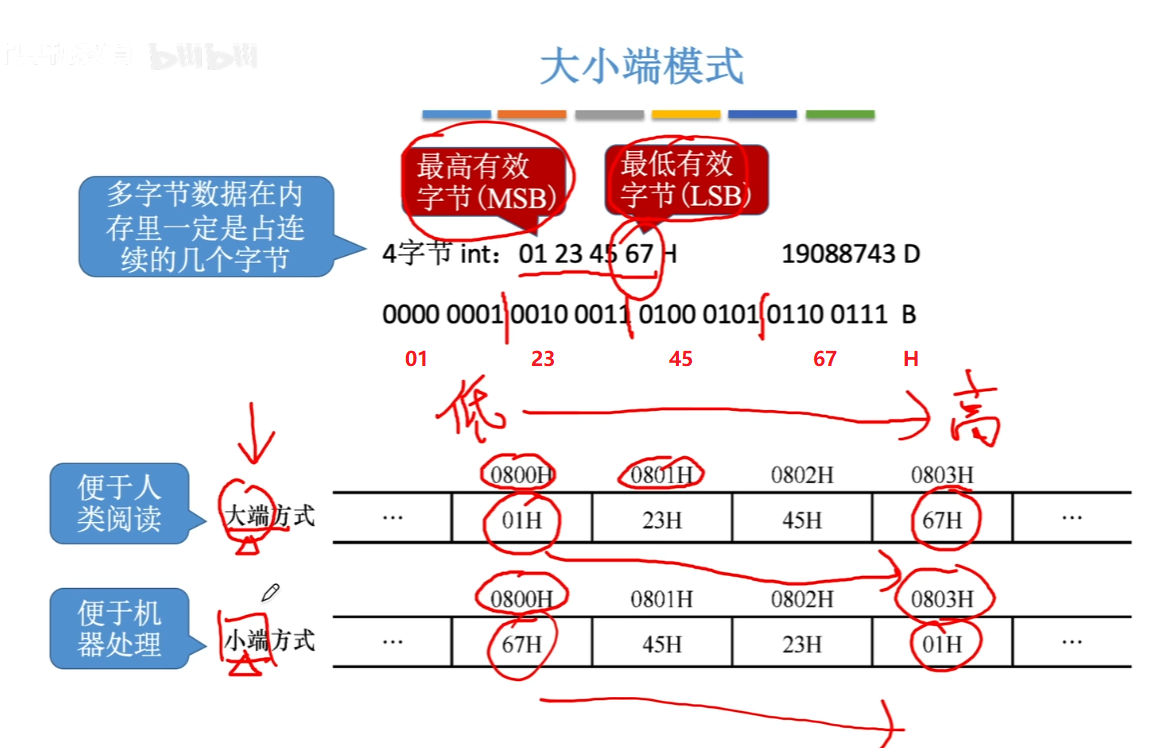

对于大小端模式实际上就是存储几个字内容的顺序不一样:

- 大端模式:从4个字节的从前往后依次存储在指定顺序的内存地址中。

- 小端模式:从4个字节的从后往前依次存储在指定顺序的内存地址中。

对于机器处理更适合采用小端方式存储的原因?

- 例如进行加法运算的时候,往常都是从低位开始进行运算的,而小端模式的存储方式就是从低位到高位存储的,读取是按照内存递增的顺序来进行的,所以很符合计算机的存储方式。

2.8.2、认识计算机编址

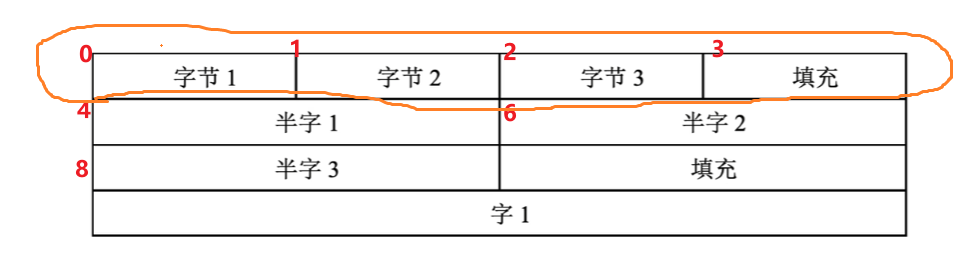

假设存储字长为32位,1个字就是32位,半字就是16位,每次访存可以读/写一个字,也就是下面画圈的一大部分32位,计算机是按照一个字节来进行编址:

若是按照字节来编址,给你说让你根据指定字来寻址,我们可以将字转换为字节然后确定具体位置:例如存储字长为32位,此时字就是32位,字节是8位,让你去找2号字,我们首先去将2转为二进制位10,接着逻辑左移2位即为1000,此时就相当于*4,从而来确定确切的地址位置。

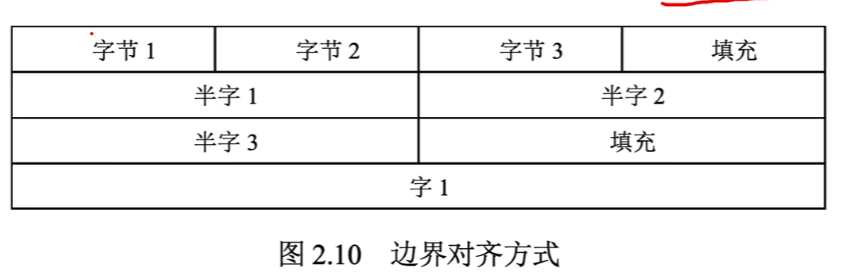

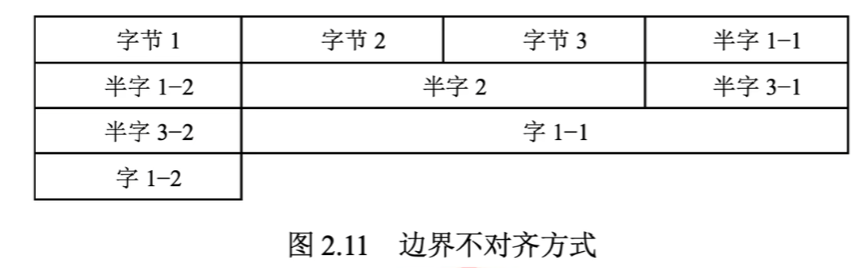

2.8.3、边界对齐方式与边界不对齐方式边界对齐

现在有一个场景:我们依次写入3个字节,接着写入3个半字,对于这种情况采用边界对齐与不对齐方式就会影响我们的实际存储方式。

边界对齐如下表所示:

- 由于一个字长为32位,此时一行相当于可以存储4个字节,按照上述场景,我们依次写入3个字节后,要写入一个半字,此时由于剩余的一行只剩余一个字节了,由于我们采用的是边界对齐方式,会将这一个半字写入到下一行当中。

边界不对齐如下表所示:

- 由于一个字长为32位,此时一行相当于可以存储4个字节,按照上述场景,我们依次写入3个字节后,要写入一个半字,此时由于剩余的一行只剩余一个字节了,由于我们采用的是边界不对齐方式,会继续存储到这一行中直至塞满这一行,此时这一行最后8位存储的是半个字。

为什么有两种方式存储呢?区别

- 采用边界对齐方式:空间换时间,若是读取上述的第一个字时,只需要访存一次即可,直接读取第二行。

- 采用边界不对齐方式:可以有效的利用存储空间,不浪费,但是对于我们要读取指定的一个字时,由于一个字拆分两部分一部分存储第一行最后,另一部分存储在第二行中,那么由于我们读/写是一个字一个字,此时就需要两次访存,时间开销就变大了。

三、浮点数的表示与运算

浮点数的局限性如下:

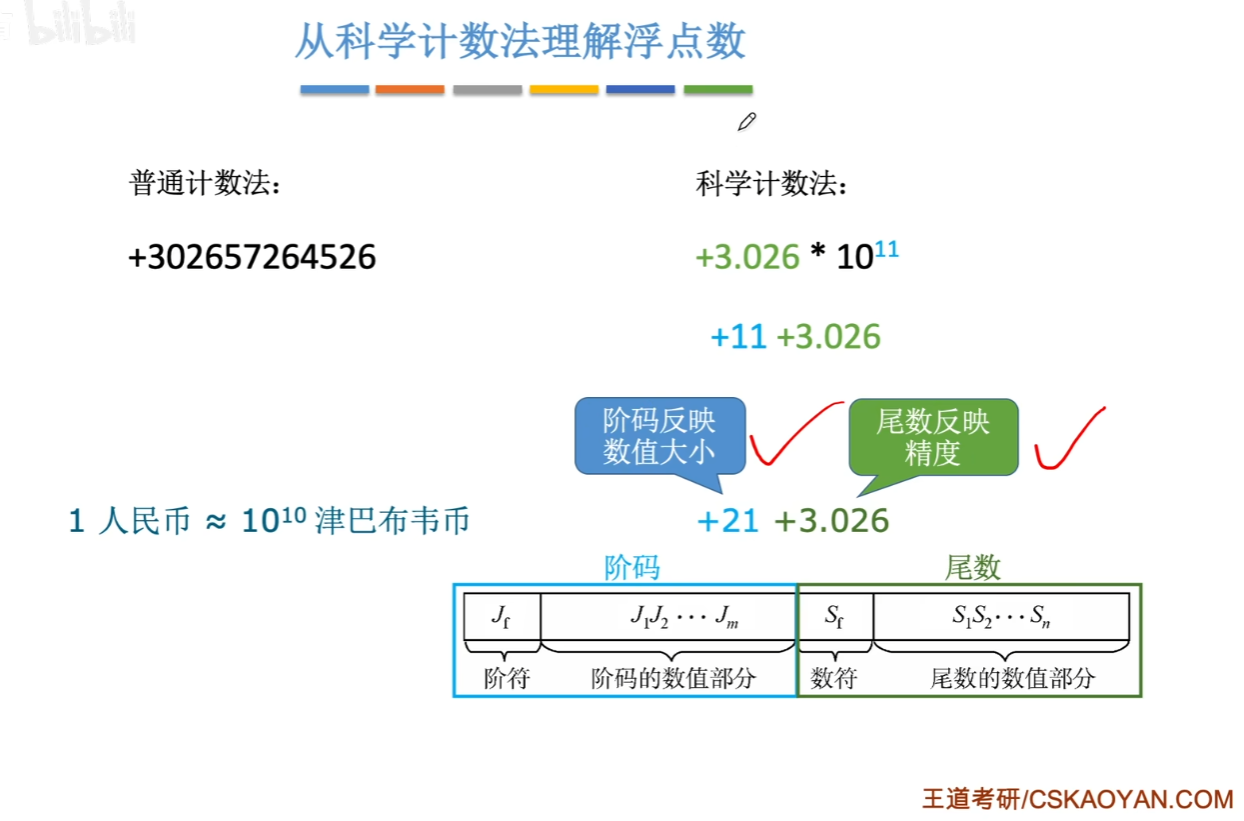

认识十进制的科学计数法:

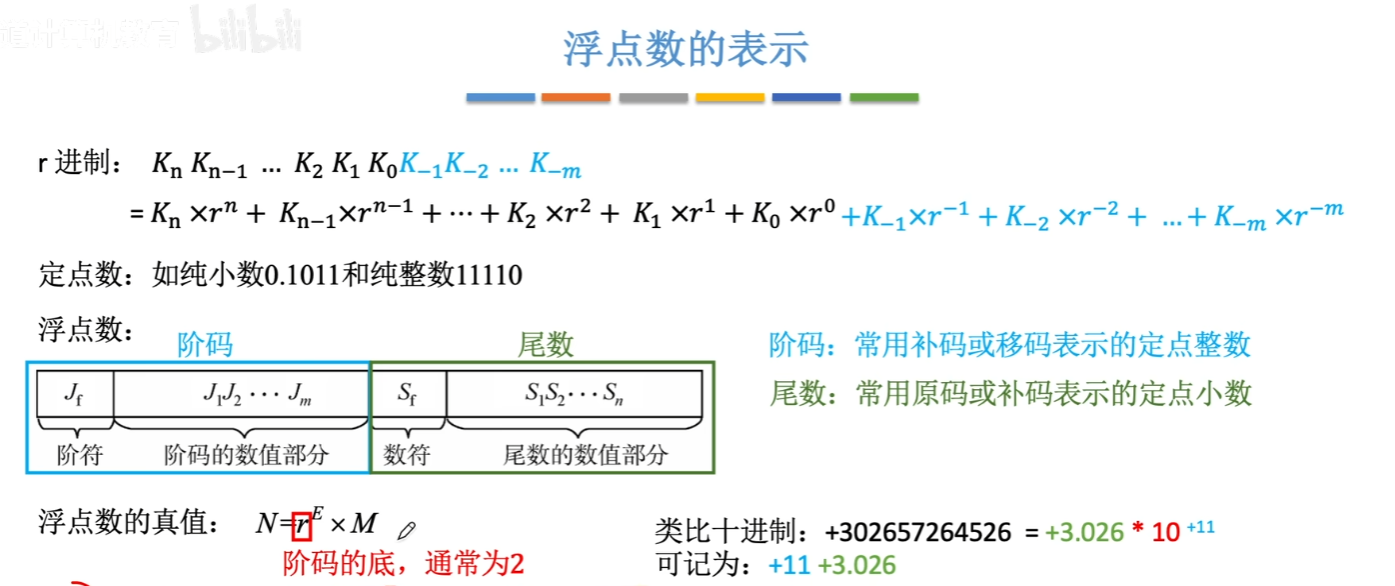

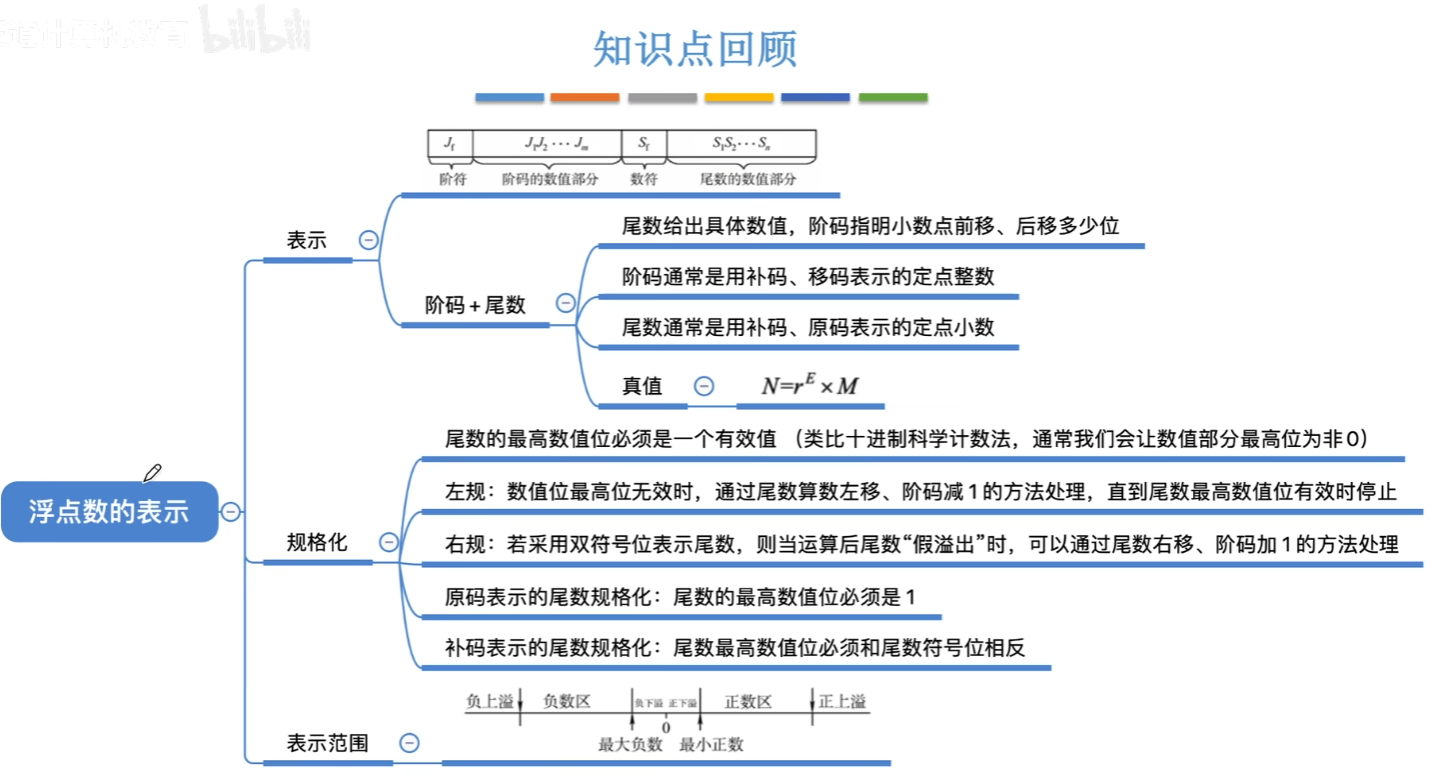

3.1、浮点数的表示

3.1.1、认识浮点数的表示

二进制的浮点数原理:

针对于阶码与尾数对应表示的含义:

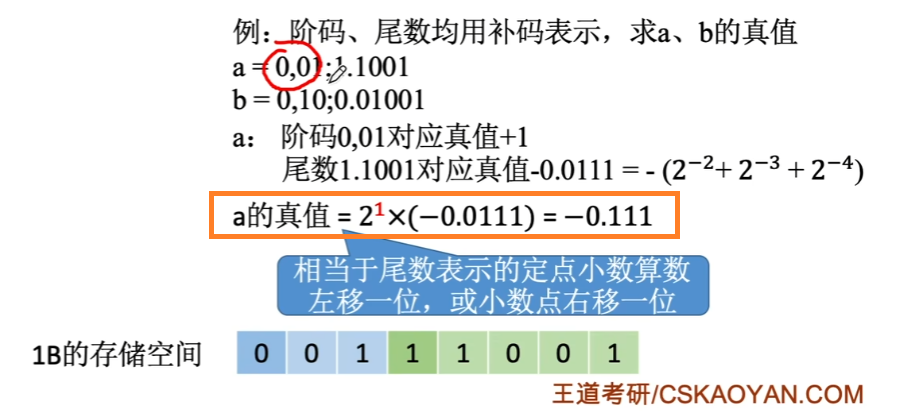

实际案例:根据给出的阶码尾数来表示求a,b的真值。

例1:

若是最后使用1B来存储a的真值,那么是正好可以表示的,阶码为001,尾数为11001,合并起来正好为8位。

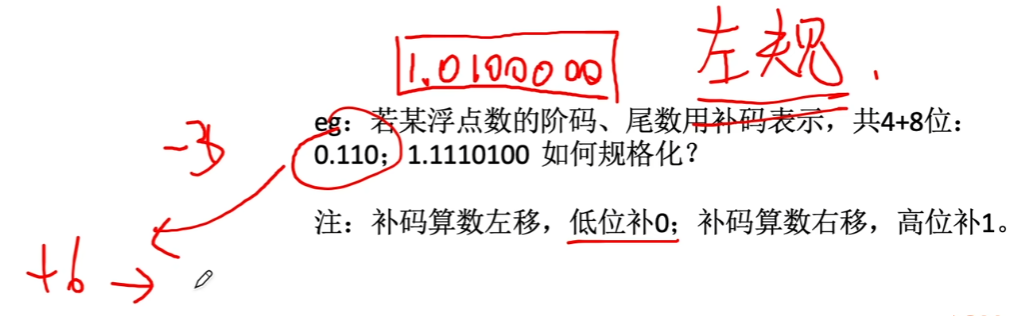

3.1.2、浮点数的规格化及示例

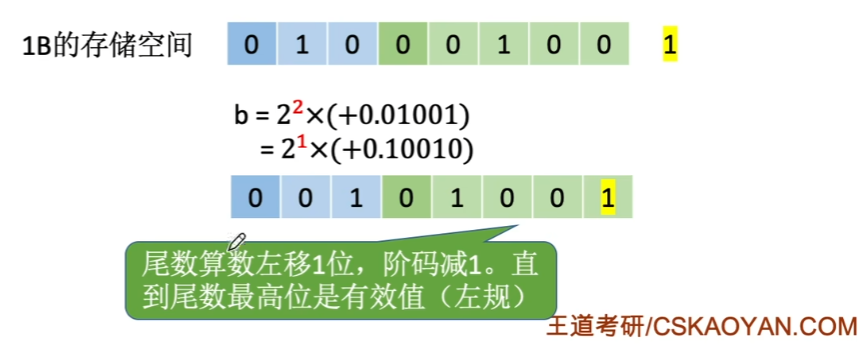

例2:引出浮点数尾数的规格化

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-FYGoQiAf-1685321272499)(https://pictured-bed.oss-cn-beijing.aliyuncs.com/img/2023/1/image-20230527155226344.png)]

介绍下十进制科学计数法规格化:

- 对于一个十进制位可以使用两种方式来表示,而最终表示应当为+3.026更为贴切,尽管另一种0.003也可以来表示,但是却丧失了精度。

- 科学计数法规定了最高位为一个有效值,不能为0,在尾数相同长的时候尽可能规定尾数的最高位不能为0。

接着回到例2:我们可以对尾数进行左移一位,此时阶码要减去一位。这样做的目的是让尽可能保留更多的精度

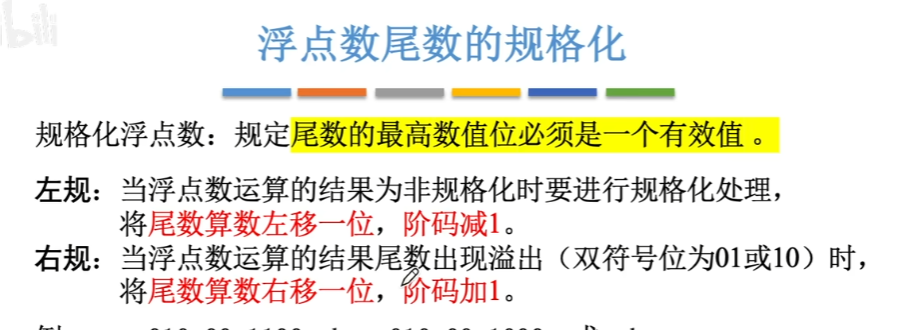

浮点数尾数的规格化:认识左规与右规

- 对于左规与右规使用时机要确定,当非规格化时需要进行算数左移,若是溢出才会是算数右移。

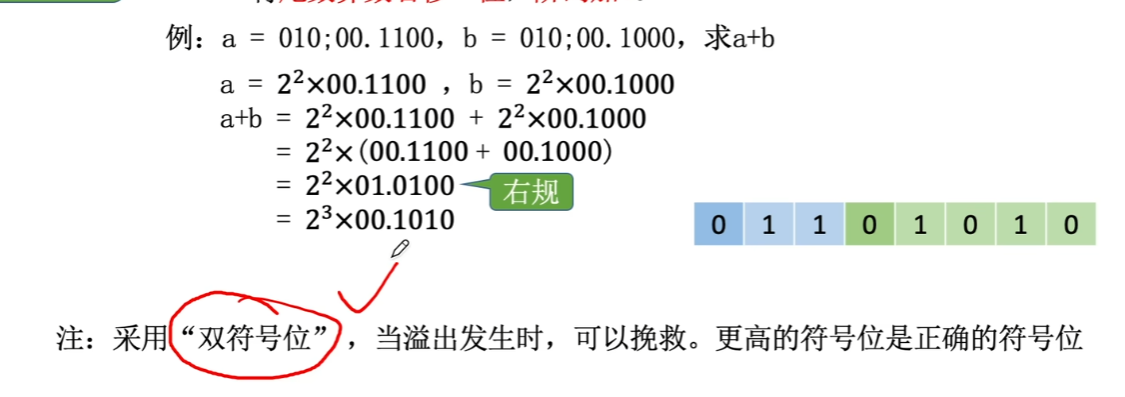

规划化示例:

尾数的符号位为01,此时采用右规,即可挽救溢出的情况。

3.1.3、规格化浮点数的特点

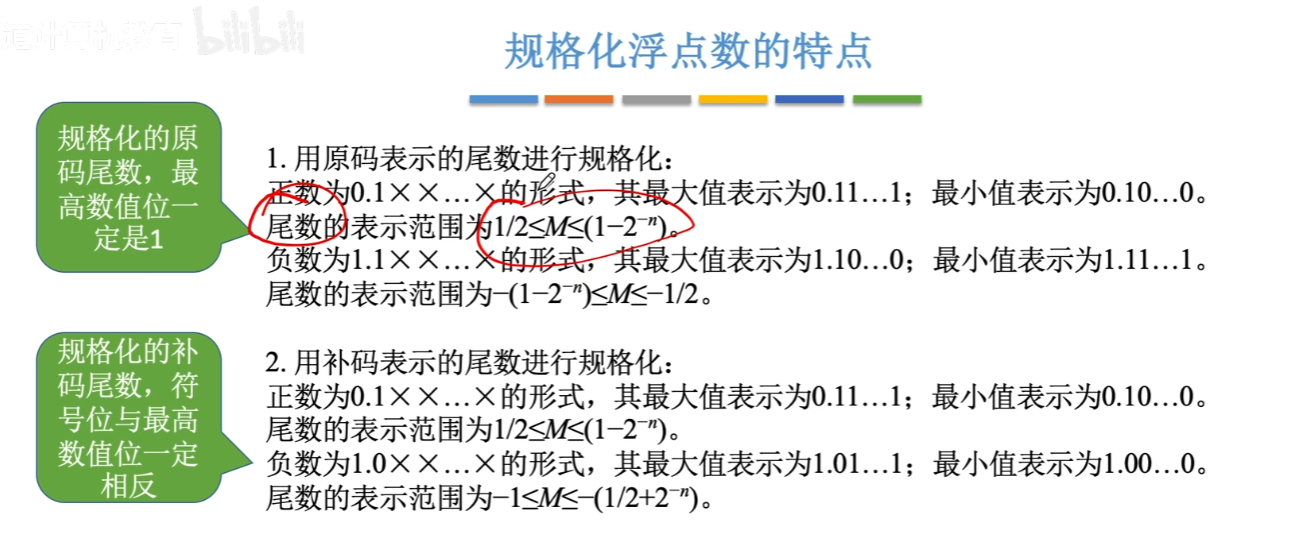

规格化浮点数的特点:原码、补码

注意:补码负数表示尾数进行规格化时要注意为1.01xxxx形式。

示例:下图中给出的1.1110100并不是规格化要求,因为其是负数补码,应当为1.01xxxx形式,所以此时需要进行算数左移。

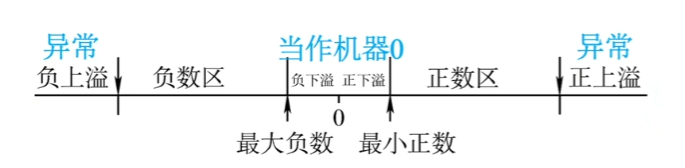

3.1.4、浮点数的范围

如下图:若是比0.00001还要小,那么此时可以表示为正下溢;而对于负下溢,若是绝对值已经超出了最小的范围即可表示。

知识点回顾

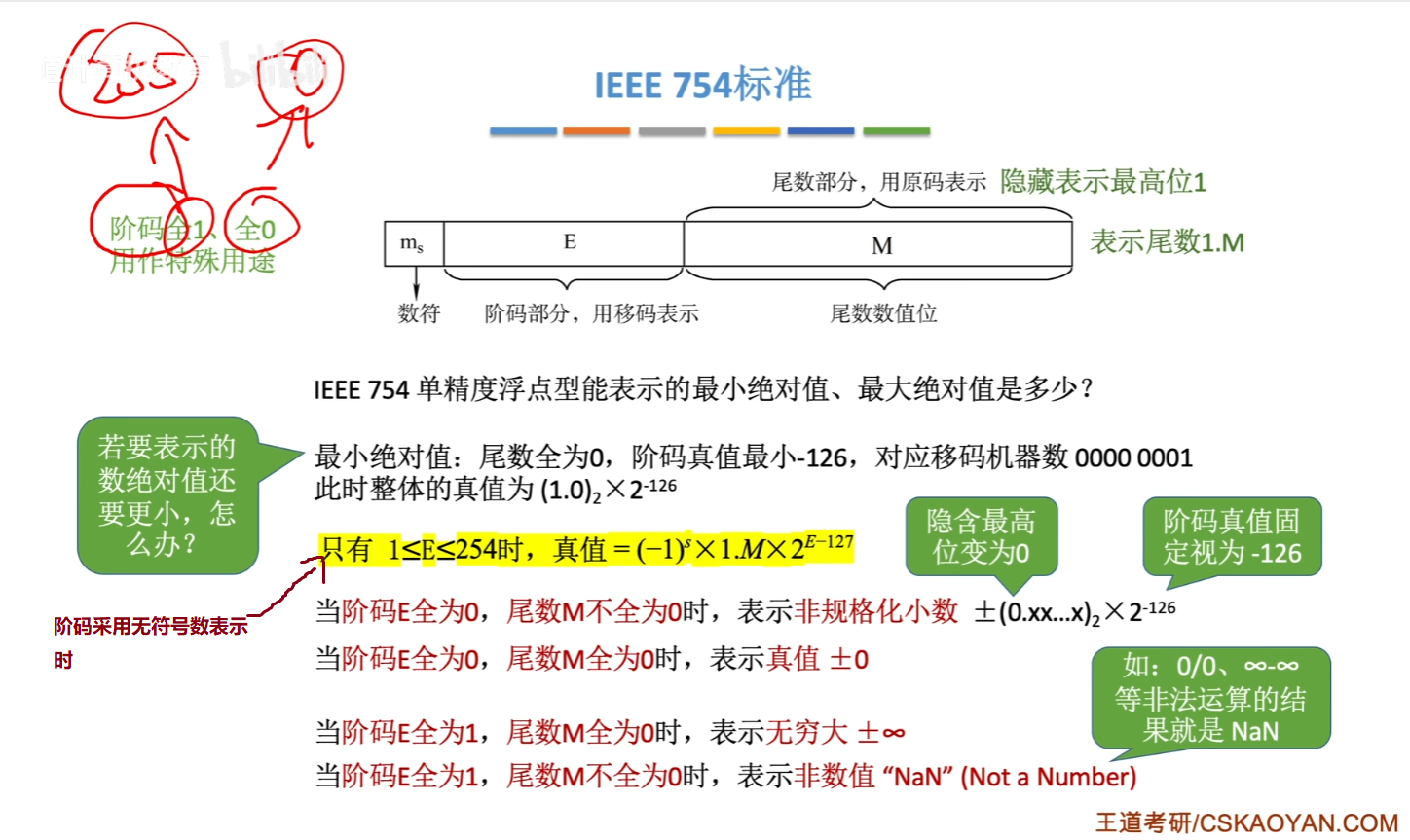

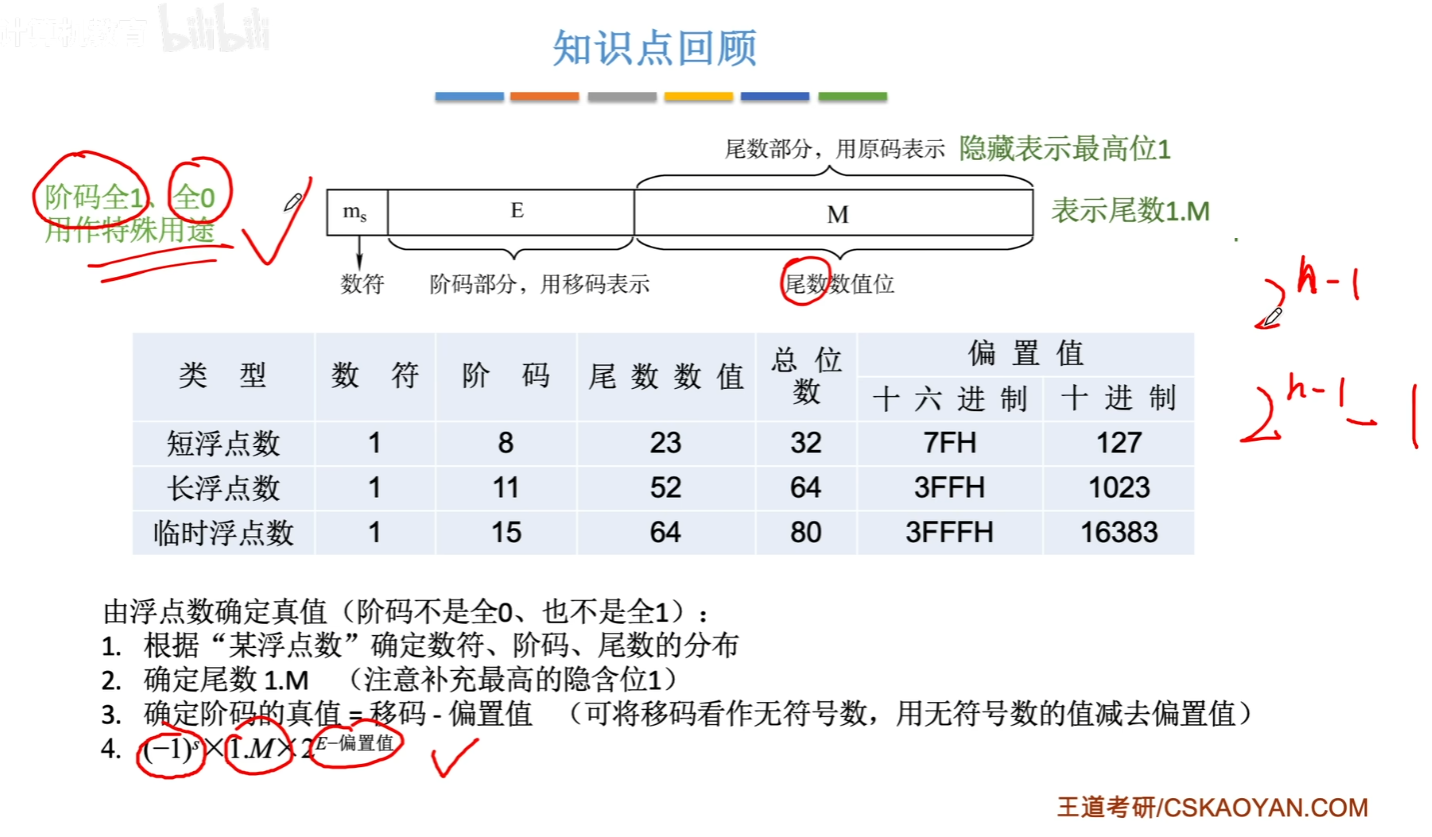

3.2、IEEE 754(浮点数标准)

3.2.1、IEEE 754中的移码表示与定义

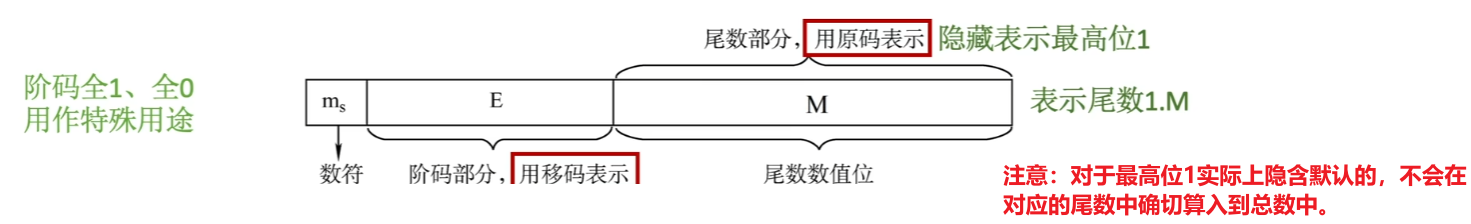

IEEE 754中阶码是采用移码来进行表示的:

- 注意移码只能够用于表示整数,这也是为什么阶码来用移码表示的一个原因。

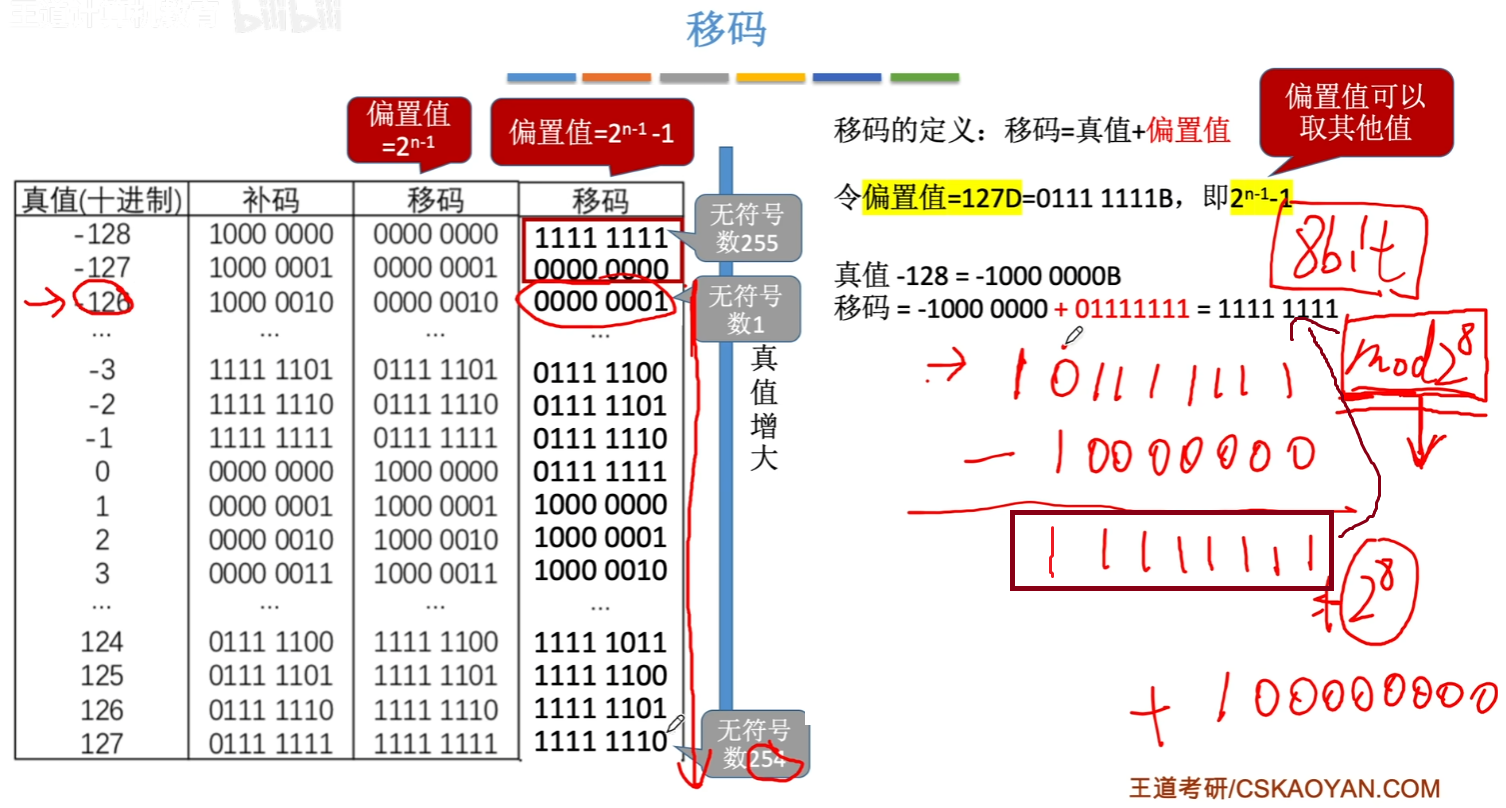

3.2.2、移码定义(偏置值为128、127情况举例)

移码最原生定义:移码=真值+偏置量(这里真值指的就是原码值)

下面举的例子尾数都是按照补码表示的:

①偏置值为128D情况

这里我们给出一组真值、补码以及移码,表中的移码可以通过我们上面的公式来获取:

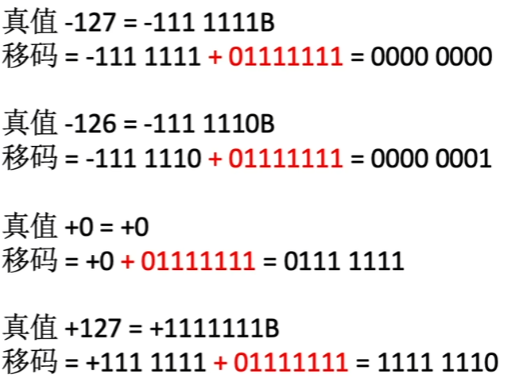

②偏置值为127D情况

偏置值为127D时左边表中最右侧的就是对应真值的移码,我们来首先尝试去计算第一个-128的移码,可以看到是一个减法计算,被减数<减数,此时我们可以多加一个位

- 该情况下的移码值如上图课件除了第一个数为255,下面的依次为1-254。

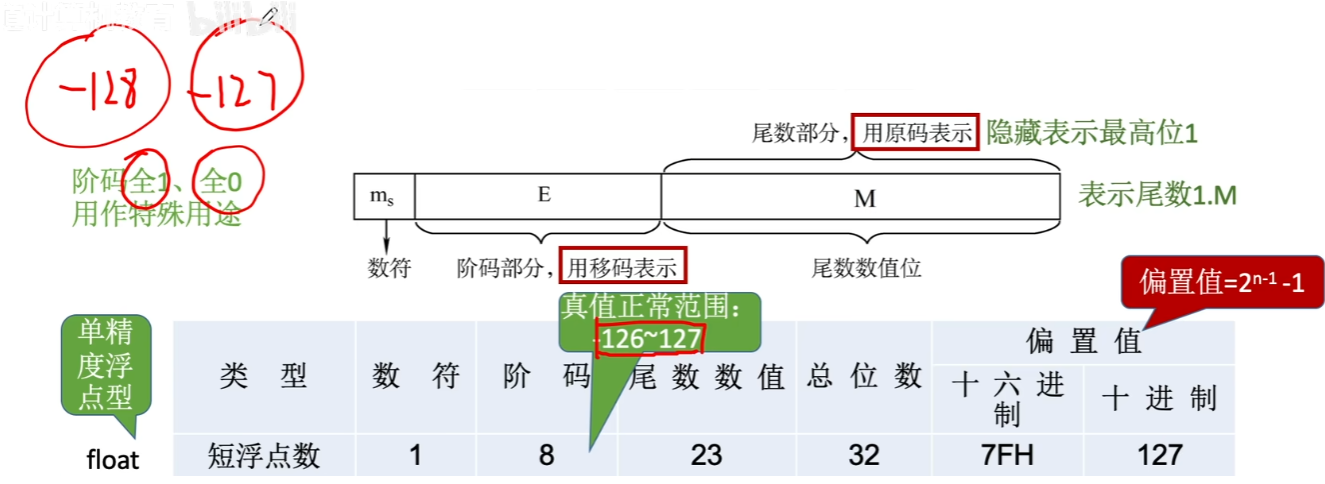

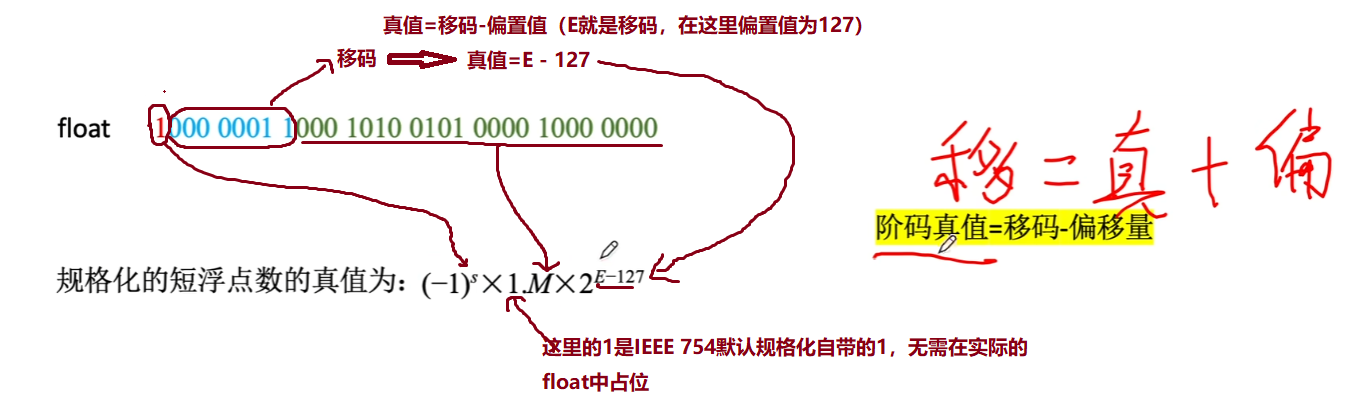

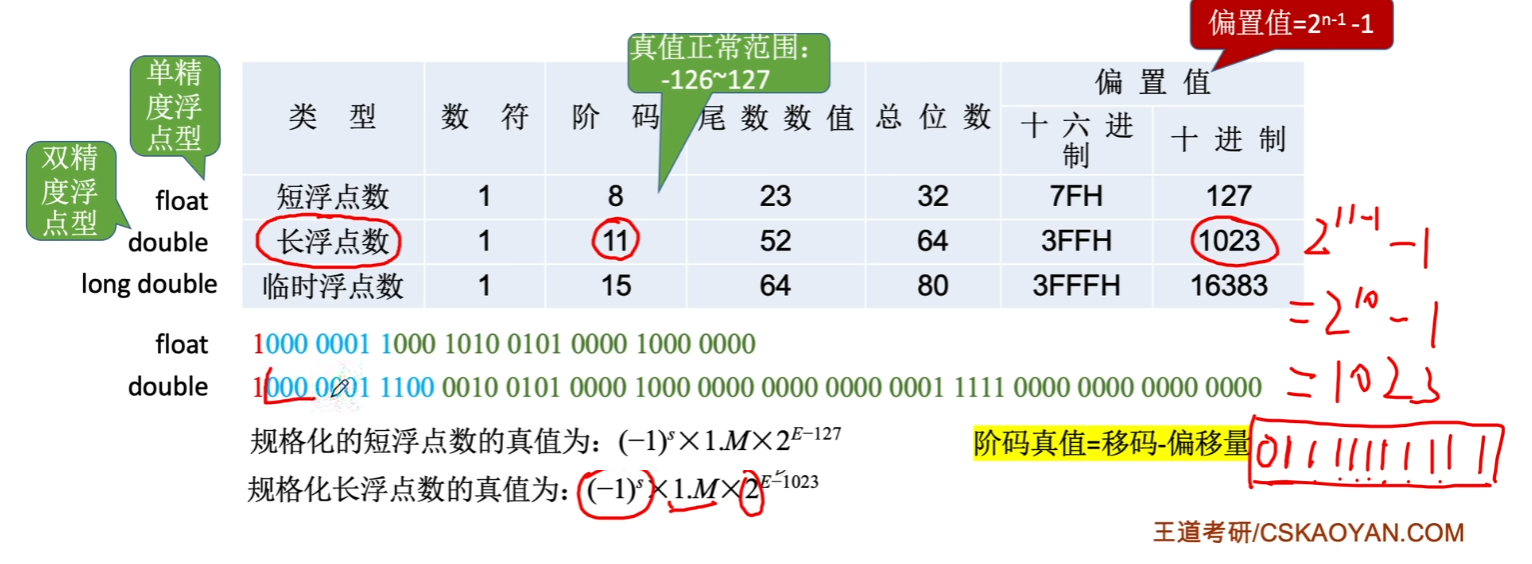

3.2.3、IEEE 754标准浮点数表示

在这里阶码是采用移码,尾数是采用补码表示的。

- 对于float中尾数数值为23位实际上指的是1.M中的M,这个1是默认就有的。

拿float来进行举例:

①其阶码真值范围是-126-127,是根据偏置值来决定的,少了的两个分别是全一的-128,全0对应的-127,这两个状态会用作特殊的处理。

- 可看下之前的图最后一列的第一第二行,全1或全0。

- 其中float十进制的偏置值怎么算?28-1 - 1 = 127。

我们来看一个规格化浮点数来求的真值的情况:

②double类型:

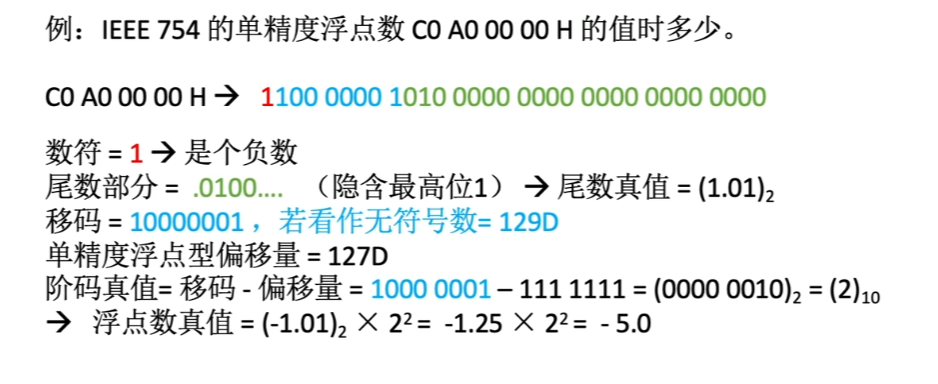

3.2.4、实际案例计算(真值与单精度浮点数相互转换例子)

1、给定真值,让你求单精度浮点数格式表示

- 由于IEEE 754对于尾数的整数部分隐含了1.,所以这里要转为1.xxxx。

2、给定单精度浮点数格式让你求真值

3.2.5、IEEE 754单精度浮点型多种阶码与尾数不同情况(最大值、最小值)

IEEE 754单精度浮点型能够表示的最小绝对值,最大绝对值是多少?

下面是多种阶码与尾数不同情况取得值:

知识点回顾总结

3.3、浮点数的计算

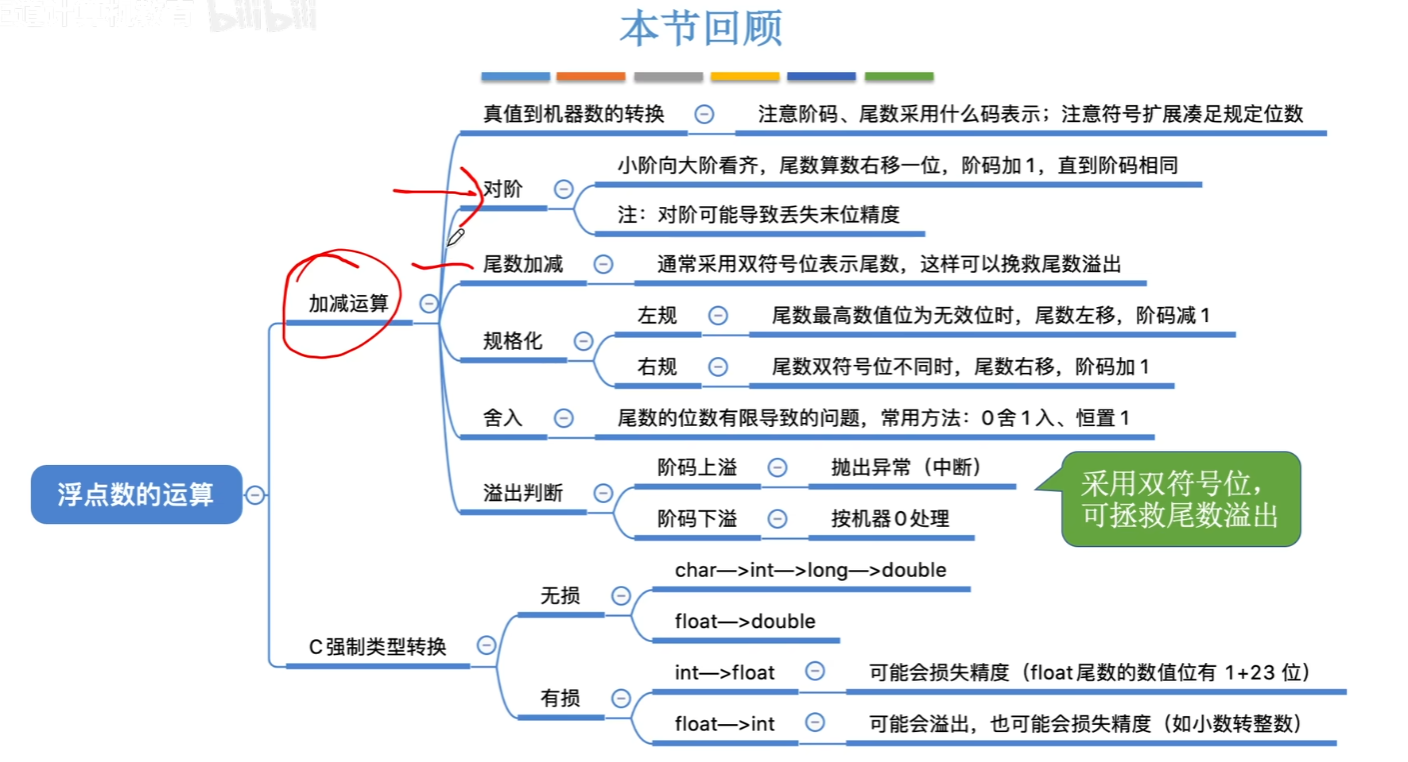

3.3.1、浮点数的加减运算

以十进制来进行举例步骤如下:

①对阶:小阶向大阶靠齐。

- 若是不向大阶靠齐,那么尾数部分的值就会很大,每大一位就是多占一个位置,例如原本的0.9854 x 105,若是阶数变小,此时就为985.4 x 102,此时你可以看到在尾数部分就直接多了三位,而若是仅仅只在阶数中呢?

- 这里原码表示下:原本为5就是101,此时为2也仅仅是10,此时少了一位却换来了多三位,肯定不好。这也是上述不向大阶靠齐的一个原因。

- 同样也方便计算机对尾数进行处理。

②尾数加减

③规格化:保证尾数的第一个数值位是有一个有效位。

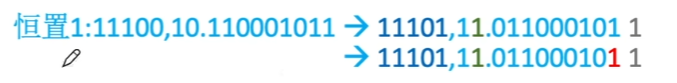

④舍入:尾数的比特位是有限的,在尾数加减截断可能尾数过长,所以需要进行舍入。对于舍入的策略有多种方式。

⑤判溢出:阶码超过指定范围则溢出。

注意:在第⑤步判断溢出时若是溢出,此时我们可以在③④步中进行拯救。

3.3.2、浮点数加减实际案例

浮点数的加减运算实际案例:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-oII0VATH-1685321272510)(https://pictured-bed.oss-cn-beijing.aliyuncs.com/img/2023/1/%E6%97%A0%E6%A0%87%E9%A2%98.png)]

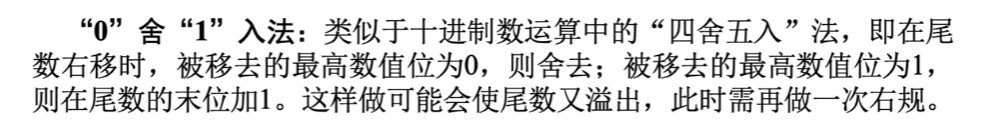

3.3.3、舍入情况

两种输入方式:

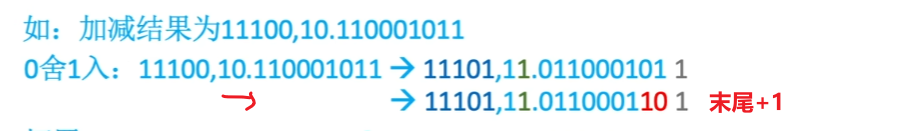

①0舍1入法

示例如下:对于下面示例是末尾+1,原本为01,+1之后为10

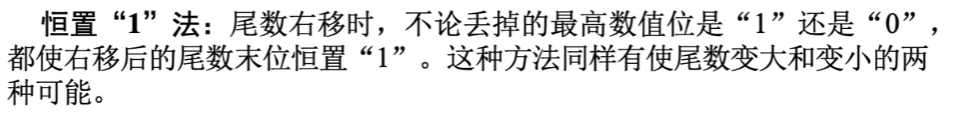

②恒置1法

注意点如下:

3.3.4、强制类型转换问题

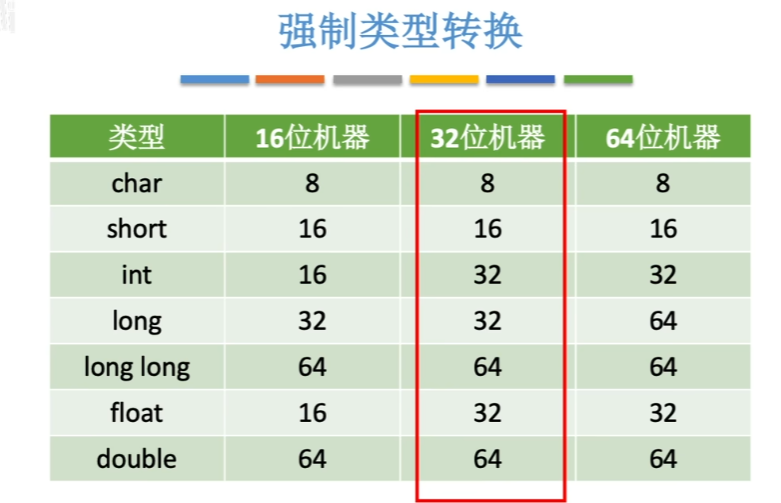

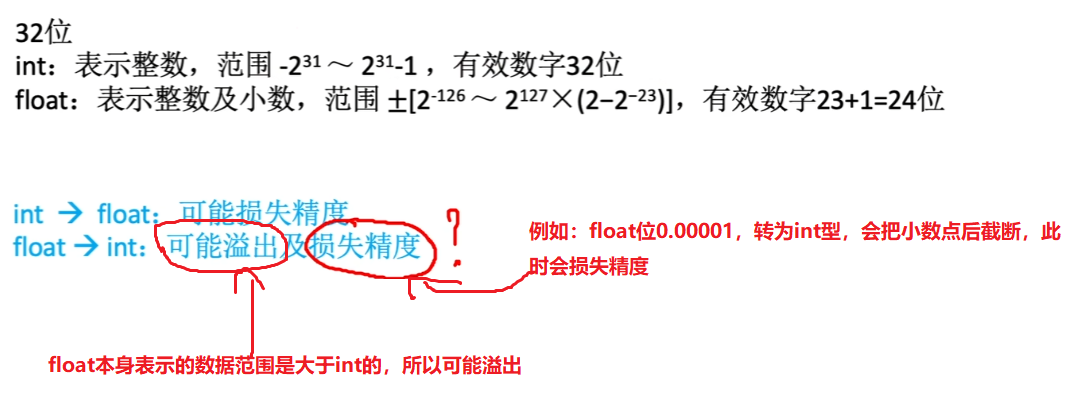

考试考察时大多是32位的,目前主流都是64位。

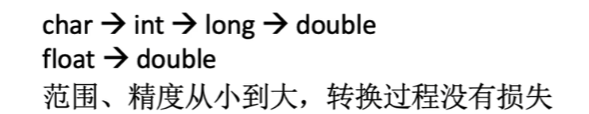

无损转换,数据精度不会丢失

int转float型会有精度的损失:其中int是1+31,而float是1+8+23,其中23实际还隐含了一位(可以表示1+23=24位)

本节回顾

整理者:长路 时间:2023.5.22-5.2