MSP430或STM32,在使用内部ADC出现的采样数据异常抖动问题

采样设计:

用于检测供电线路电流及电压。

产品运行在两种模式下,1、低功耗静态模式(仓储态),2、全功能全速运行模式(工作态)。

在仓储态下,所有外设均处于关闭状态,MCU也处于低功耗模式下(如MSP430处于LPM3模式,STM32处于STOP2模式下),仅保留低功耗定时器及ADC,ADC处于低速运行状态,检测的是工频信号,在一个工频周期内检测8个点的数据,每隔2.5ms采样一次。外部采样通道也通过MOS管进行开启关闭。

ADC转换器内部图:

问题1.ADC多通道连续采样,采样值异常波动

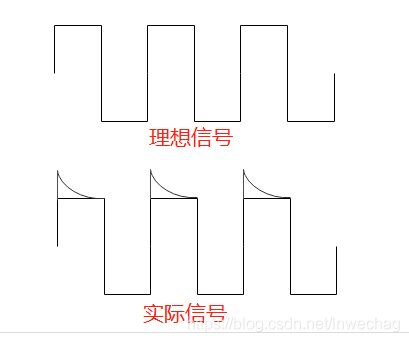

当MCU需要多通道连续采样时,ADC从设置的通道开始顺序采样到通道结束,其内部使用的是一个ADC进行对不同的采样通道的切换,在切换过程中,不可避免的需要对ADC内部RC(Cadc)进行充放电,此时就存在一个隐蔽的问题。

若不同的采样通道之间的采样幅值不同,如CHANEL1的信号为3.6V的电池电压,CHANEL2的信号为1V基准的交流信号,CHANEL3的信号为3V左右的温度信号。此时ADC先采样CHANEL1,完成后将结果写入结果寄存器,紧接着采样CHANEL2,再采样CHANEL3。

这个过程中,当不同的信道接入ADC时,外接待采样信号会通过RC回路进行充放电(这个过程需要一定的采样保持时间设置),sample and hold time越长时间,Cadc的电压值与待采信号值越一致,采样结果越准确。但增加该时间则增加相应的时间及功耗。

产品在运行过程中出现的问题也基于此。在运行过程中,偶发异常的采样到与实际值偏离较大的数据,采样的交流信号产生了失真,计算出来的值也发生了跳动。

原因在于:由于通道1连接的电压为3.6V,而通道2连接的信号低于1,在采样完成CHANEL1时,ADC自动切换到CHANEL2,此时由于采样保持时间设置较小,ADC的RC还未放电完成,由较高的电压信号切换到较低的电压信号,RC未完成放电,导致最后的采样结果出错。但其实该种情况也不会必现,MCU差异性导致批量的产品中只有部分会出现该问题。

相同的道理,如果相邻的通道,CHANEL2电压信号较低,CHANEL3的电压信号较高时,也可能产生ADC的Cadc未完成充电,采样得到的值也不准确。

解决方法:1、增加采样保持时间。2、在电压信号相差较大的信道中间,增加对基准电压的采样,使信号处于平均值,在切换通道时不会因为充放电不及时导致数据错误。

问题2 对MOS管控制的周期开关的通道进行采样,异常检测到有信号

试产的产品部分出现ADC采样的信号呈下降趋势,如2080,2070,2060,2055,2048,2048,但待检信号无异常,信号源无明显抖动。

由于功耗的限制,对于某些采样信号的通道无法长时间开启着,需要通过MOS来通道开启和关闭,通过定时器对其周期性的开启测量计算。

原因:在开启MOS管时会产生一个冲击信号,需要较长的时间稳定,由于器件的一致性差异,稳定的时间也略有差别。在设计时,设计为执行开启后60ms再去进行采样,部分产品就会检测到异常值,导致计算出现偏差,产品运行状态也出现偏差。

解决方法:增加等待时间,开启通道后,等待80ms再进行采样,采样数据无误。

STM32 ADC采样异常 采样发生抖动

同样在设计阶段,产品在低功耗状态下的采样无异常。产品逻辑是在采样计算到交流信号时,唤醒MCU外设开启工作。

在第二次试产时,出现了部分设备,在无外部信号时,也采样计算到了数据,导致运行状态发生错误,体现在静态功耗异常。从外部基准电源、工作电源、待检信号来查,其纹波均较小无异常,但ADC还是采样到抖动数据。

产品设计在定时器LPTIME中断里2.5ms周期触发开启ADC转化,随后MCU进入STOP2模式。

问题:采样到的数据,偶发的出现一两个点的跳动,如2048,2048,2048,1750,2048,2048,通过计算后,判定为检测到外部信号,唤醒了MCU及其外设,导致功耗异常。

但是通过JLINK调试就不会出现ADC采样异常。

通过更换MCU可以解决问题。

切换到外部ADC采样芯片时,不会出现抖动

MCU高速运行时,不会出现抖动

通过询问技术支持,1、输入阻抗不匹配 2、采样电容没充饱。(回到第一个问题了)

在更改程序,增加采样保持时间后,修复了部分异常设备。但依旧有部分设备异常。此时采样保持时间已加到最大,也无法解决该问题,且通过更换MCU可解决问题,又怀疑到硬件设计上来。。。

原因:

由于产品设计,在LPTIME中断里开启ADC采样,随后退出中断后立即进入STOP2模式,以降低整机功耗,使其运行在超低功耗状态下,此时MCU主频为4MHz。在测试过程中将采样保持时间开启到最大,但在实际运行过程中,ADC的时钟是与SYSCLK时钟一致的,在退出LPTIME的中断后MCU进入了STOP2模式,此时SYSCLK是被关闭的,ADC时钟也被关闭了,再多的采样保持时间也会停止不运行采样了。

解决:开启ADC->DMA中断,在触发ADC采样后,等待DMA传输完成中断(即等待所有ADC通道都采样完成),再进入STOP2模式。此时保证了设置的采样保持时间有效执行。但随即也引入了静态功耗增加的问题,为该处等待,功耗增加10uA。

总结:

在多次试产过程中,总会出现各种奇奇怪怪的问题是在设计和准备样机过程中无法发现的问题。在设计包括准备样机的过程中,会对所用的器件一一进行筛选,且数量较少。当批量生产时,由于器件一致性差异,生产过程的老化破坏,操作人员的黑盒操作,都会使问题逐一暴露。所以一个产品在真正批量供货问世前,必须经过至少3轮的试产试运行,才能保证问题基本在厂内消灭。

————————————————

版权声明:本文为CSDN博主「lnwechag」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/lnwechag/article/details/106250656