阻抗控制(二)

1.差分阻抗控制

我们平时所说的差分阻抗是奇模阻抗的两倍。现在研究 差分线之间的间距对差分阻抗的影响。总的来说,随着差分线之间距离的增大,差分线之间的耦合逐渐 变弱,对共模干扰的抑制作用会减弱,阻抗变化的程度和信号线到地平面之间的距离有很大关系 。现在研究以下三种介质厚度下,差分阻抗随信号间距的变化趋势。

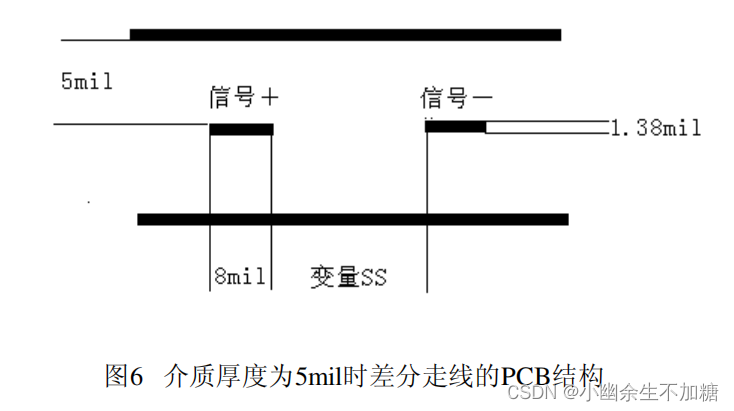

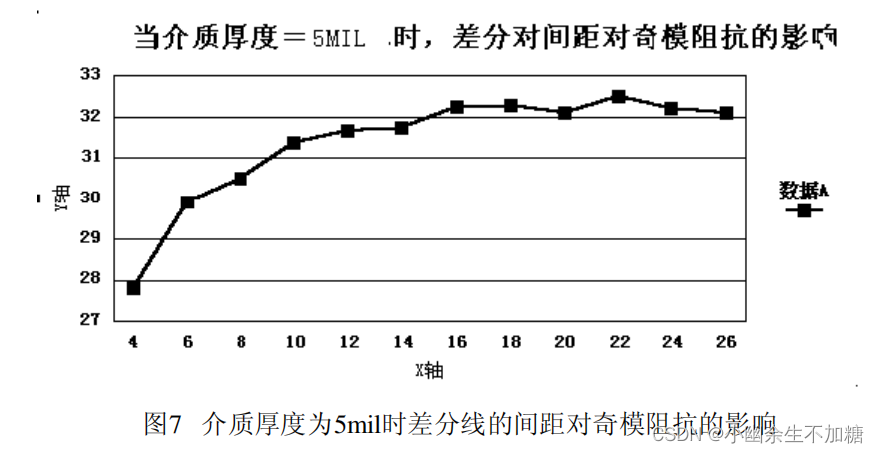

1.1 当介质厚度为5mil时的差分阻抗随差分线间距的变化趋势

差分线的PCB结构如下:

由上面的曲线可以看到在差分线之间的间距从 4mil变化到26mil这样大的一个变化范围内,奇模阻抗只减少了4个欧姆,最后稳定在32欧姆左右,原因是因为信号线到地平面之间的距离较小时PCB走线的大部分磁力线通过地板进行耦合 ,所以两个信号线之间的耦合相对较弱 ,信号线之间的间距对奇模阻抗的影响较弱。

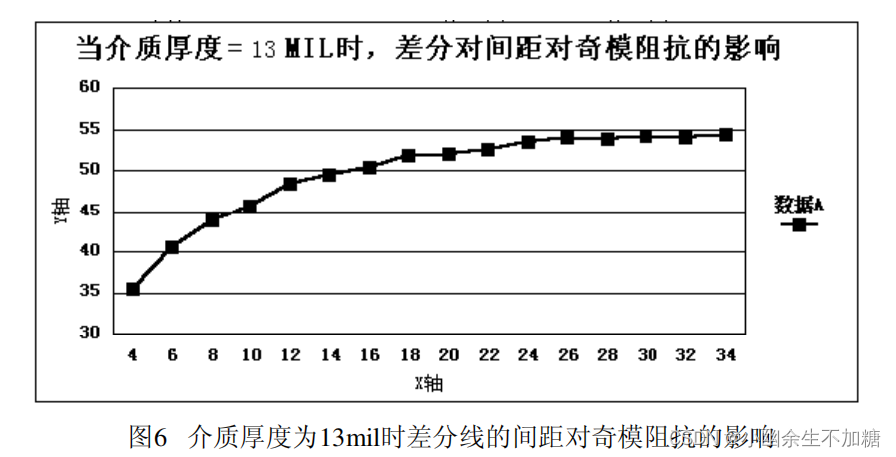

1.2 当介质厚度为13mil时的差分阻抗随差分线间距的变化趋势

差分对走线的PCB结构图如下:

由上面的曲线可以看到在差分线之间的间距从 4mil变化到34mil的时,奇模阻抗从35欧姆增大到55欧姆,变化了20个欧姆,和当介质厚度为5mil时相比,由于为信号线到地平面之间的距离增大,两个信号线之间的耦合成分逐渐增大 ,已经和地之间的耦合相比拟 ,所以信号线之间的间距的变化对奇模阻抗的影响相对较强。

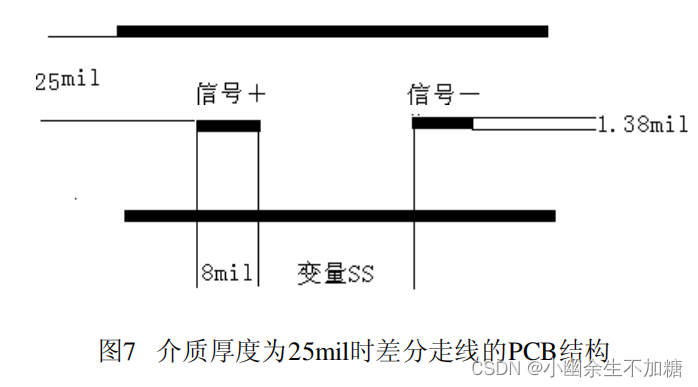

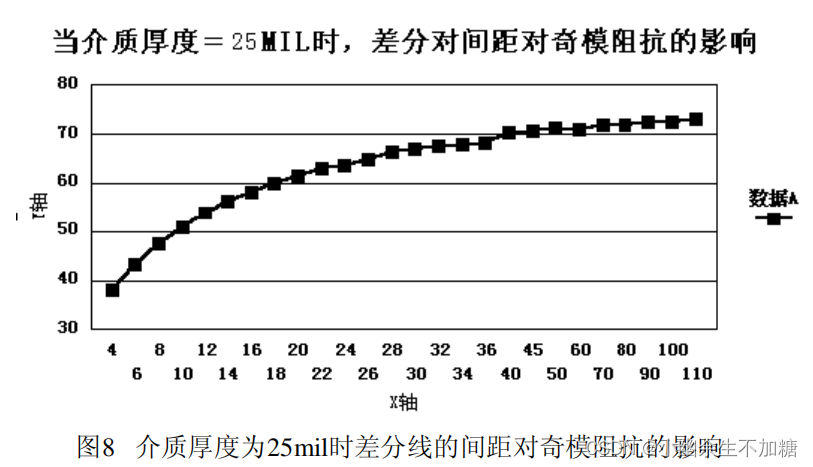

1.3 当介质厚度为25mil时的差分阻抗随差分线间距的变化趋势

由上面的曲线可以看到由于信号 线到地平面之间的距离增大到25mil时,差分线之间的耦合对整个磁力线的分布已经起者决定性的作用,尽管两个信号线之间的间距增大到30mil,接近线宽的4倍,但由于两线之间的耦合还是使阻抗减小了 10个欧姆。所以当信号到地板的距离较大时,一定要重视差分线之间耦合成分。

可以看出,在信号线离地较远时,差分信号对共模干扰有较强的抑制作用 并且降低了信号的共模辐射程度。对于高速信号线,尽量选用差分信号,可以有效减小EMI影响。

2.屏蔽地线对阻抗的影响

在实际的设计中,经常在关键的信号线两边 各加一条地线(guardline)。目的在于为关键信号提供一个低电感的地回路,从而减少相邻线之间 的串扰与传导、辐射的影响。但增加了地线的同时,也改变了信号的电磁场分布,降低了信号线的阻抗。

2.1 地线与信号线之间的间距对信号线阻抗的影响

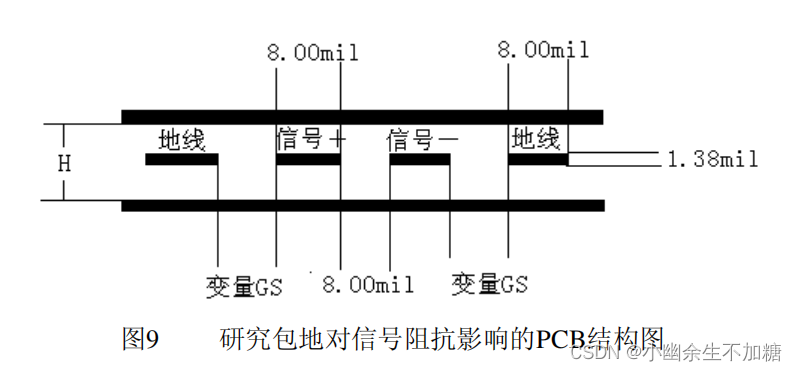

为了研究屏蔽地线对信号的影响 ,我们设置如下 PCB走线结构。该结构为标准的对称带状线,信号十、信号一为差分信号的正负 走线,两边为包地线,现固定信号走线的线宽为8mil,正负信号之间的间距为8mil,两个地板之间的间距为12.50mil或51.18mil。PCB结构图如下:

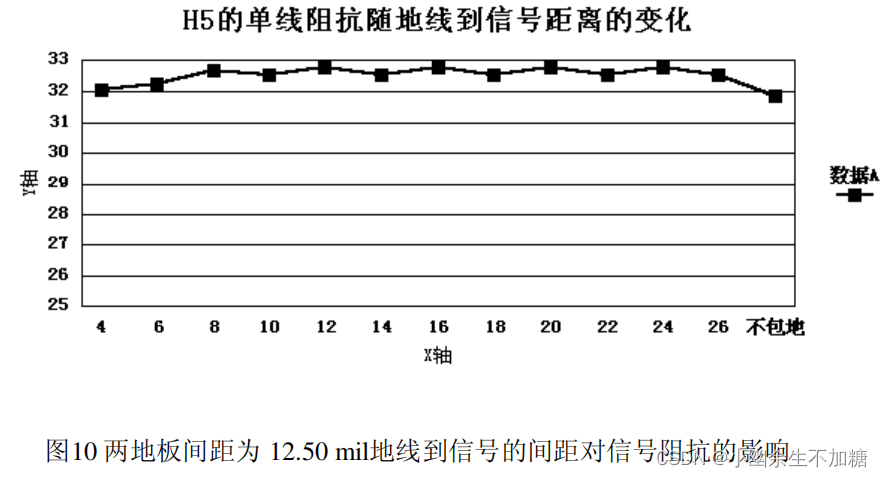

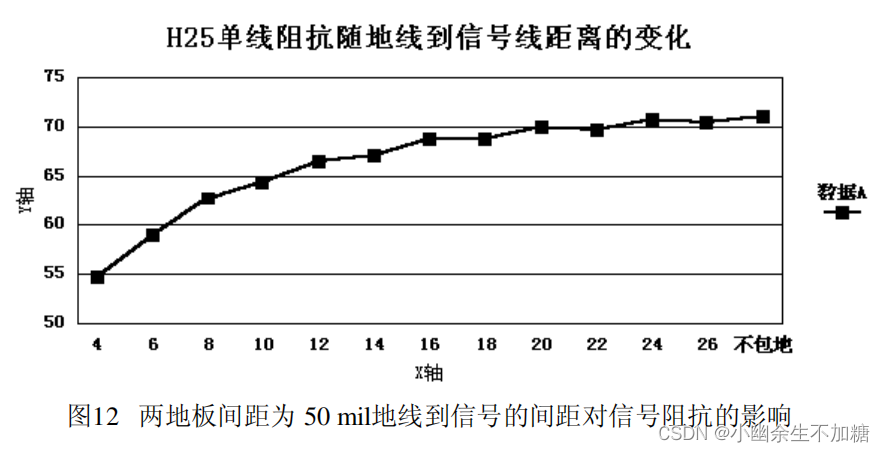

当两地板间距= 12.50 mi时,阻抗随者地线到信号线之间的间距变化的情况见下图。

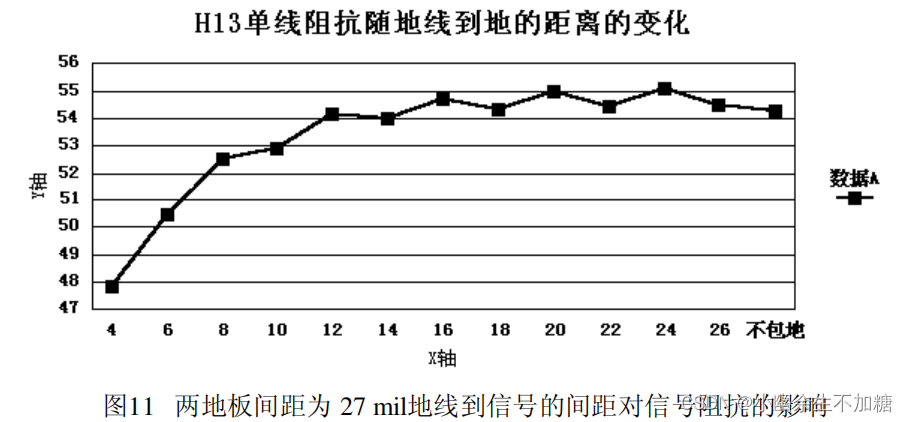

当两地板间距=27.36 mil时,阻抗随着地线到信号线之间的间距变化的情况见下表。

由上面的变化曲线可以得到:

1、随着地线到信号线的距离的增大,地线对信号线阻抗的影响逐渐减弱。

2、当两地板之间的间距为 10mil时,随着地线到信号的间距从 4mil变化到2mil,信号线阻抗基本上没用变化: 当两地板之间的间距为27mil时,随之地线到信号的间距从4mil变化到26mil,信号线阻抗从 48欧姆变化到 54欧姆: 当两地板之间的间距为 50mil时,随之地线到信号的间距从4mil变化到26mil,信号线的阻抗从55欧姆变化到70欧姆。

所以,地线对信号线阻抗的影响随之两地板之间的间距的增大而增强 。这是由于随之信号线到地板距离的增大 ,信号线到地板的耦合逐渐减弱,到地线的耦合逐渐增强造成的。

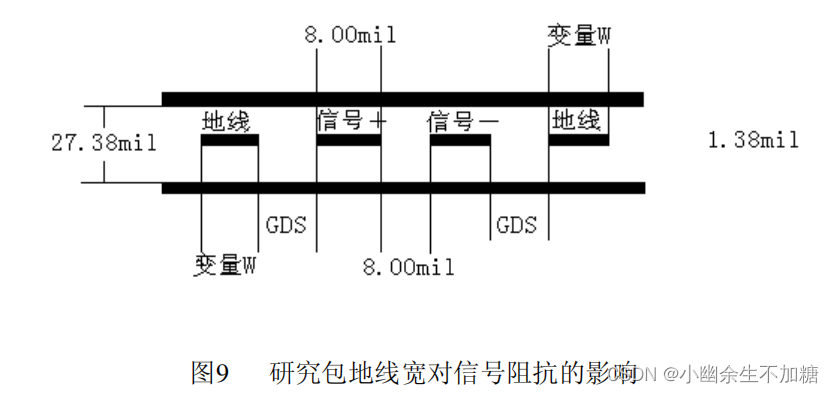

2.2 屏蔽地线线宽对阻抗的影响

为了研究屏蔽地线的线宽对信号走线阻抗的影响,我们设置以下结构: 固定信号走线的线宽为8mil、差分信号 走线的间距为 8mil、两地板之间的间距为 27.38mil。地线到信号之间的间距为6mil或12mil。

从上面两组变化趋势以XTK仿真软件计算可以得到以下结论:

A、屏蔽地线的线宽对信号的阻抗影响不是单调的 ,且对信号的影响较弱 。随着屏蔽地线线宽从4mil变化到无穷大,相应的阻抗变化只是在一个欧姆内摆动。所以在进行PCB设计时,为了节省布线空间,可以用较细的地线作为屏蔽。

B、当地线到信号的间距为6mil时,单线阻抗降低4个欧姆左右,差分阻抗降低5个欧姆左右当地线到信号的距离为12mil时,单线阻抗降低1个欧姆左右,差分阻抗也降低一个欧姆左右。对于关键信号线与接口信号,可考虑用包地线屏蔽。

3.阻抗控制案例

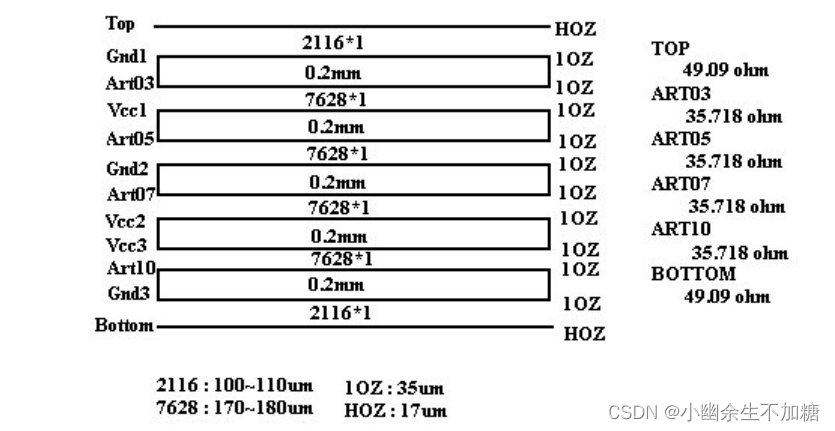

某产品单板阻抗控制:

单板为十二层板,六层走线。地层为GND1,GND2,GND3。电源层为VCC1,VCC2和VCC3。其中VCC1层为+5V电源层VCC2层为+3.3V电源层VCC3层为1.5V电源层。 从图中可看出,内层传输线阻抗为35欧,顶层阻抗为49欧,内外层阻抗不连续.在这种层次结构下,SD535到GTL16923 B口的数据线很难匹配.造成台阶与过冲现象,且此现象不可能通过匹配来消除。

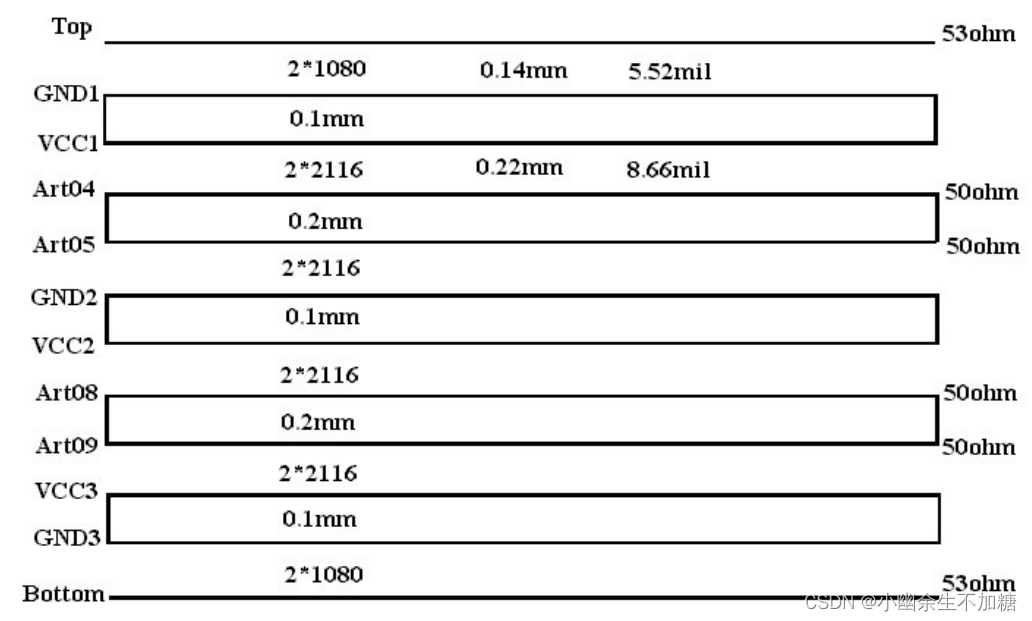

改板后的单板结构:

将原来单板的两层平面夹一层信号的结构改为两层平面夹两层信号的结构.这样内外层的阻抗基本一致,且可消除SD535到GTL1655间数据线的台阶与过冲现象.这种结构的缺点为:存在相邻层信号间的串扰.

对于相邻层信号间的串扰可通过在相邻层走线垂直,限制并行走线长度来减小串扰PCB的板厚为2.2mm+10%。PCB板上线宽基本为8mil,时钟为10mil。线距为7mil。

各层传输线的阻抗控制为:

顶层与底层的阻抗:8mil线宽时为50 10%,10mil线宽时为452 10%。内层阻抗: 7mil线宽时为492 10%,8mil线宽时为462 10%,10mil线宽时为412士10%。