1.过孔模型

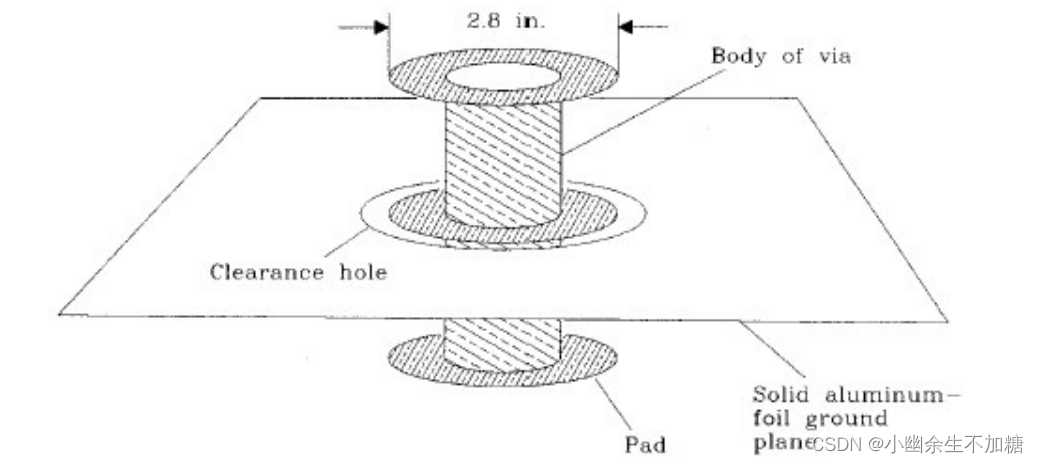

从过去设计的一些PCB板效果来看,过孔对于低频,低速信号的影响是很小的,但是近来,随着时钟速度的提高,器件的上升时间及时序问题已经成为了PCB设计中的关键问题。 过孔在PCB传输线中的影响也就成为了讨论的热点话题。 下图是PCB板过孔的一个模型。

1.1 过孔的数学模型

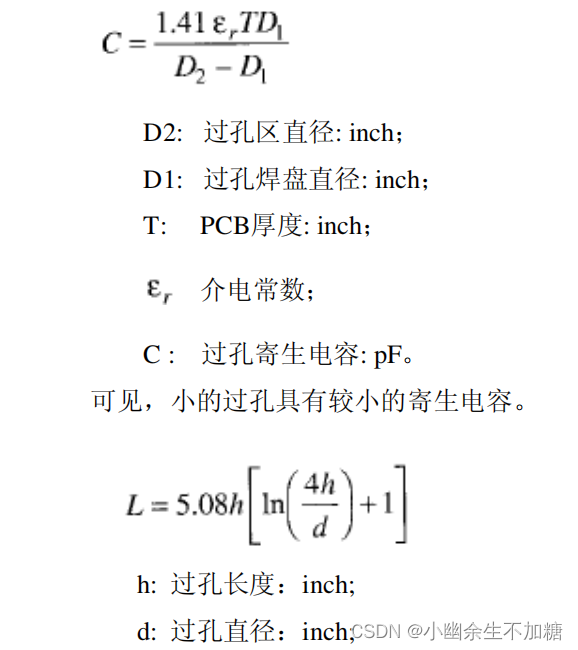

过孔与一般的传输线一样,也可以看作是电容、电感、电阻组成的参数模型,可以用场提取工具(如ANSOFT) 提取过孔模型,或者可用TDR测试方法来测试。计算公式计算:

一般仿真工具仿真分析时,过孔模型近似以 1 pf电容代替。TDR测试瞬态阻抗降落有 6~7欧姆。

1.2 对过孔模块的影响因素

由以上公式可以看出 ,影响过孔参数的因素主要有 : 过孔直径、板厚、过孔焊盘大小 。另外,不同的层设置、过孔在何处换层、平面层的影响等也是影响因素。

详细资料已经在SI教程中更新。

2.过孔对信号传导与辐射发射影响

2.2 过孔对阻抗控制的影响

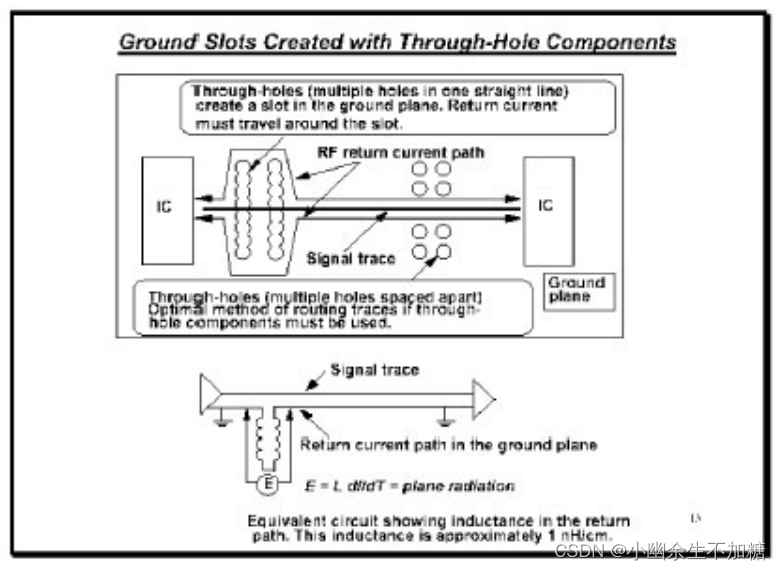

注意使用需在PCB 上钻孔的器件或在PCB 上打过孔都会引起镜像平面的非连续性,会破坏信号的最佳回流途径下图给出了一个详细的例子:

对于需在不同层之间打过孔走线的微带线或者带状线而言,在它们周边都有固定的射频回流路线,都易受干扰,最容易提高抗干扰性能的办法是不要在不同层之间打过孔布线,只在同一层走线最好,确保在微带线与地平面的任何位置上不要有任何原因造成的阻抗非连续性,如果一条敏感信号线非得打过孔不可得话,那么就要在这个信号过孔附近打上地属性的过孔来减小非连续性。设想一下对于四层以上的布线,有一层完整的地,一层完整的电源层,以及其它布线层,为了在布线时能够确保良好的信号回流,地层应担负起回流主通道的任务,若有敏感信号必需打过孔而要走到其它非地层的相邻层,那么就需对此信号线做包地处理,所包的地线应该与信号线平行,尽量靠近,如下图示:

已知的过孔的负面影响大致可分为以下几类:

1、过孔是固有电容,因此改变了PCB走线的特征阻抗;

2、过孔对于走线的特征阻抗起到了一个跳变作用,因此会导致反射,过孔导致了走线上6~7欧姆的瞬态的阻抗不连续,它导致了大约0.055的负反射系数 (50欧姆左右走线特性阻抗),近似为5%;

3、当走线从一层换到另外一层时,参考平面会发生改变,而且走线的回流路径也产生了变化。走线的特征阻抗也可能会发生很大的变化;

4、如果一层的走线从本层走到相同参考平面的另一层,过孔的影响较小,否则当换层后的参考平面发生变化后,传输线的特征阻抗将可能会发生很大的变化。

可惜的是,很少有专门的在保证其它参数不变的条件下,研究过过孔在PCB布线中的影响,这是由以下几个资源限制 至少是部分原因) 所造成的:

A、需要设计一块测试PCB板;

B、需要加工;

C、需要一套好的测试仪,并且研究者应能熟练使用它。

2.2 过孔数量对信号质量的影响

过孔数量对信号的影响还需要验证。 实际上,每一个过孔 (甚至走线本身) 都有一点高频损失。由TDR测试结果,过孔确实有容性的效果,会导致信号高次谐波的衰减,表现为信号上升时间会减缓。但是就一个过孔来说,其导致的影响和整个走线产生的衰耗相比 ,过孔所引起衰减是微不足道的。对于设计者使用上升时间范围在 0.5 ns到1.0ns (500ps 到1000ps) 的元器件 (或者更快速)来说,一个过孔所引起的 几十ps的边沿变缓相对来说是没什么影响的 ,对于甚高速设计,多个过孔的影响应该考虑,应尽量减少过孔数量。

过孔还会引起信号传输时间变长,一般一个过孔影响大约几百ps的走线延时。对于背板上长的走线来讲,一个过孔的影响也是可以忽略的。

对PCB设计过程中关于过孔的建议:

1,尽量减少过孔数量;

2,布线换层时,优选阻抗连续的平面进行切换:

3,对于低于1GHZ的信号,优先考虑内层布线,减小辐射影响,而非避免过孔。