文章目录

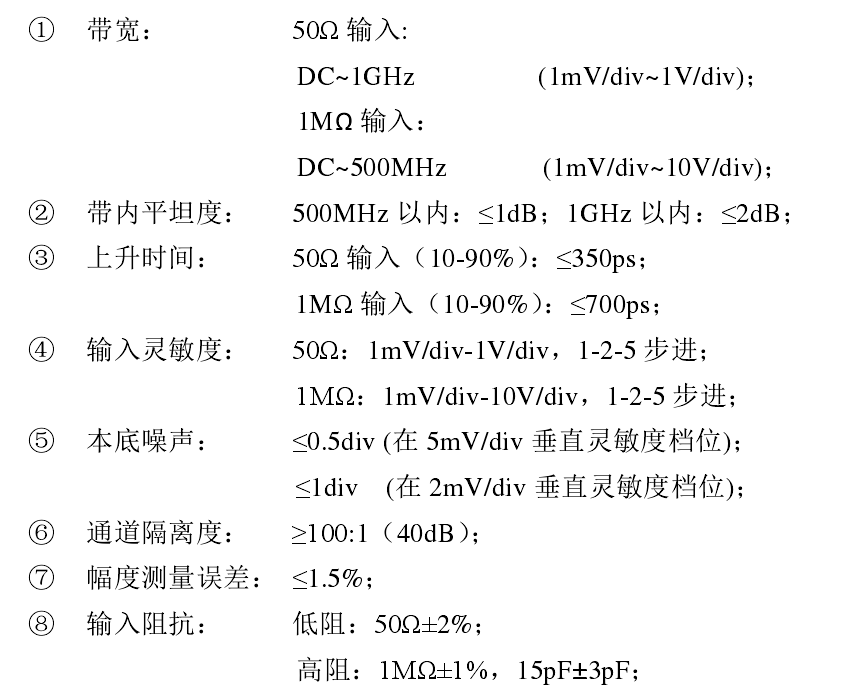

设计指标

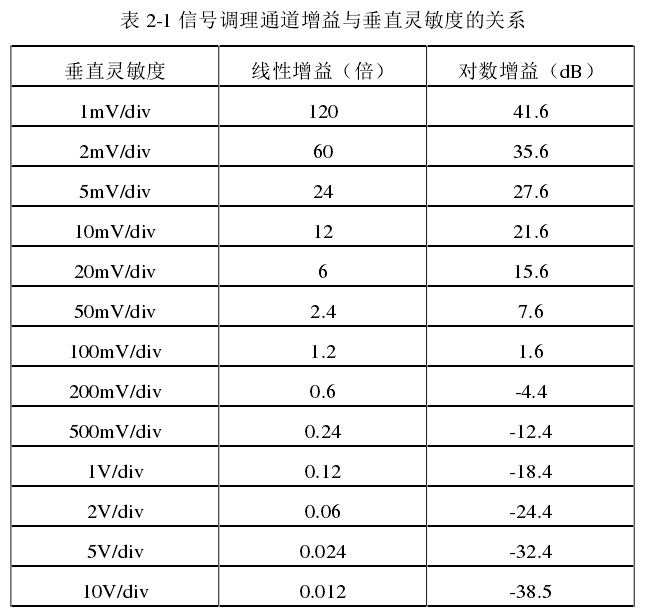

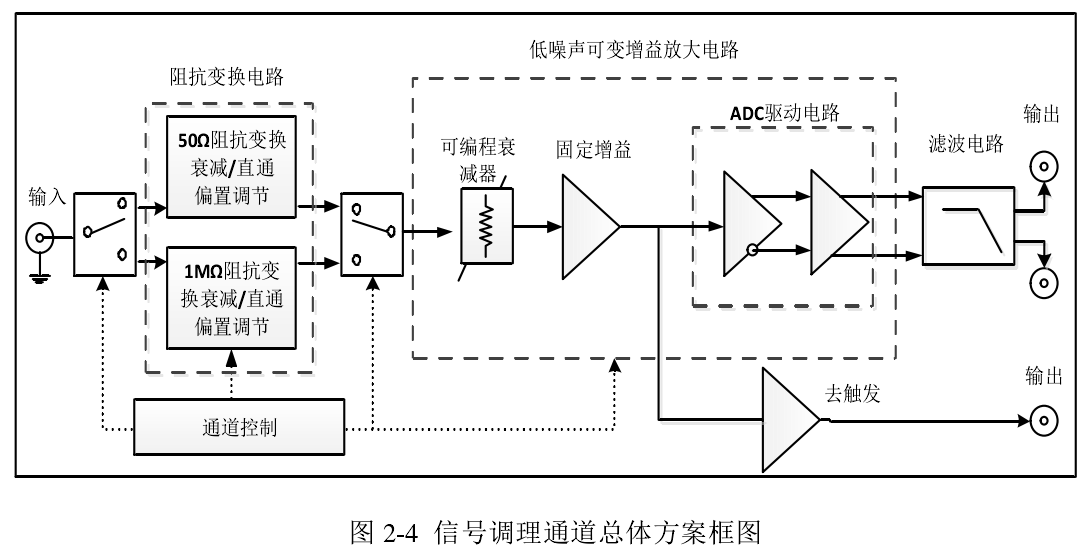

信号调理通道

整体增益

调理整体方案框图

3.1级联放大器的噪声

3.1.1常见运放噪声种类

电阻的热噪声

1/f 噪声

白噪声

3.1.2运算放大器的噪声

运算放大器等效输入噪声模型

运算放大器噪声计算

3.1.3多级放大器级联噪声计算

噪声系数

级联放大器的噪声系数

级联放大器噪声计算

无源衰减电路设计

50Ω 阻抗衰减网络,选用π型衰减网络,衰减倍数为 10 倍。

1MΩ 阻抗衰减网络,衰减倍数为 50 倍。

宽带阻抗变换电路设计

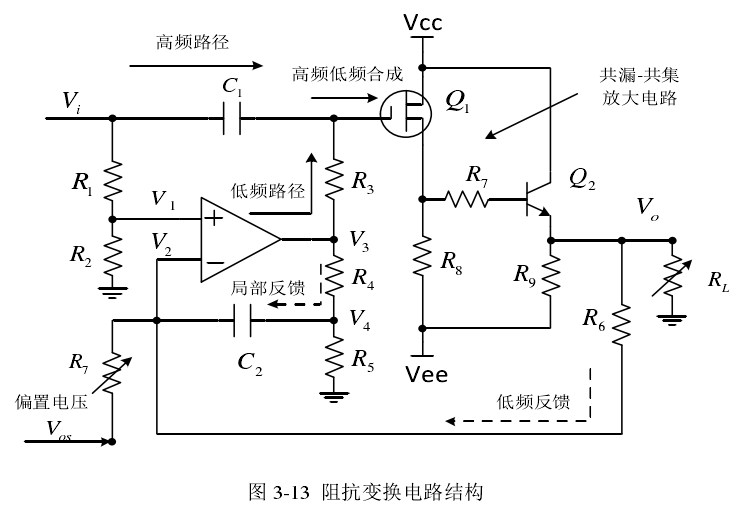

设计了一种采用运放、高频场效应管、高频晶体管等分立元件搭建的基于高低频分离路径的阻抗变换电路。

有详细的公式推导。结构分析。

选择了 ADI 公司的 ADA4610 作为阻抗变换电路的运放。

低噪声系数的高频三极管 ALG625,其特征频率高达 25GHz,最大集电极电路高低 30mA,噪声系数为 1.2dB。

场效应管选择了ATA28143,其带宽高达 10GHz,在 2GHz 带宽处的噪声系数仅为 0.4dB。

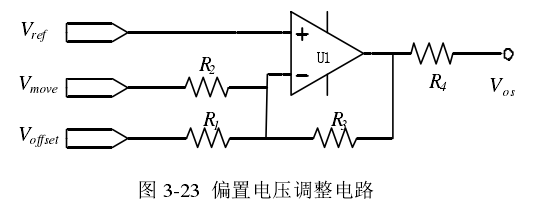

偏置电路设计

设计采用的模数转换器 AD5568 精度为 16 位,基准参考为 4.096V,其最小调节步进为 0.0625mV。

偏置的计算做了详细介绍。

低噪声可变增益放大电路分析与设计

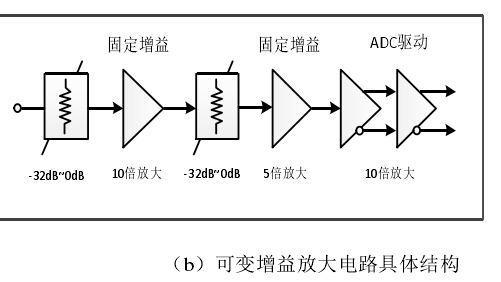

可变增益放大电路结构

可变增益放大电路增益的变化范围为:-4.5(38-42.5dB) ~38dB。

固定增益放大电路设计

选择了 ALH2402 和 ALH2401 运放,带宽分别达到 1.8GHz 和 2.4GHz

选择了 AEP4370数字步进衰减器。AEP4370 的最小衰减步进为 0.25dB,单片最大衰减范围-31.75dB,输入信号带宽可达 6GHz,可通过 SPI 接口完成衰减控制。

ADC 驱动电路设计

(1)输入阻抗设计(2)带宽和压摆率(3)噪声,谐波失真(4)供电设计。

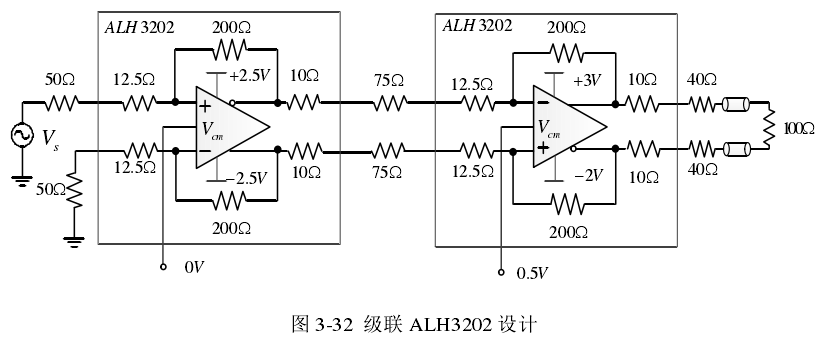

选择 ALH3202 作为 ADC 驱动器。ALH3202 在 DC 到 2GHz 范围内的频率响应非常平坦,且在 2GHz 带内平坦度小于 0.5dB。等效输入噪声仅为 1.4n V/ Hz ,在 1GHz 带宽内的噪声系数仅为 9dB。

ADC 驱动电路的增益需求为 20dB,所以单级 ALH3202 放大电路的增益无法满足需求,因此本设计采用两级 ALH3202 级联的方式

可变增益放大电路的噪声

3.4.4.1 可变增益放大电路的噪声分析

3.4.4.2 可变增益放大电路的噪声仿真

3.5信号调理通道低噪声设计

3.5.1电源设计

3.5.2滤波器设计

3.5.3屏蔽抗干扰设计

3.6 信号调理通道增益温度补偿设计

触发调理通道研究与设计

触发通道结构图

来自信号调理通道进入触发选择的信号幅度最大为 100mVpp 左右,通常将进入比较器的触发信号调理到 1Vpp 左右。

固定增益放大器选用 ALH2401,带宽达到 2.4GHz,满足设计要求。

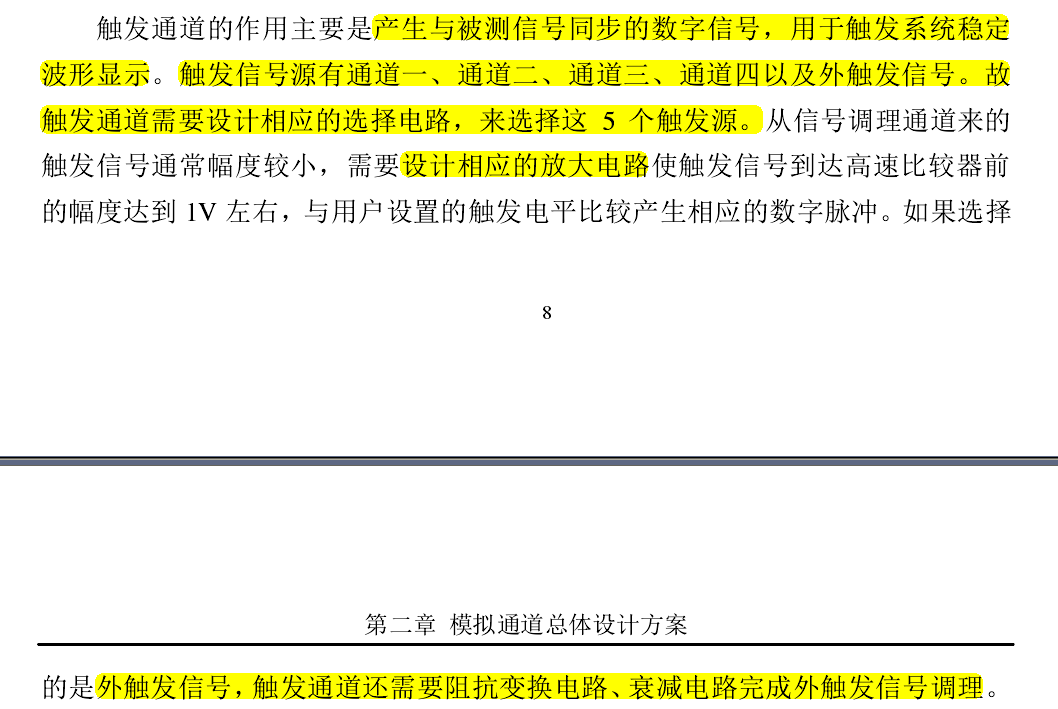

触发源选择电路设计

本设计的 5:1 选择器通过使用一个 4:1 选择器 AEP42350和 2:1 选择器 AEP4245 组合实现。

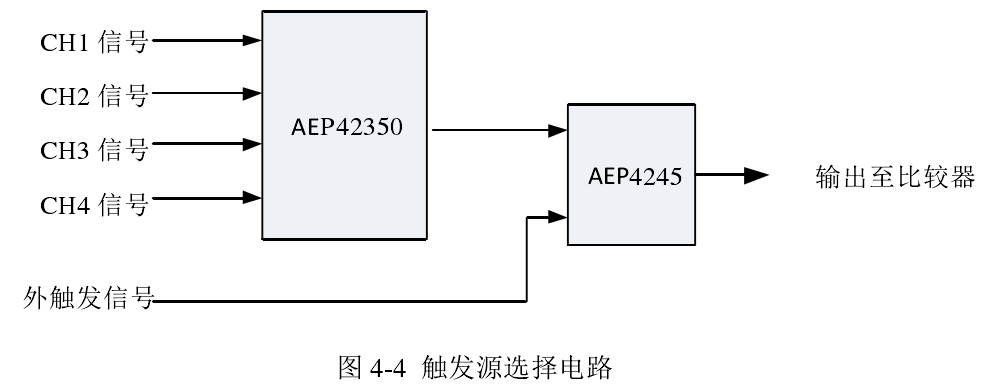

边沿触发电路设计

边沿触发电路的核心为高速比较器电路和触发电平调整电路的设计。

高速比较器:选用德州仪器(TI)公司的 LMH7322 双比较器,该比较器上升时间为 160ps(等效带宽超过 2GHz),输出兼容 LVDS 电平标准,输入电平范围为 Vcc-1.5V~Vee,可调迟滞电压范围,较好的满足了本设计的要求。

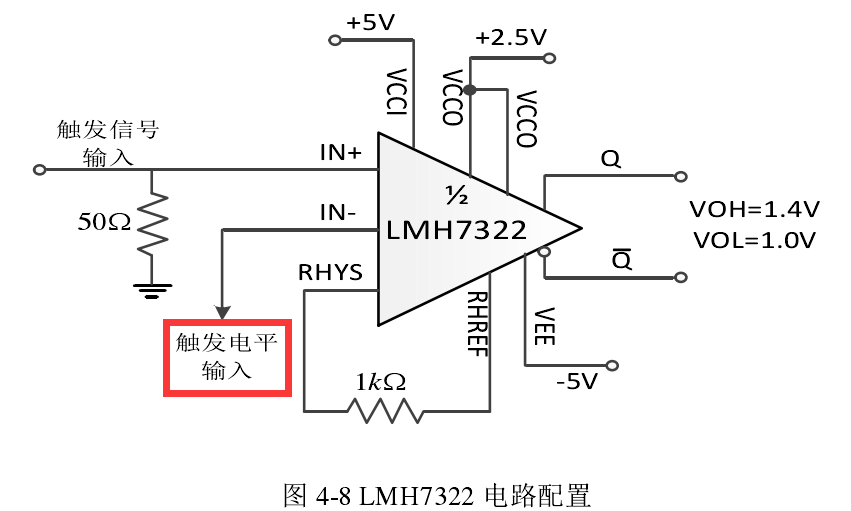

触发电平通过数模转换器件 AD5568 来输出 0-4.096V 的电压,故

触发电平不能覆盖-500mV~0mV 电压范围。将 DAC 输出电平向负端移动。

Vcomp_level为-2.096~2V,覆盖了触发信号±500mV 幅度范围。

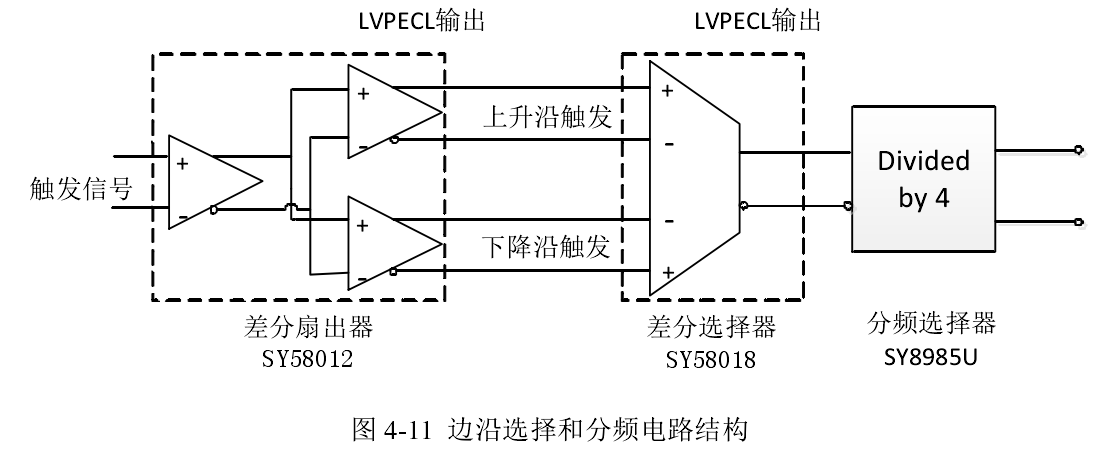

分频电路设计

通常 FPGA 的差分输入 LVDS 接口难以接收超过 600MHz的数字信号,而本次模拟通道触发带宽高达 1GHz。设计采用偶数分频,由于偶数分频后的信号上升沿和下降沿都对应原始信号的上升沿,故在触发通道增加了相应的触

发沿选择模块。

1:2 差分扇出器选择了 MICREL 公司的 SY58012,其最高 5GHz 工

作带宽,输入接口通过一个特殊端接口可方便兼容(LVPECL,LVDS,CML)三种电平标准。

2:1 差分选择器选用 SY58018,最高工作带宽 4GHz。

分频器选用 SY89875U,工作带宽达 2GHz,差分 LVDS 电平标准输出,可编程分频比率为:1,2,4,8,16。

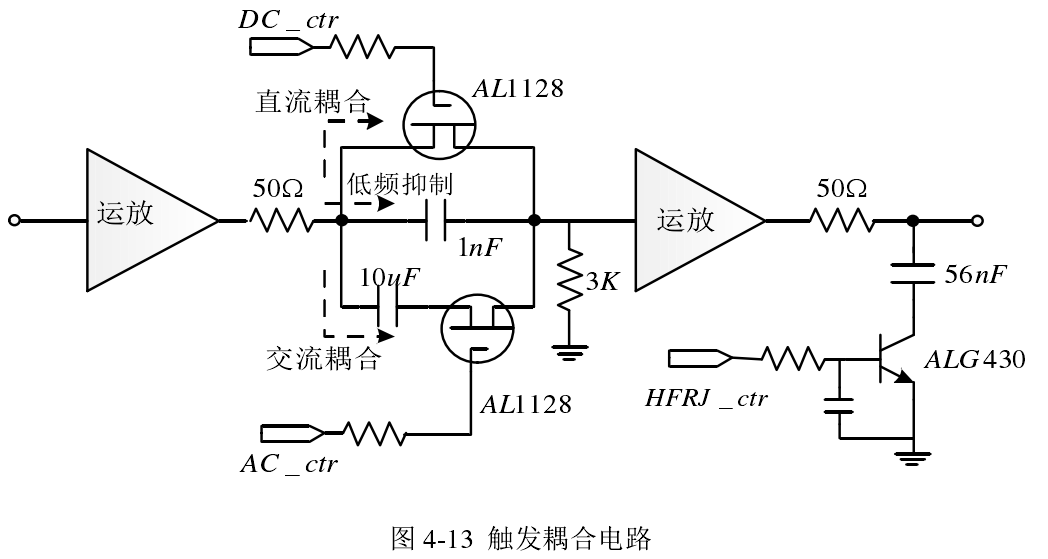

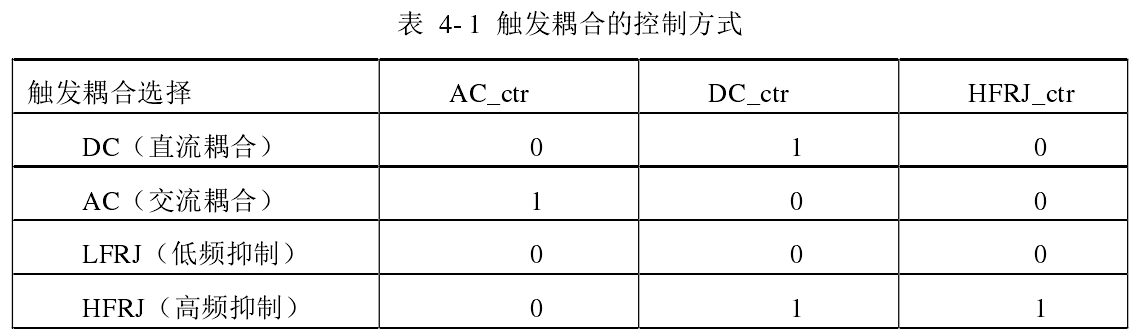

触发耦合电路设计

触发耦合电路设计主要包括:触发的低频抑制,高频抑制,交流耦合和直流耦合。

触发耦合的设计是通过分离路径来实现的,低频抑制路径通过一个 RC 高通滤波器将低频分量滤出,直流耦合路径信号经过 AL1128 射频开关管耦合到后级,而交流耦合通过 10uF 电容经过AL1128 耦合后级,高频抑制通过一开关 RC 滤波器,当控制端给高电平时,高频

三极管 ALG430 饱和导通,高频信号分量通过 RC 低通滤波器滤出。

ADC

ADC 的最佳输入方式为差分输入,共模电压为 0.5V,输入信号动态范围为1.2Vpp。

ADC 单片采样率可达 2.5GSPS,分辨率为 12bit,具有较好的线性度。

一些知识点

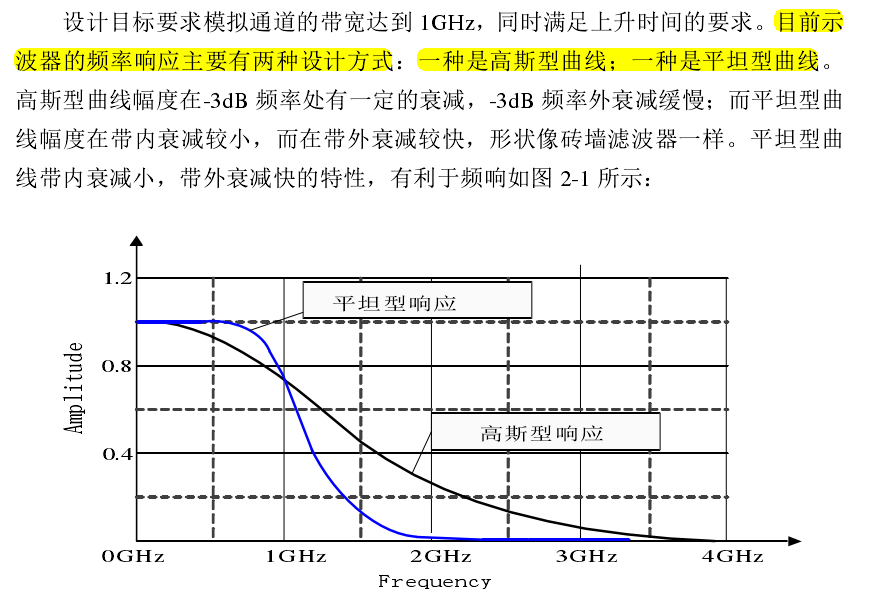

目前示波器的频率响应主要有两种设计方式:一种是高斯型曲线;一种是平坦型曲线。

FPGA 的数字接口难以接受频率超过600MHz 以上的数字信号,而本次设计触发频率高达 1GHz,故还需设计分频电路。

低噪声可变增益放大电路决定了信号调理通道的增益和衰减范围,同时也是信号调理通道噪声的主要来源。单片的 PGA(可编程放大器)由于增益范围,带宽有限,本次设计采用级联可编程衰减器和宽带固定增益放大器来实现。为了优化噪声性能,通常第一级放大器的增益尽量大,噪声系数尽量小。

外触发信号,触发通道还需要阻抗变换电路、衰减电路完成外触发信号调理。

TINA-TI 仿真软件对噪声进行了仿真。德州仪器(TI)公司的 TINA-TI 能够对运算放大器的噪声进行分析,并能够图形化显示放大器的等效输出电压噪声密度,总输出噪声电压有效值,以及信噪比等。可以方便的用来评估放大器的噪声性能。

宽带阻抗变换电路主要完成输入信号的缓冲,减小后级的负载效应,是宽带示波器一个关键电路。**利用运放实现的电压跟随电路或者同向放大电路的带宽有限,难以达到上 GHz 的带宽。**并且运放的输入阻抗有限通常为 MΩ 级,示波器高阻输入阻抗为 1MΩ,势必会产生负载效应,导致输入后级放大器的信号衰减。同时运放的噪声较大,通过前面 3.1.3.2 小结中对级联放大器噪声系数的分析,放大电路的前级噪声系数越小越好。

仿真采用 OrCAD PSpice 对电路进行仿真,其具有较为丰富的元件库和电路 Spice 模型,可以方便的进行四种常用仿真:

时域瞬态分析(Time Domain):可以方便的观察不同时刻的波形,通过添加激励源,可以方便的观察各点波形,相当于示波器的功能。

直流扫描分析(DC Sweep):可以让一个直流量变化,观察其对输出的影响。

AC 扫描参数分析:观察电路的频率响应,幅频特性等。

直流偏置点分析(Bias Point):可以方便的观察电路的直流工作点。

偏置电压调节作用是:当外部送入带有较大直流偏置而信号幅度较小的信号时,可以通过调节偏置电压将波形从屏幕外调整回屏幕内,以利于波形的观察。

通常无源衰减网络固定衰减倍数应小于 100 倍(40dB)(受限于高频继电器隔离度限制以及无源衰减电路衰减倍数对带宽影响)。

由于通常高速 ADC 工作在差分输入方式(有利于抑制共模噪声以及抗干扰),故需要将单端信号转换为差分信号输出。单端转差分可以由差分运放,射频巴伦,以及变压器等实现。

变压器为线圈无源器件,噪声小,但变压器不能通过直流。

射频巴伦的带宽高,带内平坦,但是不能提供增益,也不能通过直流信号。

全差分运放为有源器件,可以完成增益设计,单端-差分转换,共模电压调整,滤波等设计,已经成为 ADC 驱动设计的常用选择。

设计差分运放时需要考虑差分运放的输入阻抗设计,允许输入的共模电压范围,带宽和压摆率,耦合方式,噪声,谐波失真,稳定性等。