通过Verilog HDL语言使用Quartus II软件编写一个彩灯控制电路的设计

1 系统设计

1.1 设计要求

1.1.1 设计任务

设计并制作彩灯控制电路。

1.1.2 性能指标要求

① 用EDA实训仪的I/O设备和PLD芯片实现彩灯控制电路的设计。

② 彩灯控制电路具有1只复位按钮,当按钮按下后开始彩灯控制电路的工作。

③ 彩灯控制电路至少有4种以上的控制模式,如左移、右移、循环移位等,彩灯控制电路开始工作后,各工作模式能自动倒换。

④ 用EDA实训仪上的12只发光数码管(LED)显示彩灯控制电路的工作模式。

1.2 设计思路及设计框图

1.2.1设计思路

首先用Verilog HDL语言编写20M晶振分频器的程序和彩灯控制电路的主程序进行编译、仿真成功后,分别将它们生成图标,然后进入原理图的编辑方式,将分频器的输出作为彩灯控制电路的时钟输入,同时将各原件符号接上输出、输入端口,最后锁定管脚,完成下载验证过程。

1.2.2总体设计框图

彩灯原理图

2 各个模块程序的设计

- 设计一个分频器进行20MHz分频得到实训所需的1Hz的频率:

如图,将提供的频率为20MHZ的时钟转换成频率1HZ的时钟,然后输给到有需要的端口,触发下一个模块。

2彩灯控制

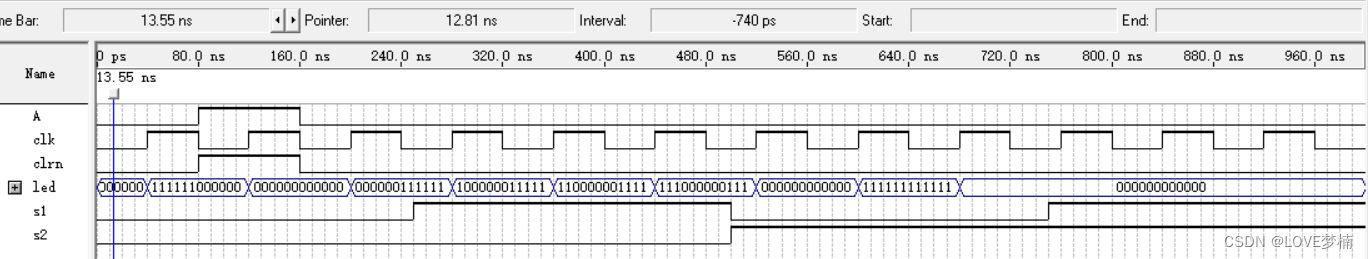

如图,clk是时钟输入端,上升沿有效,A控制彩灯亮灭的进行,s1,s2控制彩灯左移、右移、循环移位等,clrn是异步清除输入端,高电平清零,led[11..0]为彩灯的输出。

3 调试过程

为了控制LED灯闪烁的频率所以加入了分屏器,总共分成了两个模块,开始时忘记设顶层文件,导致仿真出错,编译时,由于模块的问题,导致编译结果出错,在自己的反复检查下,改正,之后锁好管脚,然后下载到实验箱,按照自己所写的程序操作,通过拨动开关进行观察是否与程序编程相同。

4 功能测试

4.1 测试仪器与设备

(1)计算机:1台。

(2)EDA实训仪:1台。

4.2 性能指标测试

Clrn为复位开关,待高电频到来执行复位功能。A为暂停功能,待高电频到来执行暂停操作,当S1=0,S2=0时:执行六灯循环闪烁功能;当S1=0,S2=1时:执行全部闪烁功能;当S1=1,S2=0时:执行右循环功能;当S1=1,S2=1时:执行左循环功能。

4.3 误差分析

因为时钟信号存在延迟,仿真结果并不与时钟信号一一对应

5 实训心得体会

EDA实训到此也结束了,我对Quartus II软件的各项操作有了更深的了解,也让我更加了解了这门课在现实生活中的应用。这次EDA实训让我感觉收获颇多,在这一-周的实训中我们不仅巩固了以前学过的知识,而且还学到了怎样运用E D A设计彩灯亮灭的整个过程和思路,更加强了我们动手能力,同时也提高了我们的思考能力的锻炼,我们在写程序的同时还要学会要改程序,根据错误的地方去修改程序。本文基于Verilog HDL的彩灯控制电路的设计,现代的关于电的东西或多或少都与EDA有关,我选择彩灯控制电路设计是因为对彩灯的左移、右移的实验很感兴趣,所以就选了这个题目,结合之前作业的一些程序,在原来的基础上加上一些创新程序做出了这个彩灯实训。在制作的过程中还是出了很多问题,尤其是在编译时总是出现问题,在自己反复修改后,终于完成了编译。总之这次实训学到了很多东西,加深了我对Quartus II软件的了解。

6 参考文献

[1] EDA技术与应用(第五版),潘松,黄继业,潘明编著。北京:科学出版社

7 附录

附录1:仿真波形图(部分模块)

附录2:程序清单

1.分屏器

module fpq(clk,q);

input clk;

output reg q;

reg[24:0]count;

always@(posedge clk)

begin

count=count+1;

if (count==10000000) q=1;

else if (count==20000000)

begin

q=0;

count=0;

end

end

endmodule- 彩灯程序

module z1(clk,A,s1,s2,led,clrn);

input clk,A,clrn;

input s1,s2;

output reg[11:0] led;

reg q_temp;

reg c;

always @(posedge clk)

begin

if(clrn) led='b000000000000;

else

if(A==0)

begin

case({s1,s2})

'b00:begin

c=c+'b1;

if(c=='b1)

led='b111111000000;

else

led='b000000111111;

end

'b01:begin

c=c+'b1;

if(c=='b1)

led='b000000000000;

else

led='b111111111111;

end

'b10:begin

q_temp=led[0];

led=led>>1;

led[11]=q_temp;

end

'b11:begin

q_temp=led[11];

led=led<<1;

led[0]=q_temp;

end

endcase

end

end

endmodule