TAUJ定时器为RH850较为常用的定时器:

(1)定时器计时是通过计数来实现的,定时器内部有一个计数器,这个计数器根据时钟(这个时钟来自于ARM的APB总线)来工作。每隔一个时钟周期,计数器就就计数一次,定时器的时间=计数器计数值x时钟周期。

(2)定时器内部有计数器,计时开始时我们会把一个总的计数值放入计数器中,然后每隔一个时钟周期计数器中的值会自动减1(硬件自动完成,不需要CPU软件去干预),当计数器的值减为0的时候,就会触发定时器中断。最后的计时时间就是设定值。

(3)定时时间是由2个东西共同决定的:一个是计数器中的计数值,一个是时钟周期。

- TAUJ Timer定时器寄存器介绍

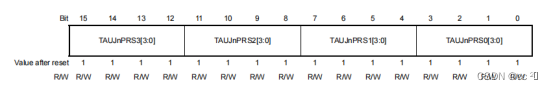

1.1、TAUJn 时钟预分频选择寄存器Prescaler Clock Select Register

| Bit position |

Bit Name |

Function |

| 15 - 12 |

TAUJnPRS3 |

指定CK3_PRE时钟。 |

| 11 - 8 |

TAUJnPRS2 |

指定CK2_PRE时钟。 |

| 7 - 4 |

TAUJnPRS1 |

指定CK1_PRE时钟。 |

| 3 - 0 |

TAUJnPRS0 |

指定CK0_PRE时钟。 |

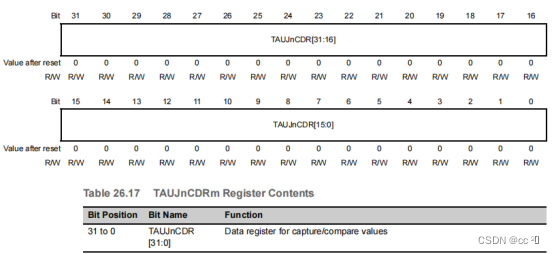

1.2、TAUJn 通道数据寄存器 Channel Data Register

| Bit position |

Bit Name |

Function |

| 31 - 0 |

TAUJnCDR |

用于捕获/比较值的数据寄存器 |

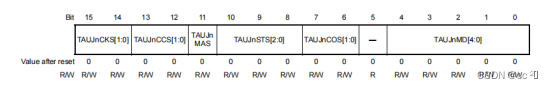

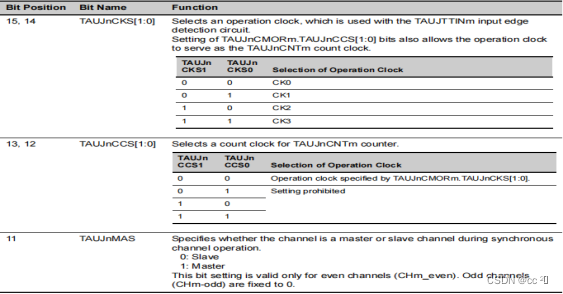

1.3、TAUJn 通道模式操作系统寄存器Channel Mode OS Register

| Bit position |

Bit Name |

Function |

| 15、14 |

TAUJnCKS |

选择一个操作时钟,该时钟与TAUJTTINm输入一起使用检测电路。 设置TAUJnCMORm。TAUJnCCS[1:0]位允许操作时钟 作为TAUJnCNTm计数器。 |

| 13、12 |

TAUJnCCS |

为TAUJnCNTm选择一个计数时钟。 |

| 11 |

TAUJnMAS |

指定同步期间通道是主通道还是从通道 通道操作。 0:从 1:主 (此位设置仅对偶数通道有效) |

| Bit position |

Bit Name |

Function |

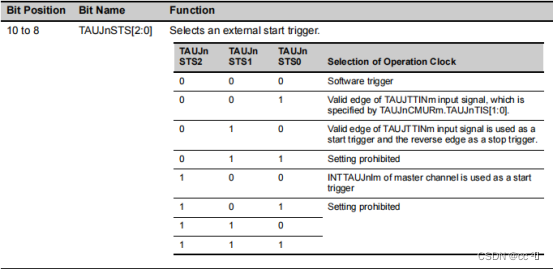

| 10 to 8 |

TAUJnSTS |

选择外部中断触发器。 |

| Bit position |

Bit Name |

Function |

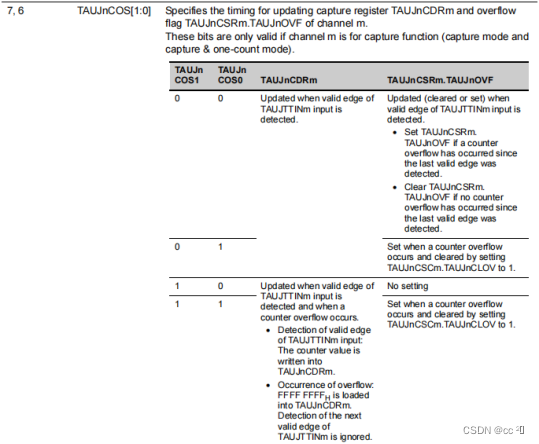

| 7、6 |

TAUJnCOS |

指定捕获寄存器TAUJnCDRm和溢出的时间 TAUJnCSRm。这些位只在通道m用于捕获功能(捕获模式和捕获一次计数模式)。 |

| Bit position |

Bit Name |

Function |

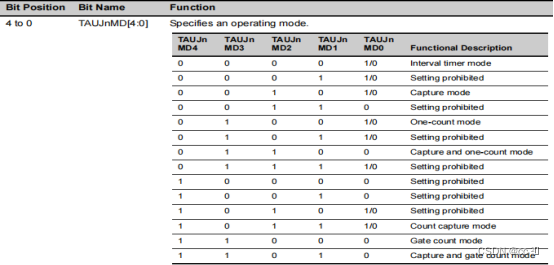

| 4 to 0 |

TAUJnMD |

选择运行模式。 |

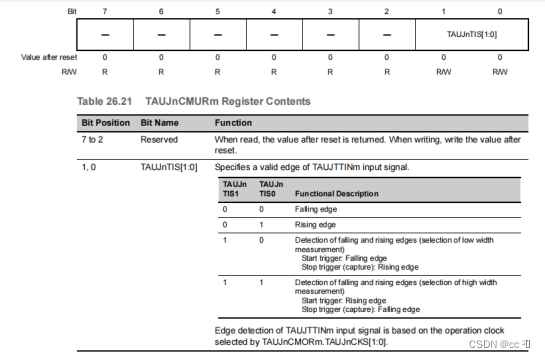

1.4、TAUJn 通道模式使用寄存器 Channel Mode User Register

| Bit position |

Bit Name |

TIS1 |

TISO |

Function |

| 1,0 |

TAUJnTIS |

0 |

0 |

下降沿 |

|

|

|

0 |

1 |

上升沿 |

|

|

|

1 |

0 |

下降边缘和上升边缘的检测(选择低宽度 测量) 开始触发:下降边缘 停止触发(捕获):上升边缘 |

|

|

|

1 |

1 |

下降边缘和上升边缘的检测(选择高宽度 测量) 启动触发器:上升边缘 停止触发(捕获):下降边缘 |

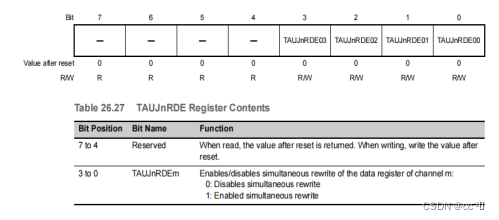

1.5、TAUJn通道重新加载数据启用寄存器 Channel Reload Data Enable Register

| Bit position |

Bit Name |

Function |

| 3 to 0 |

TAUJnRDEm |

0:禁用同时重写 1:开启同时重写 |

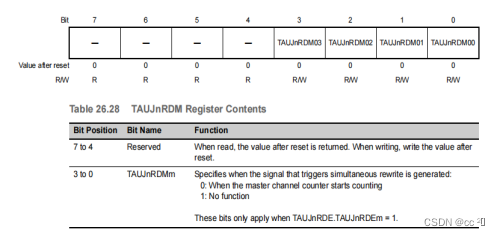

1.6、TAUJn通道重新加载数据模式寄存器 Channel Reload Data Mode Register

| Bit position |

Bit Name |

Function |

| 3 to 0 |

TAUJnRDMm |

0:当主频道计数器开始计数时 1:无效 |

例程:

void R_TAUJ_Init( void )

{

uint32_t reg32_value;

/* Source Clock Setting for C_AWO_TAUJ

CKSC_ATAUJS_CTL - C_AWO_TAUJ Source Clock Selection Register

b31:b 2 - Reserved set to 0

b 1:b 0 ATAUJSCSID - Source Clock Setting for C_AWO_TAUJ - HS IntOSC fRH (8MHz) */

do

{

reg32_value = 0x00000001UL;

WPROTRPROTCMD0 = 0x000000A5UL; /* Protection release the CKSC_ATAUJS_CTL register. */

CLKCTLCKSC_ATAUJS_CTL = reg32_value;

CLKCTLCKSC_ATAUJS_CTL = ~reg32_value;

CLKCTLCKSC_ATAUJS_CTL = reg32_value;

} while ( PORTPPROTS0 != 0x00000000UL );

while( CLKCTLCKSC_ATAUJS_ACT != reg32_value )

{

/* Waiting for CKSC_ATAUJS_CTL to set. */

}

/* Clock Divider Setting for C_AWO_TAUJ

CKSC_ATAUJD_CTL - C_AWO_TAUJ Divided Clock Selection Register

b31:b 2 - Reserved set to 0

b 1:b 0 ATAUJDCSID - Clock Divider Setting for C_AWO_TAUJ - CKSC_ATAUJS_CTL selection / 1 */

do

{

reg32_value = 0x00000001UL;

WPROTRPROTCMD0 = 0x000000A5UL; /* Protection release the CKSC_ATAUJD_CTL register. */

CLKCTLCKSC_ATAUJD_CTL = reg32_value;

CLKCTLCKSC_ATAUJD_CTL = ~reg32_value;

CLKCTLCKSC_ATAUJD_CTL = reg32_value;

} while ( PORTPPROTS0 != 0x00000000UL );

while( CLKCTLCKSC_ATAUJD_ACT != reg32_value )

{

/* Waiting for CKSC_ATAUJD_CTL to set. */

}

/* Set interrupt flags */

INTC2MKTAUJ0I0 = 1U;

INTC2RFTAUJ0I0 = 0U;

INTC2TBTAUJ0I0 = 1U;

/* Set the clock stop mask and select the clock domains to be stopped and to continue operating.

CKSC_ATAUJD_STPM - C_AWO_TAUJ Stop Mask Register

b31:b 1 - When read, the value after reset is returned. When writing to these bits,

write the value after reset.

b 0 ATAUJDSTPMSK - Clock domain C_AWO_TAUJ is not stopped in stand-by mode. Set to 1'b. */

CLKCTLCKSC_ATAUJD_STPM = 0x00000003UL;

/* Specifies the CK3 , CK2 , CK1 and CK0 clock

TAUJnTPS - TAUJn Prescaler Clock Select Register

b15:b12 TAUJnPRS3 - Specifies CK3_PRE clock - PCLK / 1

b11:b 8 TAUJnPRS2 - Specifies CK2_PRE clock - PCLK / 1

b 7:b 4 TAUJnPRS1 - Specifies CK1_PRE clock - PCLK / 1

b 3:b 0 TAUJnPRS0 - Specifies CK0_PRE clock - PCLK / 1 */

TAUJ0TPS = 0x0000U; /* HS IntOsc fRH(8MHz) / 1 */

/* Data register for the capture/compare value

TAUJnCDRm - TAUJn Channel Data Register

b31:b 0 TAUJnCDR - Data register for capture/compare values - 1ms */

TAUJ0CDR0 = 8000UL - 1UL; /* INTTAUJnIm cycle = count clock cycle * (TAUJnCDRm + 1) */

/* Controls master channel operation

TAUJnCMORm - TAUJn Channel Mode OS Register

b15:b14 TAUJnCKS - Selects an operation clock. - Selected Operation CK0

b13:b12 TAUJnCCS0 - Selects a count clock for TAUJnCNTm counter. - Set to 00'b

b11 TAUJnMAS - Specifies whether the channel is a master

channe or slave channel during synchronous

channel operation. - Set to 0'b

b10:b 8 TAUJnSTS - Selects an external start trigger. - Set to 000'b

b 7:b 6 TAUJnCOS - Specifies the timing for updating capture

register TAUJnCDRm and overflow flag

TAUJnCSRm.TAUJnOVF of channel m. - Set to 00'b.

b 5 - Reserved set to 0

b 4:b 1 TAUJnMD - Specifies an operating mode. - Interval timer mode. Set to 0000'b

b 0 TAUJnMD0 - Specifies whether INTTAUJnIm is generated

at the beginning of count operation (when

a start trigger is entered) or not. - INTTAUDnIm is not generated.

Set to 0'b */

TAUJ0CMOR0 = 0x0000U;

/* Specifies the type of valid edge detection used for the TAUJTTINm input.

TAUJnCMURm - TAUJn Channel Mode User Register

b 7:b 2 - Reserved set to 0

b 1:b 0 TAUJnTIS - Specifies a valid edge of TAUJTTINm input

signal. - Unused. Set to 00'b. */

TAUJ0CMUR0 = 0x00U;

/* TAUJnTOE.TAUJnTOEm is set to 0 because the channel output mode is not used by this samples. */

TAUJ0TOE &= 0xFEU;

/* Unused TAUJnRDE, TAUJnRDM registers in interval timer function. */

/* These registers set "0". */

TAUJ0RDE &= 0xFEU;

TAUJ0RDM &= 0xFEU;

}