一、串口通信协议简介

串口通讯(Serial Communication)是一种设备间非常常用的串行通讯方式,因为它简单便捷,因此大部分电子设备都支持该通讯方式,电子工程师在调试设备时也经常使用该通讯方式输出调试信息。 在计算机科学里,大部分复杂的问题都可以通过分层来简化。如芯片被分为内核层和片上外设。对于通讯协议, 我们也以分层的方式来理解,最基本的是把它分为物理层和协议层。物理层规定通讯系统中具有机械、电子功能部分的特性,确保原始数据在物理媒体的传输。协议层主要规定通讯逻辑,统一收发双方的数据打包、解包标准。简单来说物理层规定用嘴巴还是用肢体来交流,协议层则规定用中文还是英文来交流。 下面分别对串口通讯协议的物理层及协议层进行讲解。

1. 物理层

串口通讯的物理层有很多标准及变种,这里主要讲解RS-232标准 ,RS-232标准主要规定了信号的用途、通讯接口以及信号的电平标准。

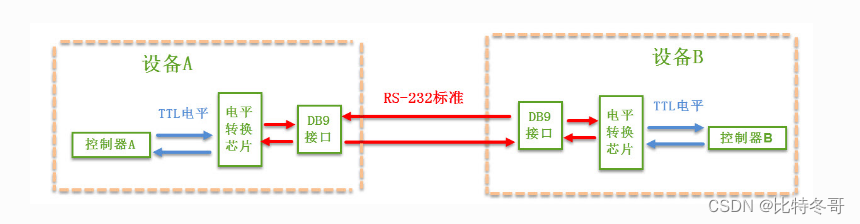

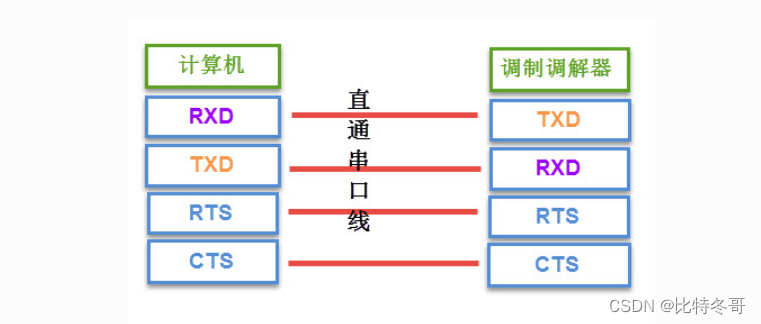

使用RS-232标准的串口设备间常见的通讯结构见下图:

在上面的通讯方式中,两个通讯设备的“DB9接口”之间通过串口信号线建立起连接,串口信号线中使用“RS-232标准”传输数据信号。由于RS-232电平标准的信号不能直接被控制器直接识别,所以这些信号会经过一个“电平转换芯片”转换成控制器能识别的“TTL标准”的电平信号,才能实现通讯。

① 电平标准

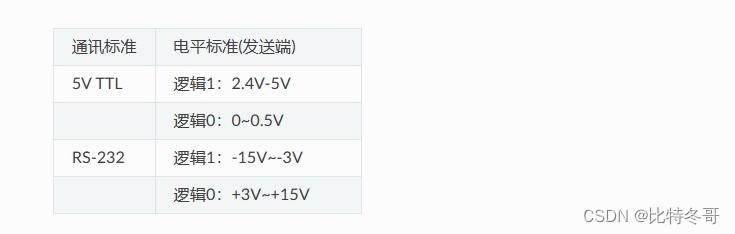

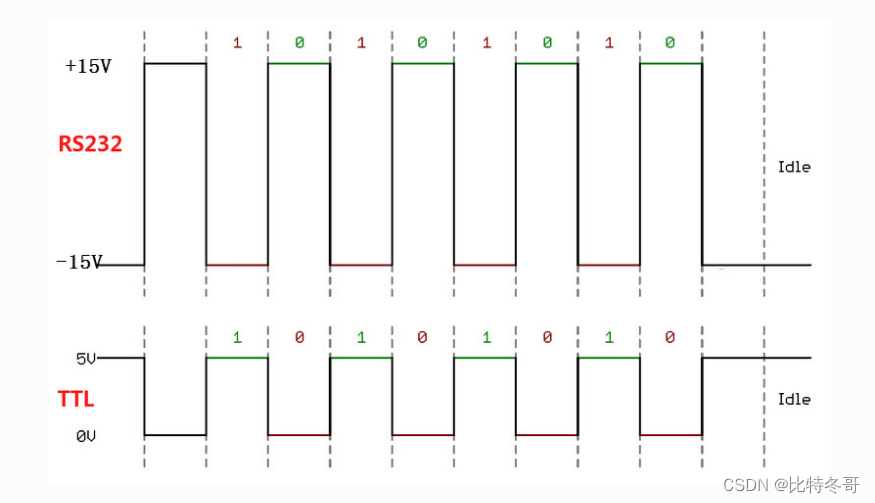

根据通讯使用的电平标准不同,串口通讯可分为TTL标准及RS-232标准,见下表

知道常见的电子电路中常使用TTL的电平标准,理想状态下,使用5V表示二进制逻辑1,使用0V表示逻辑0; 而为了增加串口通讯的远距离传输及抗干扰能力, RS-232使用-15V表示逻辑1,+15V表示逻辑0。使用RS232与TTL电平校准表示同一个信号时的对比见下图

因为控制器一般使用TTL电平标准,所以常常会使用MA3232芯片对TTL及RS-232电平的信号进行互相转换。

② RS-232信号线

在最初的应用中,RS-232串口标准常用于计算机、路由与调制调解器(MODEN,俗称“猫”)之间的通讯 ,在这种通讯系统中,设备被分为数据终端设备DTE(计算机、路由)和数据通讯设备DCE(调制调解器)。 以这种通讯模型讲解它们的信号线连接方式及各个信号线的作用。

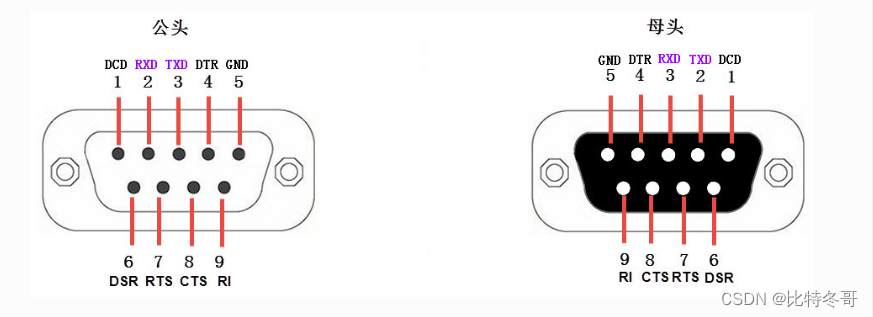

在旧式的台式计算机中一般会有RS-232标准的COM口(也称DB9接口),见下图

其中接线口以针式引出信号线的称为公头,以孔式引出信号线的称为母头。 在计算机中一般引出公头接口,而在调制调解器设备中引出的一般为母头,使用上图中的串口线即可把它与计算机连接起来。 通讯时,串口线中传输的信号就是使用前面讲解的RS-232标准调制的。

在这种应用场合下,DB9接口中的公头及母头的各个引脚的标准信号线接法见下图

由于两个通讯设备之间的收发信号(RXD与TXD)应交叉相连, 所以调制调解器端的DB9母头的收发信号接法一般与公头的相反,两个设备之间连接时, 只要使用“直通型”的串口线连接起来即可,见下图

串口线中的RTS、CTS、DSR、DTR及DCD信号,使用逻辑 1表示信号有效,逻辑0表示信号无效。例如,当计算机端控制DTR信号线表示为逻辑1时,它是为了告知远端的调制调解器,本机已准备好接收数据,0则表示还没准备就绪。

在目前的其它工业控制使用的串口通讯中,一般只使用RXD、TXD以及GND三条信号线,直接传输数据信号,而RTS、CTS、DSR、DTR及DCD信号都被裁剪掉了。

2. 协议层

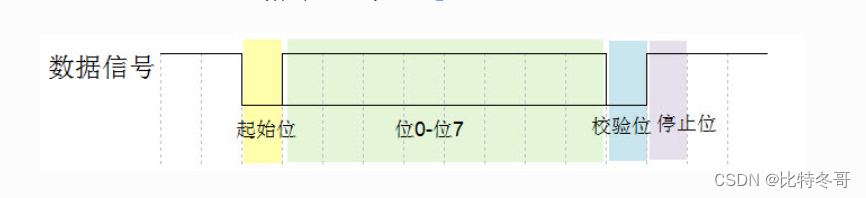

串口通讯的数据包由发送设备通过自身的TXD接口传输到接收设备的RXD接口。在串口通讯的协议层中,规定了数据包的内容, 它由启始位、主体数据、校验位以及停止位组成,通讯双方的数据包格式要约定一致才能正常收发数据,其组成见下图

① 波特率

这里主要讲解的是串口异步通讯,异步通讯中由于没有时钟信号(如前面讲解的DB9接口中是没有时钟信号的), 所以两个通讯设备之间需要约定好波特率,即每个码元的长度,以便对信号进行解码, 上图中用虚线分开的每一格就是代表一个码元。常见的波特率为4800、9600、115200等。

② 通讯的起始和停止信号

串口通讯的一个数据包从起始信号开始,直到停止信号结束。 数据包的起始信号由一个逻辑0的数据位表示,而数据包的停止信号可由0.5、1、1.5或2个逻辑1的数据位表示,只要双方约定一致即可。

③ 有效数据

在数据包的起始位之后紧接着的就是要传输的主体数据内容,也称为有效数据,有效数据的长度常被约定为5、6、7或8位长。

④ 数据校验

在有效数据之后,有一个可选的数据校验位。 由于数据通信相对更容易受到外部干扰导致传输数据出现偏差,可以在传输过程加上校验位来解决这个问题。 校验方法有奇校验(odd)、偶校验(even)、0校验(space)、1校验(mark)以及无校验(noparity)。

奇校验要求有效数据和校验位中“1”的个数为奇数, 比如一个8位长的有效数据为:01101001,此时总共有4个“1”, 为达到奇校验效果,校验位为“1”,最后传输的数据将是8位的有效数据加上1位的校验位总共9位。

偶校验与奇校验要求刚好相反,要求帧数据和校验位中“1”的个数为偶数, 比如数据帧:11001010,此时数据帧“1”的个数为4个,所以偶校验位为“0”。

0校验是不管有效数据中的内容是什么,校验位总为“0”,1校验是校验位总为“1”。

二、SCI 简介

SCI(Serial Communications Interface),意为串行通信接口, 是相对与并行通信的概念,是串行通信技术的一种总称,包括了UART,SPI等串行通信技术。 RA6M5 的SCI模块是一个有10个通道的异步/同步串行接口,RA4M2 有6个通道,RA2L1 有5个通道。

SCI 模块包含如下功能(根据具体型号有所不同):

-

UART

-

8位时钟同步接口

-

简易IIC(只能用作主机)

-

简易SPI

-

智能卡接口(符合ISO/IEC 7816-3国际标准)

-

曼彻斯特接口

-

增强的串行接口

另外,RA6M5 的 SCI0、SCI3~SCI9 有独立的FIFO缓冲区; RA4M2 的 SCI0、SCI3、SCI4、SCI9 有独立的FIFO缓冲区; RA2L1 仅 SCI0 有独立的FIFO缓冲区。

三、SCI的结构框图

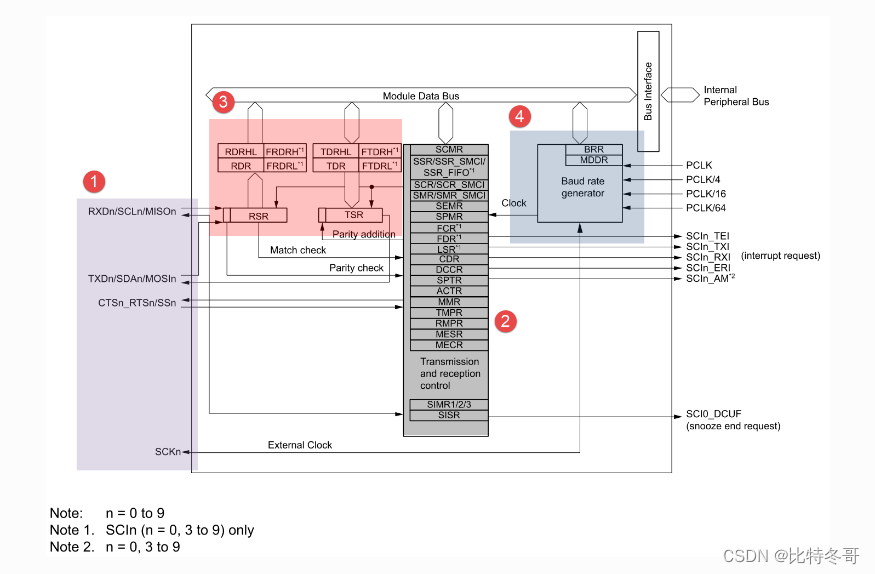

SCI的结构框图如下图所示

1. 功能引脚

见图中标注 ① 处。

① RXDn/SCLn/MISOn:

-

RXDn:UART接收数据输入。

-

SCLn:I2C时钟信号输入或输出。

-

MISOn:SPI主机信号输入,从机信号输出。

② TXDn/SDAn/MOSIn:

-

TXDn:UART发送数据输出。

-

SDAn:I2C数据输入或输出。

-

MOSIn:SPI从机信号输入,主机信号输出。

③ SSn/CTSn_RTSn:

-

SSn:片选信号输入,低电平有效。

-

CTSn_RTSn:清除以发送(Clear to Send)或请求以发送(Request to Send)。 低电平有效。如果使能RTS流控制,当UART接收器准备好接收新数据时就会将RTS变成低电平;当接收寄存器已满时,RTS将被设置为高电平。 如果使能CTS流控制,发送器在发送下一帧数据之前会检测CTS引脚,如果为低电平,表示可以发送数据,如果为高电平则在发送完当前数据帧之后停止发送, 该引脚只适用于硬件流控制。

④ CTSn (n = 0, 3 to 9): 清除以发送(Clear to Send),适用于硬件流控制。

⑤ SCKn: 时钟输出或输入引脚,适用于同步通信。

2. 发送和接收控制

见图中标注 ② 处。

-

通信模式和通信参数设置。

-

FIFO模式设置。

-

波特率生成器的时钟输入选择。

3. 数据寄存器和移位寄存器

见图中标注 ③ 处。

-

RSR接收移位寄存器将RXDn引脚接收到的串行数据转为并行数据。当接收到一帧数据,数据会被自动传入RDR/RDRHL或FRDRHL寄存器(在FIFO模式下), 并允许RSR继续接收更多数据,CPU无法直接访问RSR。

-

TSR传输移位寄存器用于传输串行数据。要进行数据传输,SCI首先自动将数据从TDR/TDRHL或FTDRHL寄存器(在FIFO模式下)传入到TSR中, 然后将数据发送到TXDn引脚,CPU无法直接访问TSR。

4. 波特率发生器

见图中标注 ④ 处。

用于控制波特率,具体由BRR(Bit Rate Rigister),MDDR(Modulation Duty Register)和SMR(Serial Mode Register)寄存器控制。 SMR在这里对波特率生成器的输入时钟进行选择,可以选择PCLK,PCLK/4,PCLK/16,PCLK/64,即PCLK/4n(n=0-3)。

四、UART波特率计算

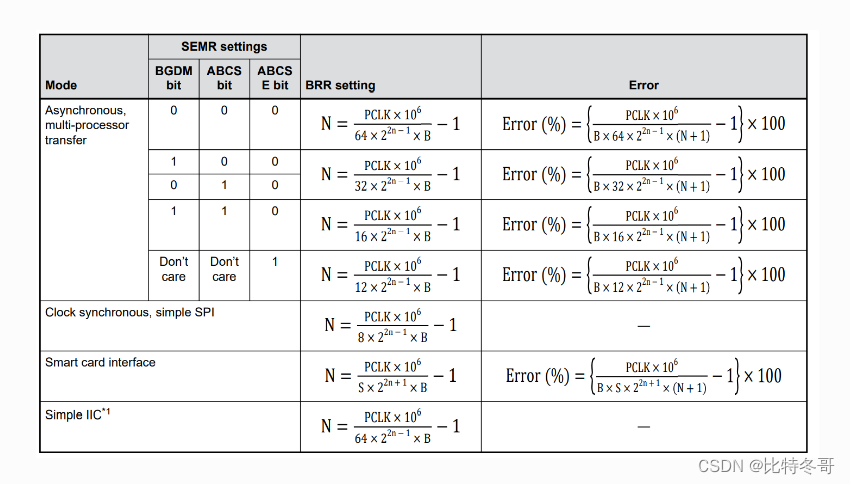

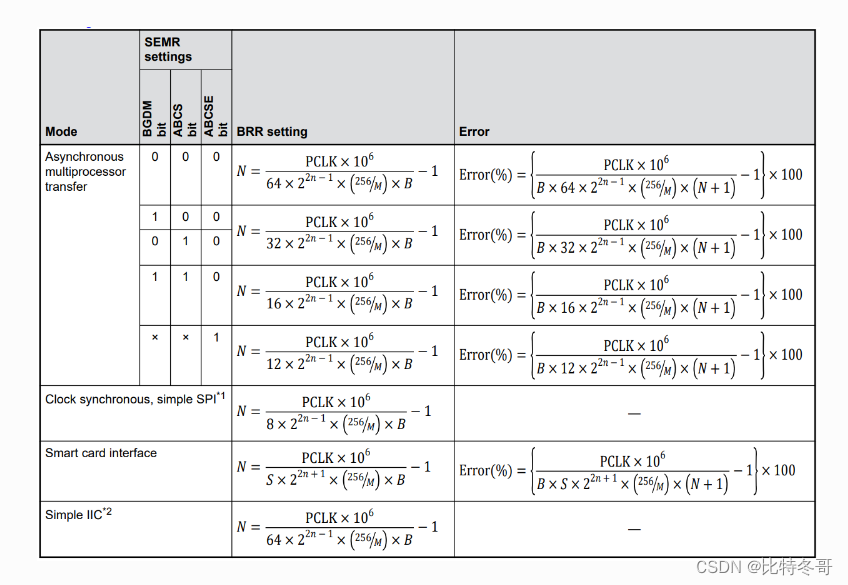

决定串口波特率的寄存器有BRR(Bite Rate Rigister),SEMR(Serial Extended Mode Rigister)和MDDR(Modulation Duty Register)。 波特率与寄存器的值的公式如下图所示。N表示BRR寄存器的值,B是波特率,PCLK是外设时钟的频率(单位:MHz)。 BGDM(Baud Rate Generator Double-Speed Mode Select) 在RA6M5中, SCI挂载在PHBIU(Peripheral High Speed Bus Interface Unit)总线上,使用时钟PCLKA,该时钟默认频率为100MHz。

由于N存放的是整数,故只能将公式计算出来的值进行四舍五入,这样肯定会存在误差(Error)。 例如,要配置当前波特率为115200bps。当PCLK=100MHz,BGDM=0,ABCS=0,ABCSE=0,n=1,按照上图公式,当前N为:

由于N是四舍五入取得的,故Error有可能是负数,因此这里取绝对值。

大多数时候会有多组参数符合波特率要求,由于误差越大,收发出错的可能性越大,虽然可以用奇偶校验避免这个问题, 但奇偶校验无法解决丢包问题,因此一般会选择误差最小的那组参数。例如: 同样是要求波特率为115200bps,但此时BGDM=1,ABCS=0,ABCSE=0,n=0,则此时的N为:

很明显这组参数的误差0.47%要小于上一组参数的3.12%,因此会选择这一组参数。

因为可选参数有很多组,所以需要遍历所有可选的参数组合来寻找误差小的那组参数,毫无疑问的对用户来说是相当繁琐的。 瑞萨官方当然也想到了这一点,因此读者在实际开发的过程中,可以直接使用FSP库的R_SCI_UART_BaudCalculate函数来计算出适当的参数组。 在通过Smart Configuration配置串口的时候,Smart Configuration也会将适当的参数组计算出来,存放到hal_data.c当中,用户可以直接调用。

如果需要更小的误差,则需要在SEMR的BRME位(Bit Rate Modulation Enable)写1,使能比特率调制功能。 此时波特率和寄存器之间的公式见下图。

该公式与未使用比特率调制功能时的公式大同小异,不管是BRR setting还是Error,都只是在分母添加了个系数(256/M), M是8位寄存器MDDR的值,取值范围(128~256),这极大的降低了波特率的误差。例如:

同样是要求波特率为115200bps,但此时BGDM=1,ABCS=0,ABCSE=0,n=0,M=184,则此时N为:

对比未使用波特率调制器时误差为0.47%,使用后为0.014%,误差降低到了原来的3%,效果可以说是相当的好,但是寻找效果最佳的M的值也是很繁琐的。 读者只需调用FSP库的R_SCI_UART_BaudCalculate函数,就能找到最适合的参数组。