- 程序查询方式

- 中断

- 中断源:向CPU提出中断请求的各种因素

- 直接内存存取(DMA):I/O与主存之间有一条直接的数据通路

- 通道方式:有自己通道指令但受CPU控制

- 外围处理机

- I/O接口组成与工作原理

- 接口功能:地址识别与设备选择,接受、保存CPU的I/O控制命令,反映外设的工作状态,信号转换,数据格式、码制转换、数据检错/纠错,传送数据,中断

- 组成:由数据缓冲寄存器器DBR、状态寄存器、命令寄存器、端口地址译码、控制逻辑和中断逻辑组成

- 用户视角端口:数据端口DBR、控制端口(命令寄存器)、状态端口(状态寄存器)

- 编址:

- 统一编址I/O与内存统一进行编址

- 独立编址:I/O与内存有各自独立的地址空间

- 接口类型:

- 传送方式:并行、串行

- 选择的灵活性:可编程、不可编程

- 通用性:通用接口、专用接口

- 数据传送的控制方式:中断、DMA

- I/O指令:80x86采用I/O独立编址:输入指令IN、输出指令OUT

- 长格式: IN AX/AL PORT、OUT PORT AX/AL

- 短格式:IN AX/AL DX、OUT DX AX/AL

- 长格式指令解释时间短、I/O速度快,短格式可以访问更多端口

- 数据传送的控制方法

- 程序查询I/O方式:CPU主动查询外设,和I/O串行工作

- 中断:随机发生,固定时间指令执行结束前CPU向接口发出中断查询信号,获取I/O中断请求,将INTR置1,在每条指令执行结束时CPU执行中断服务程序。

- 任何时刻只能为一个中断源的请求提供服务

- 中断系统:实现中断的软硬件

- CPU:接受中断请求信号的INTR、发出中断响应信号的INTA、中断状态触发器INT、中断允许状态标志EINT、将ENIT置为1的开中断指令STI、将ENIT清为0的关中断指令CLI、将程序断点弹回PC的中断返回指令IRET等

- 中断接口:中断请求触发器INTR、中断屏蔽触发器IM

- 主存:处理不同中断请求的中断服务程序

- 处理过程

- 中断请求

- 中断判优

- 中断响应:若EINT为1,CPU在每条指令执行的末尾扫描INTR引脚,有请求,CPU置INT为1,进入中断周期执行中断隐指令

- 中断隐指令:将程序断点(当前PC值)和标志位寄存器FR压入堆栈;关中断(清EINT为0),将中断处理程序首地址送入PC

- 中断服务:保护现场(中断点保护、CPU寄存器内容保护)、中断服务、恢复现场

- 形成中断入口地址:软件查询法、硬件向量法

- 可发成中断嵌套

- 中断返回:执行开中断指令STI和中断返回指令IRET

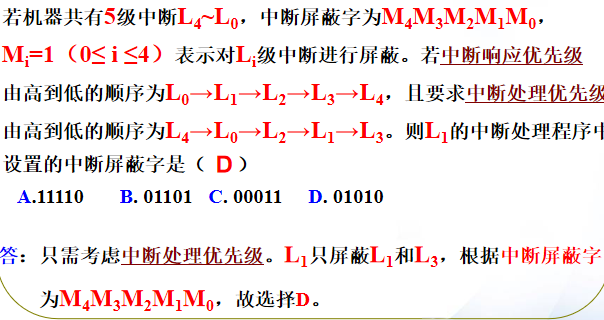

- 中断屏蔽:中断屏蔽字写入中断屏蔽寄存器IMR,可在运行时临时调整中断的服务顺序(优先级最高全为1)

- 8086微处理器的中断系统

- 硬件中断

- 不可屏蔽中断

- 可屏蔽中断

- 软件中断(内部中断):除法错误、定点加法溢出、断点中断、单步中断、中断指令INTn

- 除单步中断外,内部中断无法用软件禁止

- 屏蔽通过标志寄存器中断允许标志IF实现。处理器在每条指令执行的末尾扫描INTR引脚,检测到请求信号检查IF(STI和CLI有效)

- 中断周期:发出中断响应信号INTA,将标志寄存器FR压入堆栈、IF和TF清零,将寄存器CS\IP压入堆栈,根据中断类型号找到中断处理程序的入口地址,写入CS和IP

- 中断指令INTn:根据类型号n找到中断处理程序的入口地址

- 中断返回指令IRET:堆栈中顺序弹出3个字送入IP\CS\FR

- 中断优先级:软件中断(除数为0、中断指令、溢出中断)、不可屏蔽中断、可屏蔽中断、单步中断

- 中断特点:宏观并行、微观没有

- 硬件中断

- DMA:直接内存访问。直接实现、间接实现

- DMA控制器DMAC组成:主存地址寄存器、字计数器、设备地址寄存器、中断逻辑、控制/状态逻辑

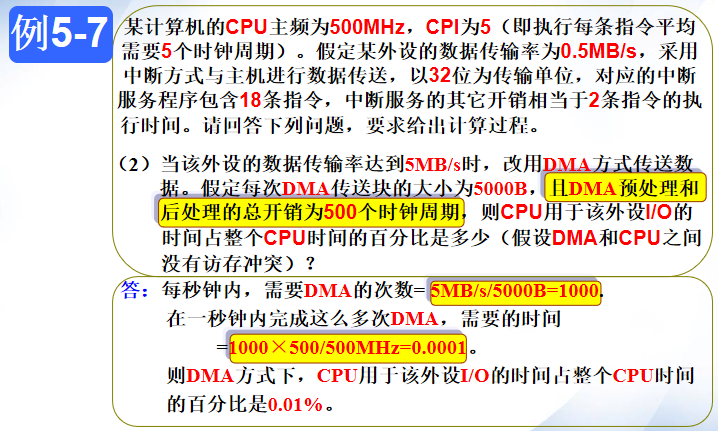

- 预处理-> 数据传输->后处理

-

- 数据传输模式:单字、成组、请求

- I/O向DMAC发出DMA请求信号DREQ、DMAC向CPU发出占用总线请求、CPU决定是否让出总线控制,总线允许信号、DMA应答信号DACK、与I/O进行数据交换、AR、WC增1、DMAC撤销HOLD信号释放总线

- CPU与DMAC分享主存/系统总线方式

- 停止CPU使用总线:CPU受到延误

- 周期挪用:CPU不使用总线时窃取周期传送

- CPU不占用总线访存时:CPU立即让出总线

- CPU占用总线访存:当前周期结束后让出总线

- CPU请求总线/即将访存:DMA优先级更高

- 交替使用:在周期内拆分使用

- 停止CPU使用总线:CPU受到延误

- 例题

-

计算机组成原理——I/O接口

猜你喜欢

转载自blog.csdn.net/qq_56061892/article/details/126139128

今日推荐

周排行