第二章

80386寻址体系

-

无分页的情况

计算步骤:首先取得该程序的段选择子,根据段选择子的内容找到段基地址(32位)、再取得当前指令所使用的偏移地址。

32位线性地址=段基地址(32位)+段内偏移(16位)+逻辑偏移(32位)

在没有分页的情况下,线性地址就是物理地址。

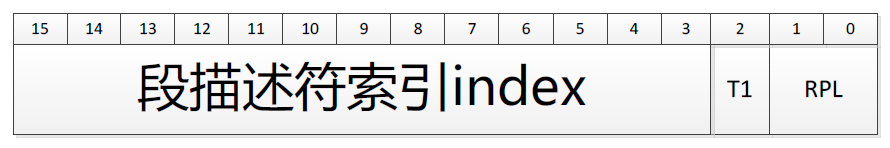

高13位为描述符索引,后面补三个0即为段描述符相对于基址的偏移(相当于前十三位乘8H和左移三位,整体将最后三位置零)

第2位为引用描述符表指示位

TI=0:从全局描述符表GDT中读取描述符TI=1:从局部描述符表LDT中读取描述符

第1和0位为请求特权级RPL

-

例:LDT的基址为00120000H,GDT的基址为0010 0000H,CS=1007H,求段描述符的地址解:CS = 0001 0000 0000 0111B所以有

TI=1,RPL=11B=3,且OFFSET(偏移地址) = 0001 0000 0000 0000H = 1000H那么段描述符的地址为

0012 0000H + 1000H = 0012 1000H -

例:LDT的基址为0060 2000H,GDT的基址为0050 1000H,CS=2006H,EIP=0200H求代码段在内存中的线性地址。解:题目中EIP指的是偏移地址所以首先计算出段描述符地址,

CS = 0010 0000 0000 0110B,即TI=1,RPL=10B=2也就有

LD = 2000H + 0060 2000H = 0060 4000H所以

线性地址 = LD + EIP = 0200H + 0060 4000H = 0060 4200H -

有分页的情况

回答80386处理器系统中,逻辑地址到物理地址转换的具体流程。

1. CPU首先从内存访问指令中获取段选择子和段内偏移地址

2. 根据段选择子从段表(GDT或LDT)中查询出对应的段描述符

3. 根据段描述符中的段基址和指令中的段内偏移地址生成32位的线性地址(页机制下的虚拟地址)

4. 32位的线性地址根据80386二级页表的设计,拆分成三个部分:高10位作为页目录项索引,中间次高10位作为页表项索引,低12位作为页内偏移地址。

5. 通过高10位的页目录项索引从一级页目录表中获取二级页表的物理页地址(通过物理页框号可得),再根据中间10位的页表项索引找到对应的物理页框。根据物理页框号与页内偏移地址共同生成最终的物理地址,进行物理内存的访问。

微处理器体系结构的改进

-

储存子系统的分层

关键的问题是:以合理的价格搭建出容量和速度都满足要求的储存系统,根本是需要协调速度、容量和成本三者之间的矛盾

-

二级结构:内存(解决读写速度)+外存(解决储存容量)

-

四级结构:寄存器+Cache+主存(字节编址)+辅存

Cache-主存结构解决高速度和低成本的矛盾

主存-辅存结构利用虚拟存储器解决大容量与低成本的矛盾

-

流水线:是将计算机指令处理过程拆分为多个步骤,并通过多个硬件处理单元并行执行来加快指令执行速度。

-

超标量:超标量体系结构的CPU在一个时钟周期可以同时分派多条指令在不同的执行单元中被执行,这就实现了指令集的并行。

-

流水线的问题:只有在满载时,才能发挥出最佳效率;流水线级数不能无限增加;增加了硬件成本;会引入延迟和额外开销,限制了流水线的深度;当各阶段操作存在关联时会引起流水线中断。

寻址方式

-

立即寻址:操作数作为指令的一部分

MOV AX,1234H ;小端序:高位:12->AH 低位:34->AL -

直接寻址:指令所要的操作数存放在内存中,在指令中直接给出该操作数的有效地址。

MOV AX,[1234H] ;MOV 不能直接进行两地址之间的内存交换 -

寄存器寻址:操作数存放在寄存器中,通过指定寄存器来获取数据

MOV AX,BX -

寄存器间接寻址:操作数有效地址只在

SI、DI、BX、BP这四个寄存器之一中MOV AX,[DI] ;[]取内存单元 -

寄存器相对寻址:操作数的有效地址是一个基址寄存器(

BX、BP)或变址寄存器(SI、DI)的值加上指令中给定的8位或16位偏移量之和MOV AX, [BX + 1234H] ;或者 MOV 1234H[BX] -

基址变址寻址:操作数的有效地址由基址寄存器(

BX、BP)之一的值与变址寄存器(SI、DI)之一的值相加得到MOV AX, [BX + DI] ;MOV AX, [BX][SI] -

相对基址变址寻址:相比基址变址寻址增加了偏移量

MOV AX, 1234H[BX + DI]

习题

-

8086CPU把1MB空间划分为若干逻辑段,每段最多可含64KB的储存单元。

-

8086CPU可寻址访问的最大I/O空间为64KB

-

8086系统中内储存器地址空间为1M,而在进行I/O读写时,有效的地址线是低16位。

-

若8086CPU主频为8MHz,则其基本总线周期为500ns

-

虚拟字节地址7FFFH-8000H在物理地址空间上可能不连续

-

?8086的CPU硬件中断引脚有2个,INTR/NMI是可屏蔽中断信号和不可屏蔽中断信号 INTA是中断响应

-

8086CPU对内存读/写操作,需两个总线周期的操作是从奇地址读/写一个字(16位数据线,从奇地址读取,则不是对其的方式)

-

计算机储存器的分段和分页管理方式中,段与段之间是可重叠的,页与页之间不可重叠

-

8086的CPU中指令队列课以储存6个字节的指令代码

-

储存器分页管理方式中,构造多级页表的目的是可以减少页表项

使用多级页表可以节省页表内存。使用一级页表,需要连续的内存空间来存放所有的页表项。多级页表通过只为进程实际使用的那些虚拟地址内存区请求页表来减少内存使用量

-

8086和80386内部都含有指令流队列

-

保护模式下,奔腾处理器的段寄存器用于选择段描述符

-

当8086的引脚信号M/IO=1、RD=0、WR=1时,CPU完成的操作是储存器读,(读写低电平有效,M表示存储器)

-

在8086系统中,一个总线周期完成一次储存器读写

-

四级流水线CPU操作:取指、译码、执行、回写

-

16位处理器8086读写一个连续的双字节数据,总线周期数可能一个也可能两个(当对齐时,一个周期;不对齐时,两个周期)

-

CPU在调用子程序时,返回地址会被压入堆栈

-

Intel X86和AMD的处理器具有指令集兼容性,指令集是同一套。

-

为X86保护方式设计的程序不能在8086中运行,其原因是,寻址方式不兼容

-

Intel处理器实方式和保护方式的本质区别是不同的任务管理机制

-

CPU在调用子程序时,返回地址会被压入堆栈

-

Intel X86和AMD的处理器具有指令集兼容性,指令集是同一套。

-

为X86保护方式设计的程序不能在8086中运行,其原因是,寻址方式不兼容

-

Intel处理器实方式和保护方式的本质区别是不同的任务管理机制