HDMI 2.1 Transmitter Subsystem v1.2 PG350

- HDMI2.1 Transmitter Subsystem (Xilinx PG350)

- XILINX SUPPORT

- 参考来源

- **(仅供学习交流使用,转载请注明出处)**

HDMI2.1 Transmitter Subsystem (Xilinx PG350)

1、介绍

- HDMI2.1发送子系统是一个包含了一组hdmi子核的分层次的IP。它是一个现成的IP,不用手动集成hdmi子核。

- HDMI2.1 发送子系统是一个包含所有必要逻辑的功能丰富的软核,与PHY层配合提供HDMI编码功能。

- 接收视音频数据转换为HDMI流,后将流发给PHY Layer。

2、特性

- 符合 hdmi2.1 标准

- 动态支持 FRL 和 TMDS

- 动态支持FRL带宽(4x12G\10G\8G\6G、3x6G\3G)

- 动态支持TMDS最高到3*6G

- 最高支持分辨率10240*4320 p30

- 最高支持10kp60(yuv420)

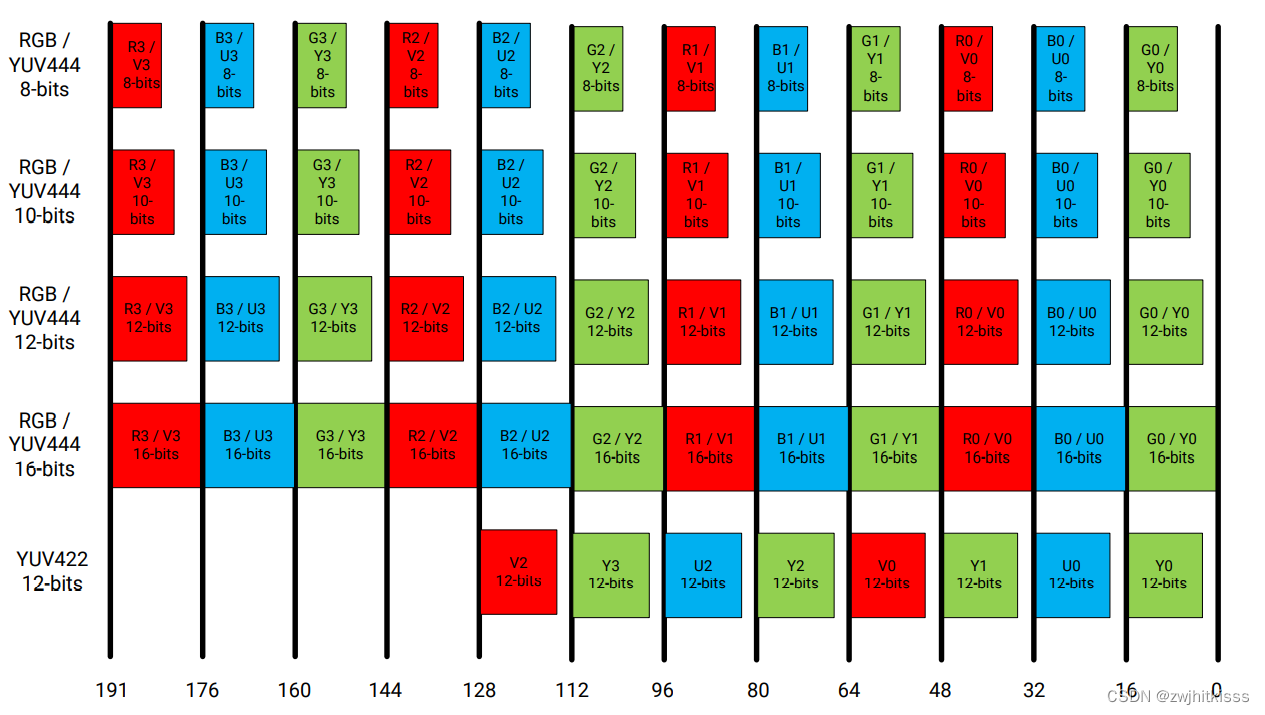

- 支持8、10、12、16 bpc

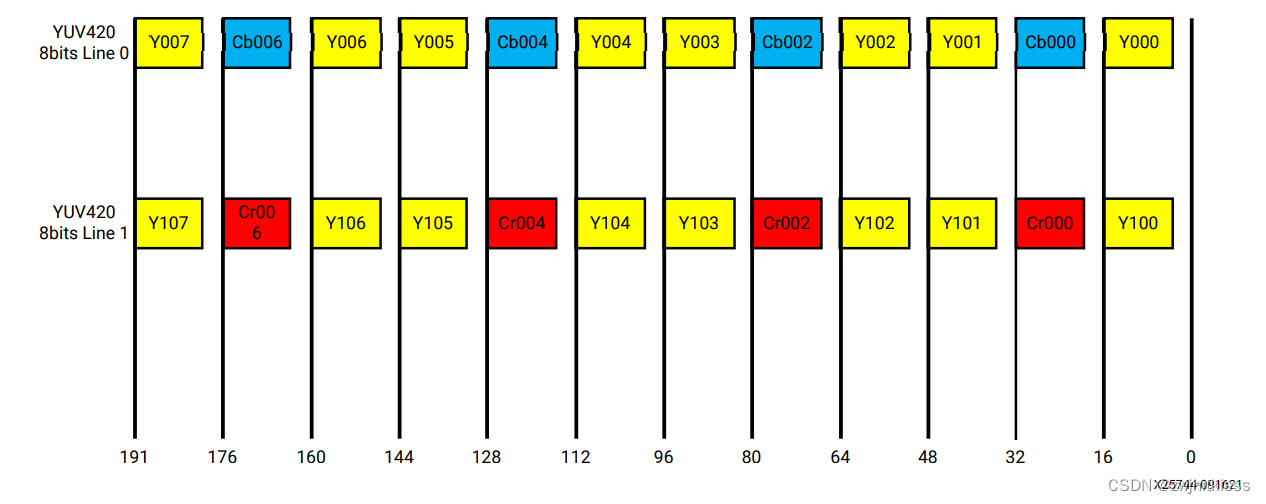

- 支持RGB、YUV422 420 444

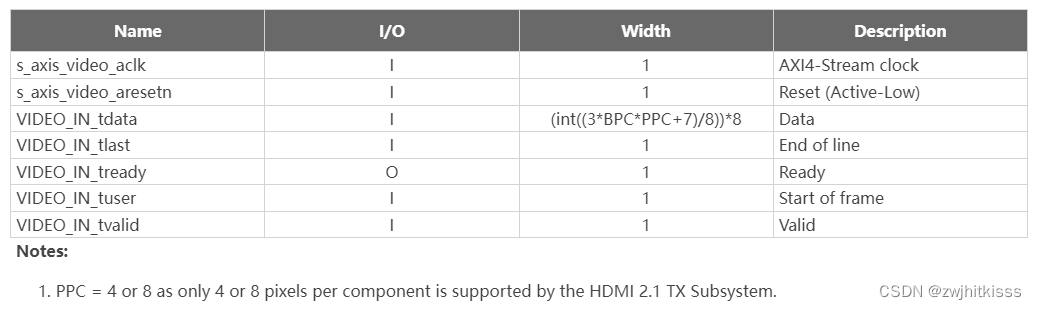

- 支持4、8ppc axis video 输入

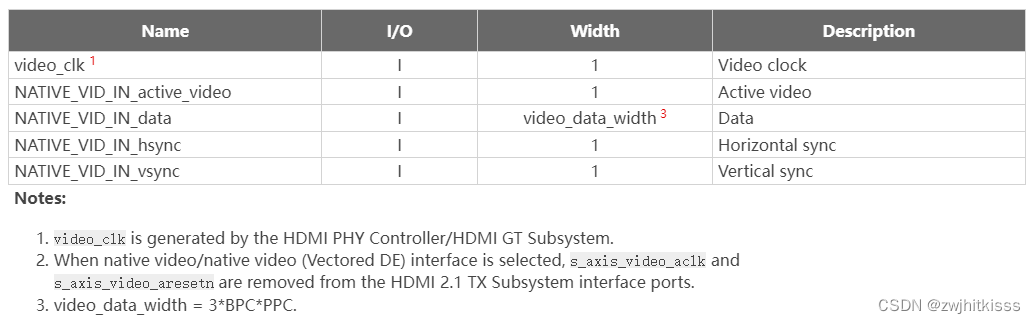

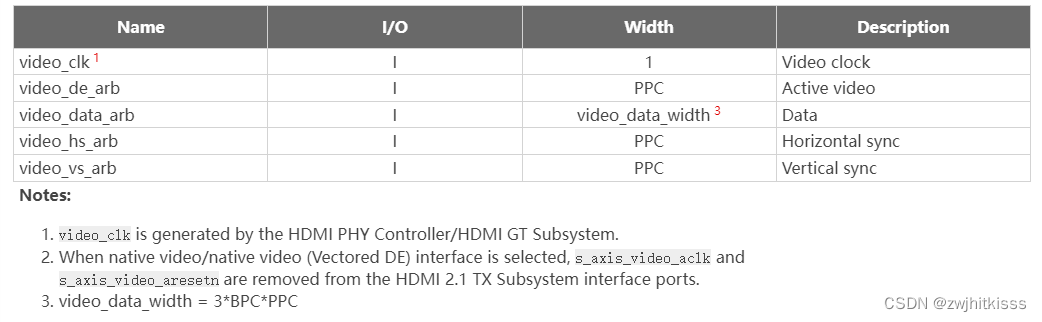

- 支持4ppc native video 输入,支持 4ppc native video(Vectored DE) 输入

- 支持最高32 channels pcm音频

- HBR音频

- 3D audio

- 支持可选择的HDCP 2.3/1.4

- INFO FRAMES

- DDC

- 支持DDC时钟拉伸(DDC CLOCK STRETCHING)

- 支持热拔插和HPD信号极性控制

- 支持HDR视频传输(Dynamic Range and Mastering info frames)

- Traditional Gamma - SDR

- Traditional Gamma - HDR

- HDR 10 - SMPTE ST 2084

- Hybrid Log Gamma (HLG)

- 支持 enhanced gaming and media features

- Variable Refresh Rate (VRR)

- Quick Frame Transport (QFT)

- Auto Low Latency Mode (ALLM)

- Quick Media Switching (QMS)

- 支持动态HDR

- CTA 861-H HDR dynamic metadata extended info fram

- 支持HDR10+ Forum VSIF

3、IP FACTS

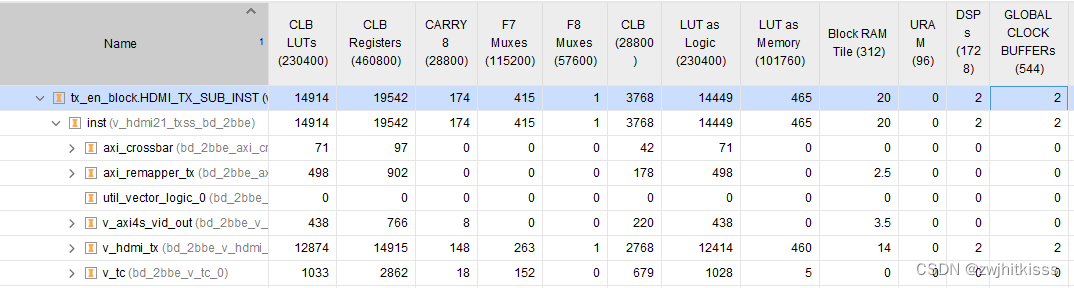

资源占用(图)

4、应用

消费级设备

DVD、多媒体播放器、数字电视、摄像机、数字平板、手机

专业级设备

专业相机、视频选择器、转换器、大屏应用、大众显示信号

5、不支持特性

Lip sync

CEC

HEAC

Dual view

eARC

Multi-stream audio

Digital Stream Compression (DSC)

Pixel repetition is not supported for YCbCr 422 in AXI Stream Mode

6、IP介绍

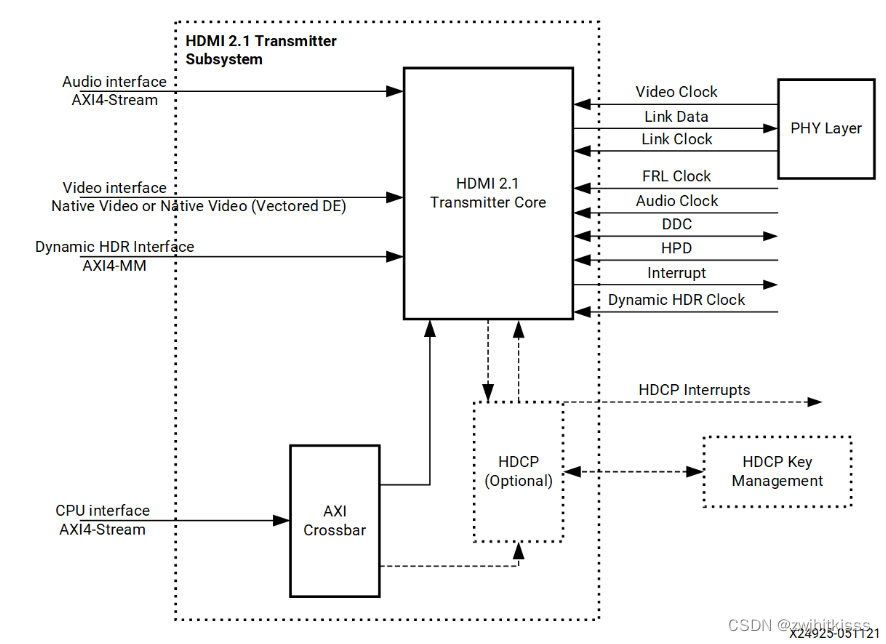

配合 HDMI PHY Controller(PG333)/HDMI GT Subsystem(PG334)使用。

AXI4S下,IP核使用了以下子核:

- HDMI 2.1 Transmitter core

- Video Timing Controller (VTC)

- AXI4-Stream to Video Out Bridge

- AXI Remapper TX

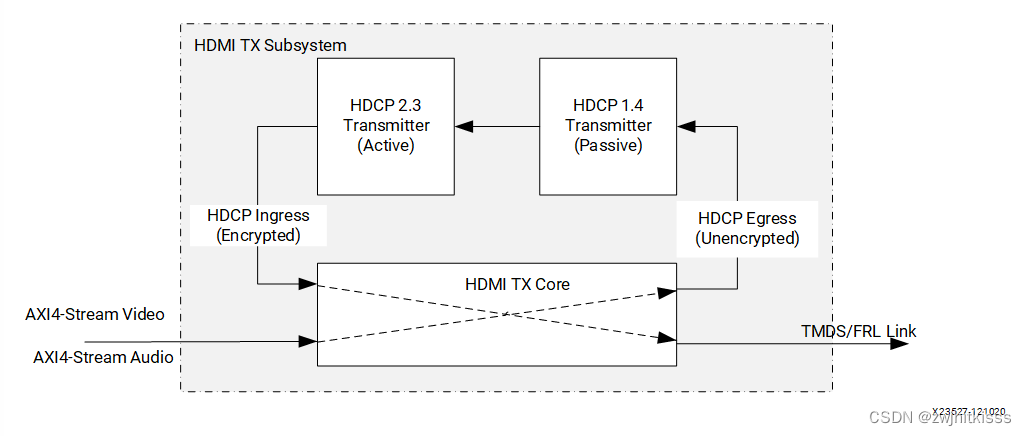

IP核包含可选择的HDCP 2.3 controller and HDCP 1.4 controller,需要AXI Timer作为辅助核。

支持以下三种接口作为输入

- AXI4-Stream Video interface

- Native Video interface

- Native Video (Vectored Data Enable (DE)) interface

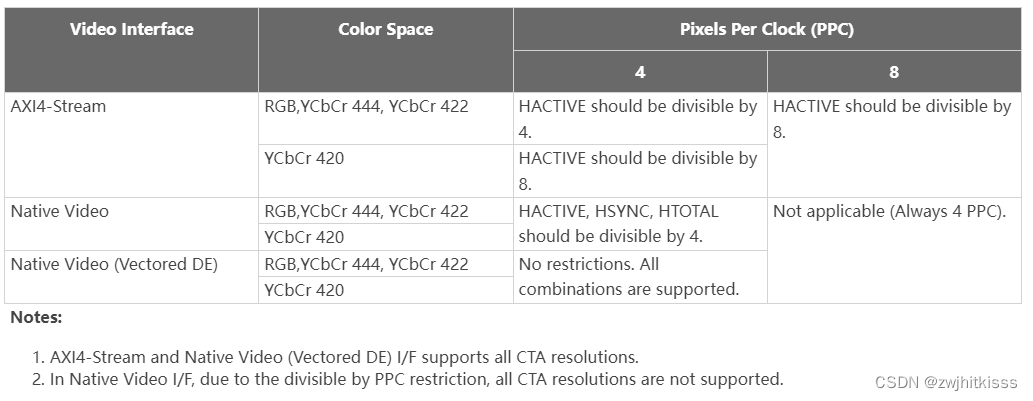

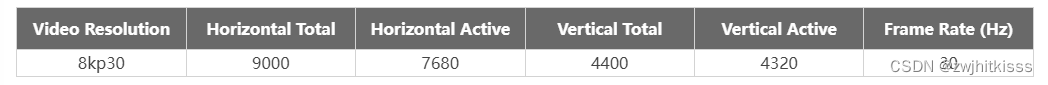

支持的视频时序(图)

AXI4S下支持8kp48, 8kp50, and 8kp60/10kp60 YUV420,需要设置PPC为8。

AXI4S下,IP核支持YUV444、RGB像素点复制,使用native/Native DE接口时,自己做像素点复制。

AXI4S视频Block Diagram(图)

Native Video or Native Video (Vectored DE) Block Diagram(图)

AXI4-Stream to Video Out Bridge

AXI4-Stream to Video Out LogiCORE IP Product Guide(PG044)

Vivado Design Suite: AXI Reference Guide(UG1037)

AXI4-Stream Video IP and System Design Guide(UG934)

Video Timing Controller

Video Timing Controller LogiCORE IP Product Guide(PG106)

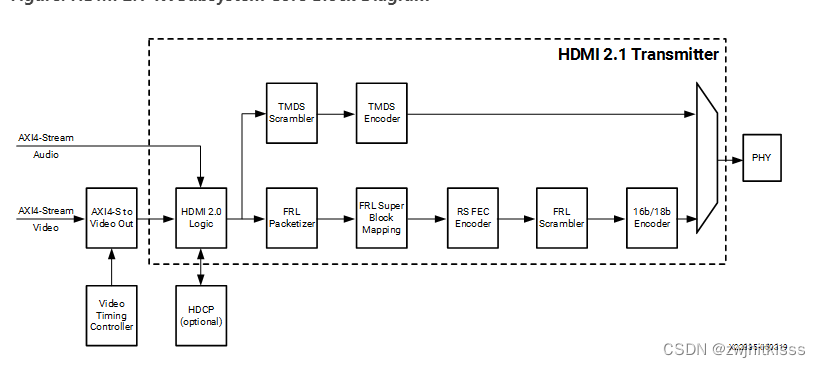

HDMI 2.1 Transmitter 结构

HDMI2.1发送子系统根据处理器选择的视频格式将视频频流处理成HDMI格式。

HDMI2.1发送子系统根据接收端的能力支TMDS及FRL。

拥有两条独立的数据链路,一条支持TMDS编码,另一条支持打包成FRL包,添加FEC,进行16b/18b编码。

物理层受HDMI PHY Controller /HDMI GT Subsystem控制,GT每组transceiver最大支持到12G。

HDMI 2.1 TX Subsystem Core Block Diagram(图)

GT接口不支持TMDS的电平标准,需要外接电平转换器来支持TMDS(XILINX推荐使用ON Semiconductor NB7NQ621M)。

HDCP

FRL下用HDCP2.3

TMDS的UHD用HDCP2.3

以下分辨率用HDCP1.4

IP核通过调用API来保证同一时间只有一个HDCP核在工作状态

HDCP 1.4 and HDCP 2.3 over HDMI Transmitter(图)

HDCP 1.x Product Guide(PG244)

HDCP 2.2 LogiCORE IP Product Guide(PG249)

HDCP SPCE

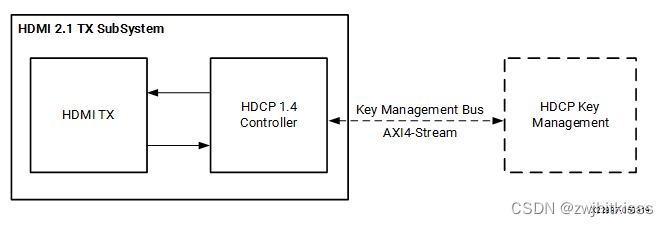

HDCP 1.4 Key Management Bus (AXI4-Stream)(图)

HDCP1.4独立于HDMI2.1发送子系统。

对于HDCP2.3,用户应用程序负责在HDCO2.3驱动存储和取出KEY。

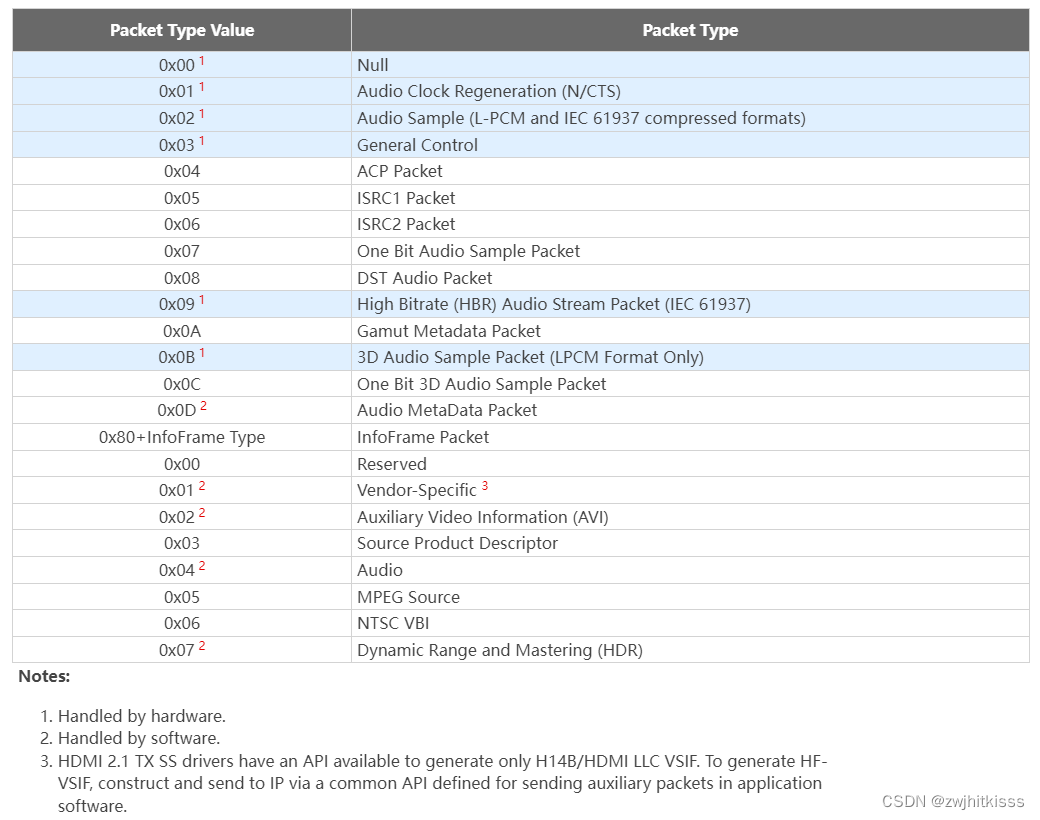

辅助数据包

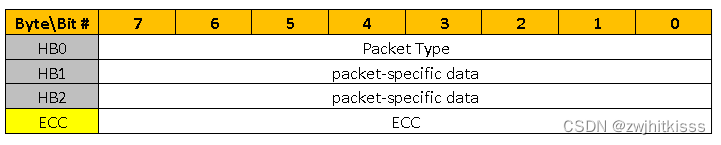

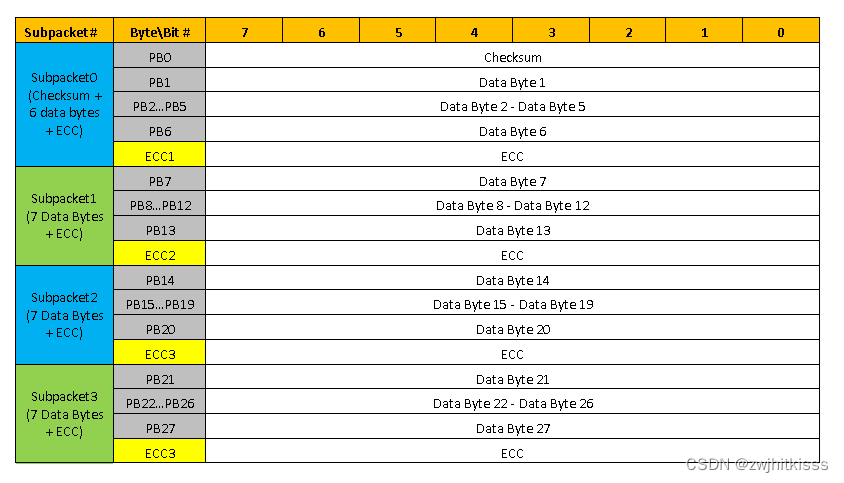

数据包包括4字节包头和32字节包内容。

包头包括3字节数据和1字节 BCH、ECC

包内容由四个子包组成,每个子包包括7字节数据和1字节 BCH、ECC

Hardware and Software Packet Types(图)

软件发auxiliary packets

API

u32 XV_HdmiTxSs1_SendGenericAuxInfoframe(XV_HdmiTxSs1 *InstancePtr, void *AuxPtr);

//InstancePtr is a pointer to the HDMI 2.1 TX Subsystem instance.

//Aux is a 36 byte array contains the complete AUX packet.

AUX 数据结构

typedef union {

u32 Data;

u8 Byte[4];

} XHdmiC_AuxHeader;

typedef union {

u32 Data[8];

u8 Byte[32];

} XHdmiC_AuxData;

typedef struct {

XHdmiC_AuxHeader Header;

XHdmiC_AuxData Data;

} XHdmiC_Aux;

软件处理the Vendor Specific InfoFrame (VSIF), the Auxiliary Video Information (AVI) InfoFrame, the Audio InfoFrame, and the Dynamic Range and Mastering InfoFrame,数据结构查阅CTA-861-H。

typedef struct XHDMIC_AVI_InfoFrame {

unsigned char Version;

XHdmiC_Colorspace ColorSpace;

u8 ActiveFormatDataPresent;

XHdmiC_BarInfo BarInfo;

XHdmiC_ScanInfo ScanInfo;

XHdmiC_Colorimetry Colorimetry;

XHdmiC_PicAspectRatio PicAspectRatio;

XHdmiC_ActiveAspectRatio ActiveAspectRatio;

unsigned char Itc;

XHdmiC_ExtendedColorimetry ExtendedColorimetry;

XHdmiC_RGBQuantizationRange QuantizationRange;

XHdmiC_NonUniformPictureScaling NonUniformPictureScaling;

unsigned char VIC;

XHdmiC_YccQuantizationRange YccQuantizationRange;

XHdmiC_ContentType ContentType;

XHdmiC_PixelRepetitionFactor PixelRepetition;

u16 TopBar;

u16 BottomBar;

u16 LeftBar;

u16 RightBar;

} XHdmiC_AVI_InfoFrame;

typedef struct XHdmiC_Audio_InfoFrame {

unsigned char Version;

XHdmiC_AudioChannelCount ChannelCount;

XHdmiC_AudioCodingType CodingType;

XHdmiC_SampleSize SampleSize;

XHdmiC_SamplingFrequency SampleFrequency;

u8 CodingTypeExt;

u8 ChannelAllocation;

XHdmiC_LFEPlaybackLevel LFE_Playback_Level;

XHdmiC_LevelShiftValue LevelShiftVal;

unsigned char Downmix_Inhibit;

} XHdmiC_AudioInfoFrame;

typedef struct {

u8 Version;

u32 IEEE_ID;

XHdmiC_VSIF_Video_Format Format;

union {

u8 HDMI_VIC;

XHdmiC_3D_Info Info_3D;

};

} XHdmiC_VSIF;

typedef struct XHdmiC_DRM_InfoFrame {

XHdmiC_DRM_EOTF EOTF;

XHdmiC_DRM_Static_Metadata_Descp_Id Static_Metadata_Descriptor_ID;

struct {

u16 x,y;

} disp_primaries[3];

struct {

u16 x,y;

} white_point;

u16 Max_Disp_Mastering_Luminance;

u16 Min_Disp_Mastering_Luminance;

u16 Max_Content_Light_Level;

u16 Max_Frame_Average_Light_Level;

} XHdmiC_DRMInfoFrame;

GCP(General Control Packet)

void XV_HdmiTxSs1_SetGcpAvmuteBit(XV_HdmiTxSs1 *InstancePtr);

void XV_HdmiTxSs1_ClearGcpAvmuteBit(XV_HdmiTxSs1 *InstancePtr);

void XV_HdmiTxSs1_SetGcpClearAvmuteBit(XV_HdmiTxSs1 *InstancePtr);

void XV_HdmiTxSs1_ClearGcpClearAvmuteBit(XV_HdmiTxSs1 *InstancePtr);

Enhanced Gaming and Media Features

MVRR multimedia video refresh rate

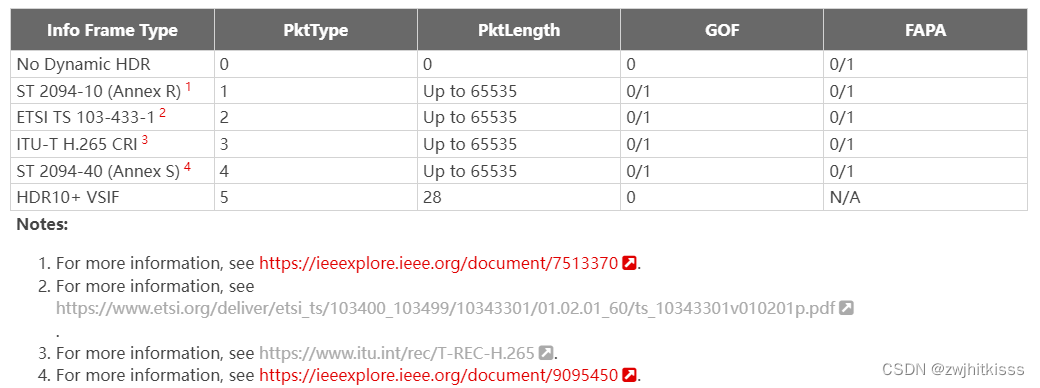

Dynamic HDR

- Dynamic HDR在IDE上可以选择,勾选后添加一组m_mm接口。

- 支持CTA-861-H动态HDR信息帧

- SEI message参考 ETSI TS 103 433-1

- color remapping information SEI message

typedef struct

{

u64 Address; /**< Dynamic HDR packet buffer address */

u16 PktType; /**< 16 bit Packet Type */

u16 PktLength; /**< 16 bit Packet Length */

u8 GOF; /**< GOF Value 0 or 1 only */

u8 FAPA; /**<FAPA Location 0 or 1 only */

} XV_HdmiTxSs1_DynHdr_Config;

动态HDR配置结构(图)

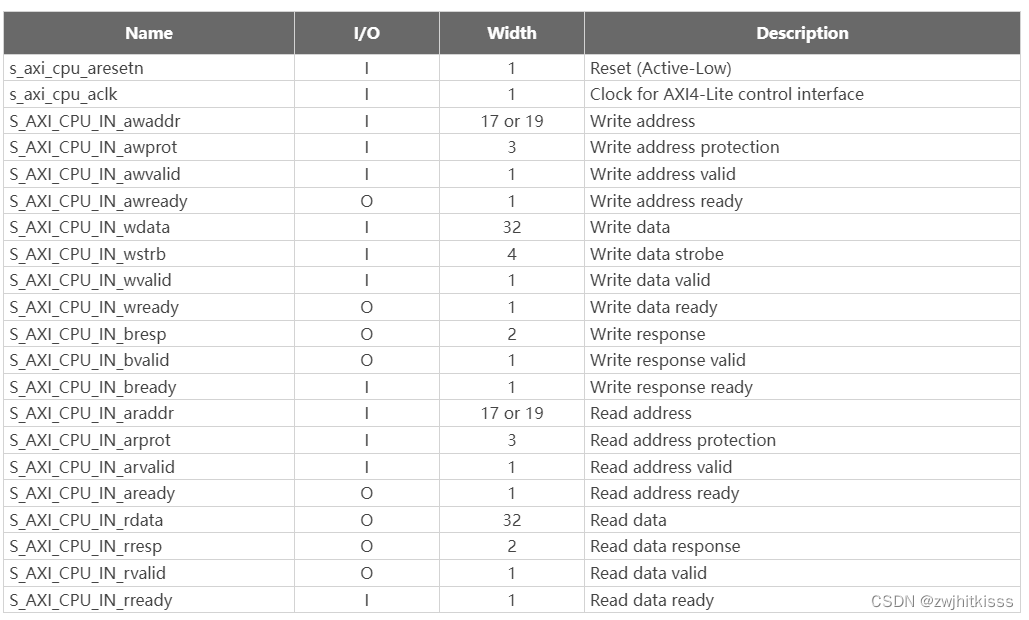

7、端口描述

AXI4-Lite

支持AXI4-Lite作为控制接口,AXI4-Lite支持单拍读写,不支持brust模式。

AXI4-Lite 寄存器位宽为17b或19b。

AXI4S

Native Video Interface

Native Video (Vectored DE) Interface

使用Native Video (Vectored DE) Interface时,视频时序不需要被4、8ppc整除。

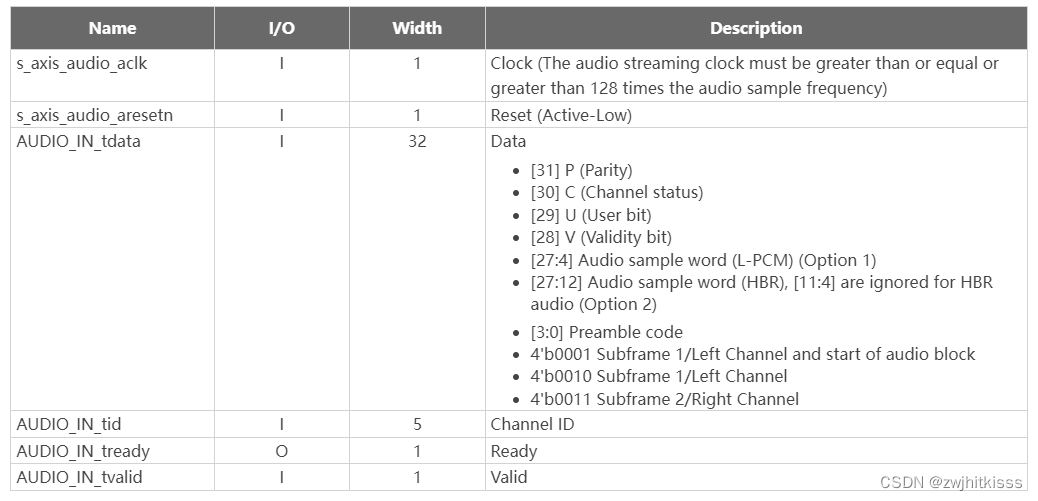

Audio Input Stream Interface

支持24bit L-PCM或16bit HBR音频采样(IEC 60958)

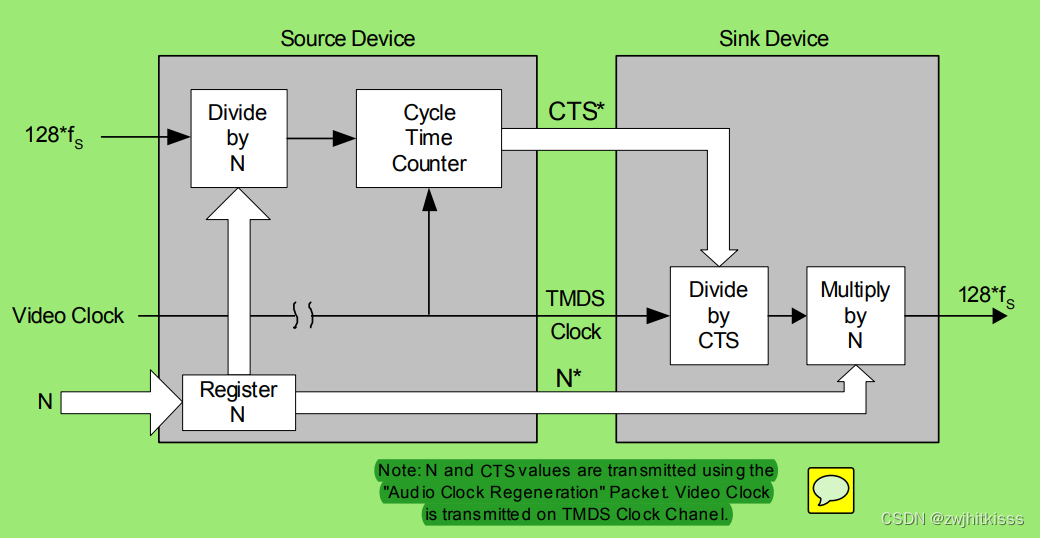

Audio Clock Regeneration Interface

CTS:ACR Cycle Time Stamp

N:Audio Clock Regeneration Value

具体参数值设置参考HDMI1.4\2.1标准

直通模式下,RX、TX FRL速率可能不同,请不要直连

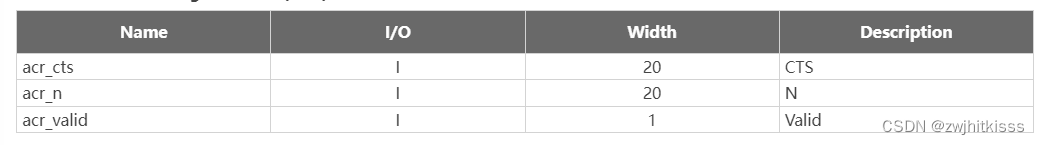

Data Display Channel Interface

所谓DDC就是IIC,用于HDMI设备source和sink通信的低速接口。

Miscellaneous Signals

locked:一般ip核时钟配置正确,输入正确数据,axis转video模块就会锁定。

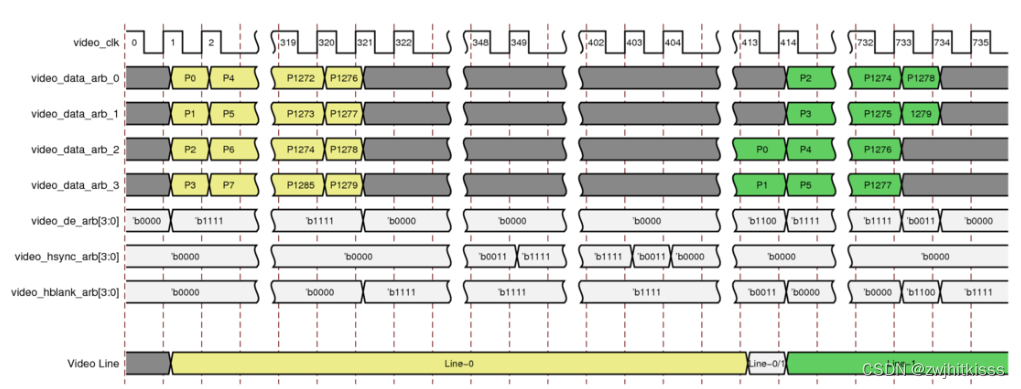

video_clk:tmds下为视频时钟,frl下与video_clk_in协同使用,用来转换axi4s视频到原始视频格式。

video_cke_in:video_clk使能信号,用于在HDMI RX和HDMI TX核之间做同步(直通模式),中间加上frame buffer或视频源不来自与HDMI RX时不建议使用。

Clocks and Resets

复位需要等待时钟稳定后拉起

8、IP设计

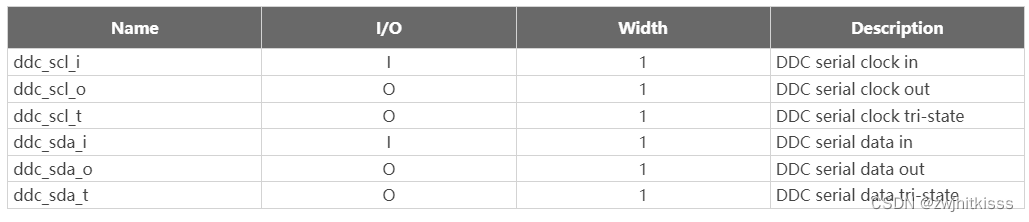

音频流

需要按照CH0, CH1, etc.格式给IP核音频,顺序错误可能会引起传输错误。

在IP里,音频声道数由软件驱动控制。需要保证驱动设置和音频流声道数及TID对应。

支持L-PCM (IEC 60958, Packet Type 0x02), HBR (Packet Type 0x09),

and 3D Audio (Packet Type 0x0B) ,API设置音频格式。

void XV_HdmiTxSs1_SetAudioFormat(XV_HdmiTxSs1 *InstancePtr,

XV_HdmiTx1_AudioFormatType format)

//InstancePtr is a pointer to XV_HdmiTxSs1 instance.

//the format is a selector of Audio Format.

typedef enum {

XV_HDMITX1_AUDFMT_LPCM = 0, /*L-PCM*/

XV_HDMITX1_AUDFMT_HBR, /*HBR*/

XV_HDMITX1_AUDFMT_3D, /*3D Audio*/

} XV_HdmiTx1_AudioFormatType;

当使用多声道音频,保证不用的音频通道置零,否则会出现声道交换。

HDMI标准要求所有的音频包被打包成偶数个(table 7-6 of the HDMI specification),当使用奇数声道时,在最后添加一路静音声道,数据全部置零。

视频输入

AXI4S视频接口支持4、8ppc,8、10、12、16bpc,YUV44、YUV420、RGB

对于YUV422,色深为12bpc

Four Pixels Data Format (Max Bits Per Component = 16)(图)

YUV420 Color Space Four Pixels Data Format (Native)(图)

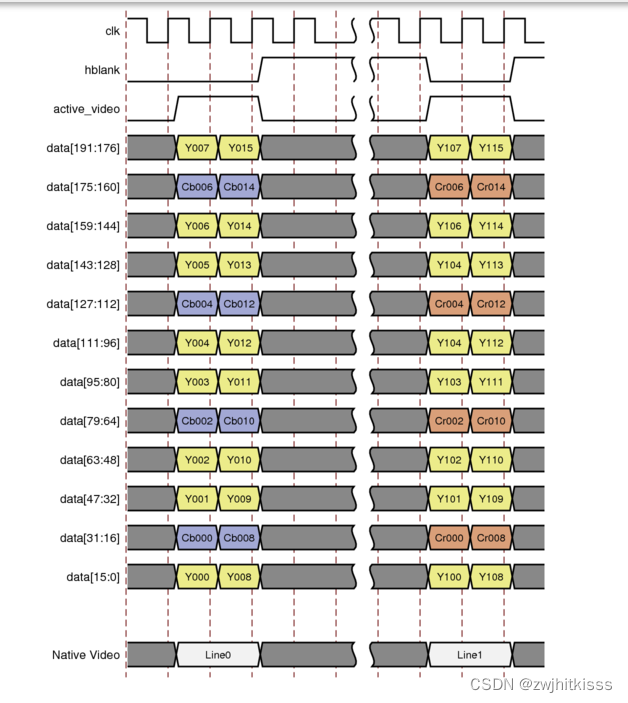

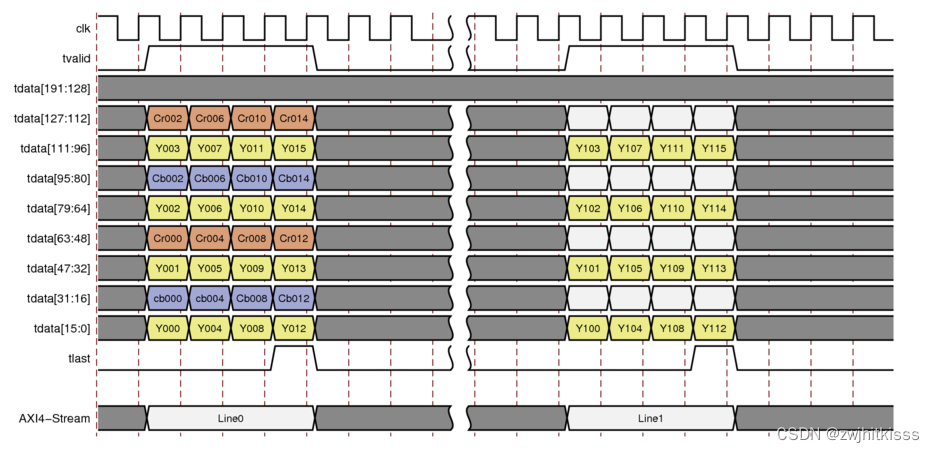

Native HDMI Video Interface (Four Pixels per Clock)(图)

YUV 4:2:0 AXI4-Stream Video Data (Four Pixels per Clock)(图)

在YUV420格式下,AXI4S和Native Video之间需要做数据转换(重新映射)。

IP核会自带一个AXI4S YUV420转Native Video YUV420的模块(AXI Remapper)。

Native DE HDMI Video Interface (Four Pixels per Clock)(图)

Interlaced Video

支持Interlaced Video,AXI4S下控制fid信号,Native Video下需要控制相关时序。

1920*1080 @50HZ HDMI视频时序(图)

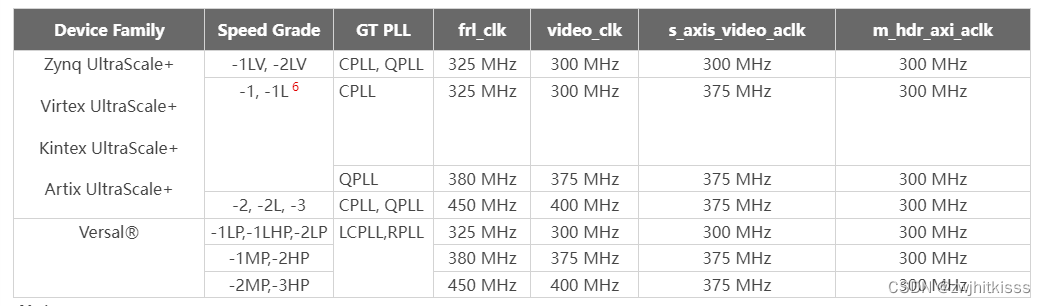

时钟域

共有6个时钟域。

s_axi_cpu_aclk:处理器时钟域,推荐使用100MHz。

frl_clk:一个固定频率的自由时钟,用于内部数据处理,可以来自mmcm或时钟管脚。

s_axis_video_aclk:自由时钟,AXI4S运行在这个时钟域下,AXI4-Stream to Video Out bridge转化数据到video_clk时钟域。

video_clk:来自于HDMI PHY Controller/HDMI GT Subsystem,tmds下为标准视频时钟,frl下为固定频率时钟,配合video_cke_in使用。

m_hdr_axi_aclk:自由时钟,用来处理动态HDR的MM格式数据。

上图中,frl_clk为指定值。s_axis_video_aclk、m_hdr_axi_aclk为最大值。

frl_clk没有达到以上指定值时,FRL可能无法训练到器件速度等级\GT PLL支持的最大速率。

Ultrascale+ -2器件上设定frl_clk为400MHz时测试只能达到4x10G的FRL速率。

s_axis_video_aclk需满足:s_axis_video_clk >= HActiveVactiveFrame Rate/PPC。

m_hdr_axi_aclk也可以降低频率,最小频率由最大分辨率和动态HDR metadata大小决定。

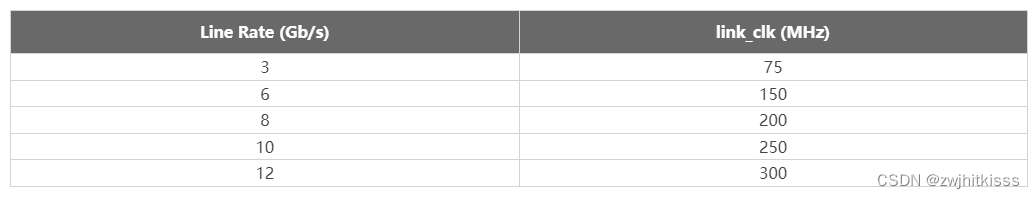

link_clk:TMDS下为TMDS clk,FRL下 link_clk = line rate/40 as the GT data width is set to 40 bits parallel bus。

s_axis_audio_aclk,s_axis_audio_aclk = 512 × audio sample rate。

在采样频率为48KHZ时,s_axis_audio_aclk 应当为24.576MHz。

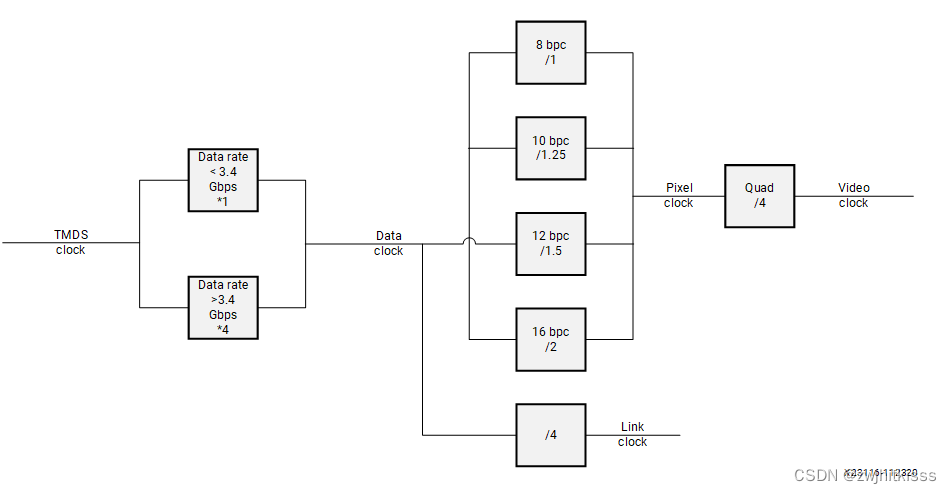

TMDS Clocking Structure(图)

| 时钟 | 频率 | 例子 |

|---|---|---|

| TMDS | = 1/10 data rate(for data rates < 3.4 Gb/s) | Data rate = 2.97 Gb/s TMDS clock = 2.97/10 = 297 MHz |

| TMDS | = 1/40 data rate(for data rates > 3.4 Gb/s) | Data rate = 5.94 Gb/s TMDS clock = 5.94/40 = 148.5 MHz |

| Data | = TMDS clock(for data rates < 3.4 Gb/s) | Data rate = 2.97 Gb/s Data clock = TMDS clock * 1 = 297 MHz |

| Data | = TMDS clock * 4(for data rates > 3.4 Gb/s) | Data rate = 5.94 Gb/s Data clock = TMDS clock * 4 = 594 MHz |

| Link | = clock=data clock/4 | Link clock = 297 MHz/4 = 74.25 MHz |

| Pixel | = 8 bpc pixel clock = data clock | Data clock = 297 MHz For 8 bpc pixel clock = 297 MHz |

| Pixel | = 12 bpc pixel clock = data clock/1.5 | Data clock = 445.5 MHz For 8 bpc pixel clock = 297 MHz |

| Video | = clock = pixel clock/4 | 297 MHz/4 = 74.25 MHz for quad pixel wide interface |

计算的时候,先从video_clk开始计算,算出tmds_clk。

FRL 8KP30 CLOCK(图)

- Pixel clock = Htotal × Vtotal × Frame Rate = 9000 x 4400 x 30 = 1,188,000,000 = 1188 MHz

- Video clock = (Pixel clock)/PPC = 1188/4 = 297 MHz

- Data clock = (Pixel clock) x BPC/8 = 1188 x 8/8 = 1188 MHz

- Link clock = (Data clock)/PPC = 1188/4 = 297 MHz

- 带宽计算:The total bandwidth needed = (Pixel clock) x BPC (bits per component) x 3 (3 components for RGB video) x 18/16 (HDMI 2.1 uses 16/18 encoding scheme) = 1188 x 8 x 3 x 18 / 16 = 32.076 Gb/s

- active pixel clock计算:

- Active Pixel clock = HActive × Vactive × Frame Rate = 7680 x 4320 x 30 = 995,328,000 = 995.328 MHz

- s_axis_video_clk = (Active Pixel clock)/PPC = 995.328/4 = 248.832 MHz

- HDMI 2.1 specification中定义了如何压缩不携带辅助数据的空区,所以4*8G可以支持8KP30。

- 理论上可以支持8KP60制式如下:

| 色度 | BPC | 带宽 |

|---|---|---|

| YUV420 | 8 | 32.1Gb/s |

| YUV420 | 10 | 40.1Gb/s |

| YUV420 | 12 | 48.1Gb/s |

| YUV422 | 8 | 42.8Gb/s(XILINX未测试) |

9、设计流程

Designing IP Subsystems using IP Integrator(UG994)

Designing with IP(UG896)

Getting Started(UG910)

设计和生成IP

To view the parameter value, run the validate_bd_design command in the Tcl console.

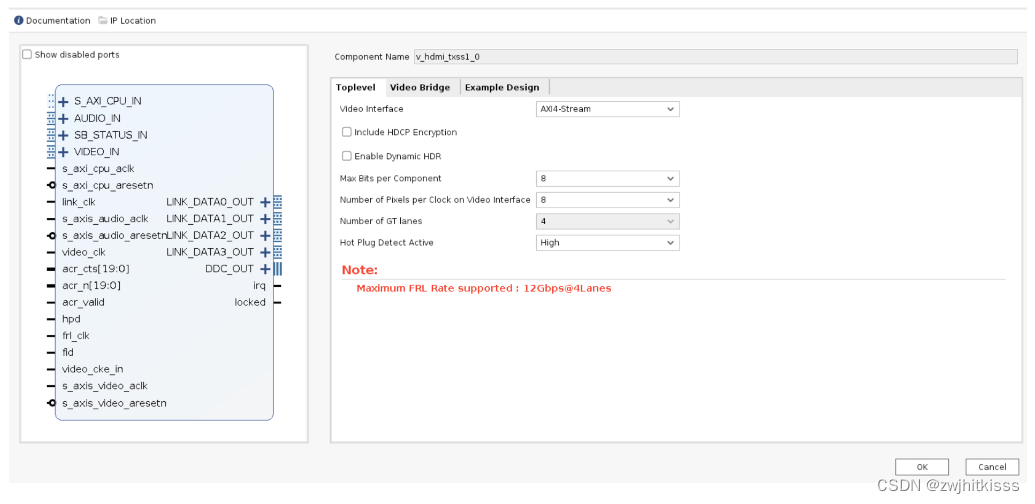

IP核配置页面(图)

采用Native Video or Native Video (Vectored DE)接口时,IP支持YUV420,但是需要自己做YCbCr 4:2:0 Pixel Encoding,参考HDMI 2.0b Section 7。

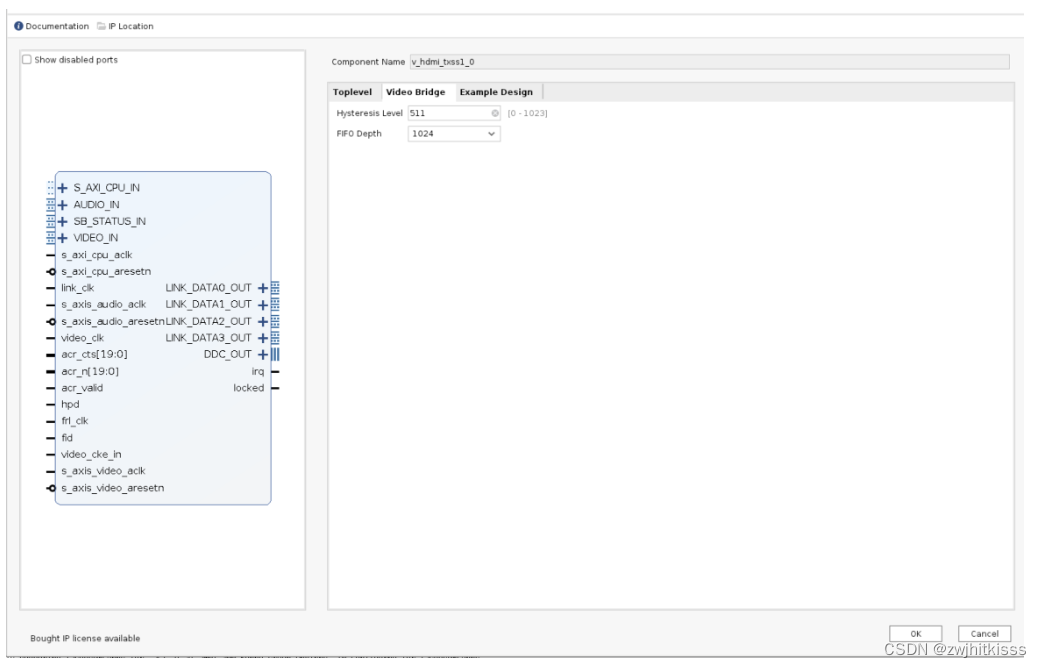

Video Bridge Tab (AXI4-Stream Interface Only)(图)

Hysteresis Level:读FIFO门限

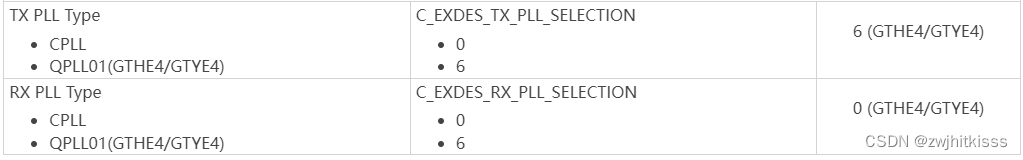

CPLL-0,QPLL-6

CPLL-0,QPLL-6

时钟约束

create_clock -name s_axi_cpu_aclk -period 10.0 [get_ports s_axi_cpu_aclk]

create_clock -name s_axis_audio_aclk -period 10.0 [get_ports s_axis_audio_aclk]

create_clock -name video_clk -period 2.5 [get_ports video_clk]

create_clock -name s_axis_video_aclk -period 2.5 [get_ports s_axis_video_aclk]

create_clock -name link_clk -period 3.333 [get_ports link_clk]

create_clock -name frl_clk -period 2.222 [get_ports frl_clk]

create_clock -name m_hdr_axi_clk-period 3.333 [get_ports m_hdr_axi_clk]

设备、封装、速度等级

HDMI 2.1 FRL Line Rates Supported Across Devices(图)

10、Application Software Development

略

XILINX SUPPORT

性能和资源占用

AR72277

VIVADO IP CHANGE LOG

Xilinx Support web page

Xilinx Core License Agreement

Xilinx HDMI web page

Xilinx Intellectual Property

HDCP Adopters Licensee list

XILINX论坛

Programming and Debugging (UG908)

参考来源

HDMI 2.1 Transmitter Subsystem v1.2(PG350)