前言:通过一个SoC项目实例,了解SoC的架构,初探数字系统设计流程;花最短的时间,走最少的弯路,学最多的IC验证技术知识。

一、SoC架构图:核心功能和设计目标

SoC是基于通用处理器这样的思路进行设计的,与PC设计思路一样。即通用处理器是由 CORE + MEM 两部分组成,修改软件来实现不同的功能,电脑还是同一个电脑,硬件组成还都是一样的。

SoC架构图四大组成部分:

- 1、核 CORE

- 2、存储 MEM

- 3、外设 IO

- 4、总线 BUS

SoC总的架构图如下:

1.1、SoC - 核 CORE

对于核来讲,现在主流的核有三类:

1、CISC(Complex Instruction Set Computer - 复杂指令集计算机)

- x86为代表,公司有AMD和INTEL,PC和Server用这类核比较多。

2、RISC(Reduced Instruction Set Computing - 精简指令集计算机)

- ARM为代表,手机芯片、嵌入式系统等用这类核比较多。

- ARM-M系列:低端,常用在微控制场景,如MCU

- ARM-R系列:中端,常用在实时场景,如医疗器械,路由交换机

- ARM-A系列:高端,常用在高端应用场景,如手机芯片

3、RISC-V(开源)

- 基于ARM和x86之间,可以进行灵活的切换和组装

- 暂没有成熟的商用体系,没有生态支撑

架构图为SoC系统的核,此处使用的是ARM 公司的Cortex-M3/M4内核。

同时,I-Code表示指令代码,D-Code表示数据代码。JTAG用来调试芯片,下载调试程序使用。

注:

I-Code、D-Code即I-Cache、D-Cache,这个可选的,并不是每个SoC都会用到,需要根据实际芯片的规模和需求!

1.2、SoC - 存储 MEM

架构图,中间部分为SoC系统的存储,此处包含PFlash和SRAM两种。

PFlash(硬盘)中的数据掉电不丢失

- 如果PFlash不够用,可以外扩Flash,如

NFC(Nand Flash Controller)

SRAM(内存)中的数据掉电丢

- SRAM是静态随机存储器(Static Random Acess Memory),与之相对的还有一种是动态随机存储器(Dynamic Random Acess Memory)。DRAM需要不断的刷新才能保持住数据,SRAM是不需要刷新的!

- DRAM的密度很高,所以当存储数据容量很大的时候组出来的Memory面积就会小一些!SRAM通常用在小的SoC中!

- 如果SRAM不够用,可以外扩SRAM,比如上图中的

Ext_SRAM

core上电后,会到PFlash中取它的指令,来读取系统要运行的“软件”(代码),在PFlash启动之后,把所需的软件下载至SRAM中,最终在SRAM里运行“软件”。

- 即BootLoader放在PFlash中,一上电便会将其load至SRAM中,CPU来SRAM取指来执行我们的程序!

- SRAM存储速率较PFlash速率快,故上电跑的程序是放在SRAM中,启动程序以及不需要的数据会存在PFlash中。

1.3、SoC - 外设 IO

外设 IO分为两部分:

- 一个是高速外设 IO(AHB 100MHz):DMA、Ext_SRAM Controller、SD_Memory、SD_Host

- 一个是低速外设 IO(APB 50MHz):SPI、UART、GPIO、I2C

1.3.1、 DMA (帮CPU搬移数据)

DMA(Direct Memory Access,直接存储器访问),使用场景如下:当CPU需要搬移SRAM中的大量数据时,此时如果使用CPU搬移,则会先将SRAM中的数据搬移至CPU的寄存器中,然后再取指令写操作等方式搬移至目的地。该方法效率较低,且占用了CPU的宝贵处理时间。此时就有了DMA的登场,CPU只需告诉DMA引擎,你需要从哪个地址搬移多少个数据到哪个地址,这样DMA就自己听话地去工作了,不再需要CPU的参与,减轻CPU的负荷。

DMA对外没有接口,这个也可以从架构图中看出。

1.3.2、 Ext_SRAM Controller、SD_Memory 与 SD_Host

Ext_SRAM Controller:通常是SRAM大小不够时,用作扩展使用。

通常SD_Memory连接一个诸如Camera的设备,将拍到的照片数据通过SD_Memory接口存储到SRAM中,然后SD_Host接口将SRAM中的数据保存至SD Card中,取出SD卡插入PC,就可以看到读取的照片了!

1.3.3、典型低速外设

典型的3个低速外设接口:I2C、UART、SPI,差异如下:

- UART常用于长距离传输,但是速率较低。

- I2C比UART速率快,但是速率不会太长;且I2C在短距离传输时,可以接多个Slave。UART是点点通信,1个UART接口只能接1个UART Slave。1个I2C Master接口,可以接多个I2C Slave;

- SPI相较于UART和I2C速度会更高;1个SPI Master接口,可以接多个SPI Slave;SPI 占用的IO数也较I2C多!

外设与CPU进行通信,有两种方式:

- CPU来查询我们的状态

- 直接给CPU发送中断,CPU收到中断后会去处理中断程序

BootLoader程序和中断程序是事先写好的程序,放到Flash中,一旦启动后便会将其load至SRAM中! 一旦发生某个中断,便会根据中断向量号去查询中断程序去执行它。(了解即可)

注:主动发起数据我们称之为master;被动接受数据我们称之为slave。

1.3.4、内部组件

WDT:看门狗。我们的内核每隔一段时间喂一次狗,如果内核挂掉,看门狗溢出会产生一个中断,告诉外界,芯片已经挂死,需要处理。

Timerx:硬件计数器。CPU计数精读低,通常是us级,很难达到ns级。而我们的硬件计数器精度可以达到ns级别;另外,硬件计数,可以减小CPU的开销。

ICT:指令的计数,统计用的!

1.3.5、剩余组件

左下角是系统控制器和一些模拟组件:

- System Controller:系统控制器

- POR:Power On Reset,上电复位(模拟IP)

- OSC:Oscillator,晶振

- PLL:Phase Locked Loop,锁相环

- VBG:电源管理

- VR:Voltage Regulater,电压调节器

上述讲的IO小模块,以及本节介绍的模拟组件,我们一般都称之为IP。

1.4、SoC - 总线 BUS

将上述介绍的IP进行互联的线,我们将其称之为总线。这里使用的是AMBA 2.0总线,包括AHB、APB两部分。

1.5、其他模块

1.5.1、MemBist

MemBist主要针对Memory,如SRAM。在制造过程中,可能会存在缺陷,当芯片回来之后,我们要进行一些制造型测试!MemBist是进行内建自测试!

这种内建自测试与其他IP外设测试不一样,其他IP外设测试通常是通过GPIO灌激励,然后将经过这些逻辑之后的激励通过另外一些GPIO引出,然后去对比Partner。而内建自测试是我这个测试,对SRAM的测试不需要通过外部的管脚,在SRAM外部会包一层Bist逻辑,然后相当于在内部触发一个使能信号,然后它就可以往SRAM中灌各种激励,然后把经过逻辑之后的激励输出,就可以完成这样一个内建自测试。这就是MemBist的功能。

1.5.2、Spare Cells

Spare Cells 主要是放在顶层,用于芯片后期,在投片时忽然发现有BUG,这时候要做一个叫ECO(Engineering Change Order,手动修改集成电路的过程)的东西,这个时候就可能会涉及到一些cell的替换,如果之前已经放了Spare Cells的话,就可以直接用Spare Cells,不需要再重新增加cell。如果增加cells,可能会导致整个Die的面积放不下!所以相当于是提前预留放了一些为我们做ECO准备的Spare Cells,把面积在那占着,这样的话,整个FloorPlan就不用了动了!Cell在那放着,尽可能最小的去影响我们最终的FloorPlan。

1.5.3、IO MUX

管脚复用,类比STM32。

1.6、SoC IP

二、SoC架构图:简述SoC的功能及应用场景

该芯片是一个SoC芯片,主要功能是无线通信和数据存储功能,主要的应用场景是数据相机的存储卡。随着智能手机的发展,尤其是高清摄像头的发展,这种无线存储芯片方案的应用场景在萎缩。

- 无线通信功能是通过APB总线上的SPI接口外接一个WIFI芯片,实现无线通信和数据传输功能。

- 数据存储功能主要是NandFlash控制器,实现存储功能。但是该芯片采用了替换方案,使用了SD-Host接口,外接SD Card的方式进行存储数据。

- 典型的应用场景是:数码相机拍照时,将照片通过SD-Memory控制器接口,放入SRAM暂存,最后通过SD Host接口,将照片存储到外接的SD memory卡中,然后手机/PC端用户,可以连接到WiFi上,通过手机/PC下载SD Card中存放的视频到手机/PC。

这种应用在记者、摄影爱好者,数码相机爱好者等有应用需求。当把数码相机中的图片下载到手机上后,可以通过移动网络,上传至社交媒体;现场记者,则可以通过将照片及时发送给电视台、媒体等提供及时的照片素材。

2.1、数据存储 数据流

数据存储功能的数据流向示意图(以DMA搬移SRAM数据为例):数据流按照箭头,依次是:红 -> 绿 -> 蓝。(下图标号所在位置是该颜色起始位置)

问:为什么不直接从Camera -> SD Card?如下图:

答:数据通路是可以通的,但是Camera发送数据的速率与SD Card存储数据的速率,这两个并不一定是完全一样的,这样就可能导致数据错误。将数据存入SRAM,相当于起一个缓冲的作用!这样我数据存进来之后,是存至SD Card还是通过WiFi进行无线传输,都可以通过CPU进行灵活控制!

2.2、无线传输 数据流

无线传输功能的数据流向示意图(以DMA搬移SRAM数据为例):数据流按照箭头,依次是:红 -> 蓝 -> 棕。(下图标号所在位置是该颜色起始位置)

2.3、关于Master和Slave

- CPU通常是一个Master,数据的发起者;

- 存储系统(PFlash、SRAM)是一个Slave,被动的接收别人发过来的命令,要来读哪个地址的数据了;

- 两个AHB高速外设:SD_Memeory和SD_Host。既有Master口,又有Slave口。SD_Memory模块工作时,数据是通过Master口进行传输,Slave口更多指的是CPU对其进行一些配置(IP可以工作在多种模式,控制信号可以通过Slave口对其进行配置);SD_Host模块同理。

- 慢速外设:SPI/UART/GPIO/I2C/Timer/WDT/ICT等,都是Slave口,是CPU来告诉他们要传什么数据出去(CPU对其进行配置)。

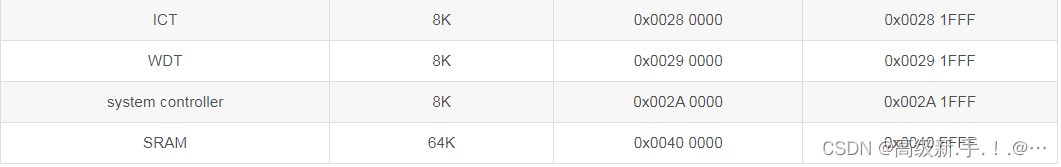

三、SoC架构图:IP总线地址映射

基地址:Base Address

偏移地址:Offset Address

注:

基地址 + 偏移地址可类比区号 + 号码。低16位是偏移地址,高16位是基地址。

每一次的访问都是基于地址空间进行访问的,所以会把每一个系统进行划分,划分成为一个地址空间。

各个外设地址如下表:

软件工程师写模块时,通常只关注偏移地址!

- 一般一个地址空间可以存储8bit数据,故上述单位是

KB

四、SoC架构图:Pin-MUX & PAD

- PAD:芯片与外部通信的一个接口

- PIN-MUX:主要用来减少PAD数目,为什么要减少PAD?

- ①、PAD本身就挺大的,PAD过多,很占边长,造成规划的Die放不下。【芯片外围边长留足够的余量】

- ②、PAD本身是模拟器件,PAD过多,会增加功耗!【总体功耗也会有收益】

- 上图展示的三种数字PAD,从上到下分别是:Input Only、Output Only、Bidirection 三种。工程上通常上都是 Bidirection ,使用的时候直接控制EN信号,来使其输入或输出!

- 模拟PAD:如LVDS;

- VR(电压调节器) PAD

五、SoC架构图:版图布局 Floorplan

注:版图布局 Floorplan 布局可类比 PCB 的布局!

Floorplan 中可以看到的是各个Cell(数字电路)和各个IP(模拟电路)。

- 模拟 IP (MEM/FLASH)放到靠近DIE的边角上,提高空间利用率

- DIE的内部会放数字逻辑

这样的放置原则是为了提高整个空间的利用率!MEM这个模拟IP,可以认为是一个硬核,如果它放中间,那么周围的绕线就会很麻烦。如果是数字的话,那就是各个离散的Cell,走线容易,空间利用率高!

六、SoC架构图:版图 layout - GDSII

注:版图 layout 可类比 PCB 的布线!

下面的版图 layout 中,中间紫色部分的就是对应 Floorplan 中标注的数字逻辑部分,周围靠近Die的就是模拟IP!

- 工艺水平:110nm e-flash

- DIE大小:3mm x 4mm = 12 mm^2

- 晶圆wafer大小:8英寸,可以生成3600片DIE(3mm x 4mm),1个wafer的制造成本在1000美金。

- 良率(yield)【wafer中有多少个DIE是可用的】:>95%(通过ATE去筛选不能用的DIE)

六、SoC架构图:Pin & 电源电压

下图为外围的原理图,从中可以看到管脚分布和电压域划分。

- 电压域的划分工作通常由架构师完成,前端人员是接触不到这个东西的!

- 电压域通常可划分为:数字电压域(CORE、IO)、模拟电压域(不同模拟IP,不同的电压)

七、数字系统设计节点(SoC Design Node)

芯片的诞生,从前期到后期的整个流程:

- ①、进行市场调研,有没有市场需求,具不具备很好的商业价值,做芯片很烧钱,1个wafer1w美金,还要买一些IP等都要花钱!做出来之后能否赚钱,有没有人买单,这个很重要!

- ②、根据市场需求,算法团队根据要实现的功能,做一个算法模型,算法可以实现(仿真成功),可以达到市场需求,则进行下一步。

- ③、进行芯片的实现架构设计,包括:软硬件划分(哪些部分用软件实现,哪些部分用硬件实现)、硬件上划分多少个模块等,编写架构文档(AS,Architecture Specification),架构也分为好多层次,比如系统级,电路级等。接下来还有编写一个设计文档(DS,Design Specification)

- ④、编写RTL代码,进行功能验证(EDA仿真验证、FPGA原型验证)和代码复查

- ⑤、通过综合工具,将其转化为Netlist,即将RTL代码映射(MAP)成门级网表(STD CELL),同时进行形式验证(RTL逻辑功能和Netlist的逻辑功能对比,看看综合工具是否把RTL某些功能给优化掉),时序验证(实现Netlist后,timing setup 能否满足)

- ⑥、接下来进行物理实现,GDSII也是一个网表,只不过是包含了器件位置信息的网表。Netlist仅仅只是逻辑信息。然后进行一些后仿真和签收复查。

- ⑦、投片,在wafer上生成我们的芯片。生产过程有没有问题,通过ATE测试,ATE测试的partner是在前面做RTL时的DFx做的,Membist,Scan扫描,都是在前期做好的设计,芯片回来之后,会把这些电路启动,进行ATE测试!测芯片本身,有没有制造功能的问题!

- ⑧、最后进行应用测试,即功能测试。投放市场。

从上图看出

- ①、芯片的实现是需要很多的团队,很多个环节,一步步实现的。

- ②、每一个环节的交付件(交付标准)是变化的,每一步都是需要有不同的方法验证。做IC验证,主要进行RTL的功能验证,要明确从事的工作在整个设计流程中的位置!

参考文章:soc架构实例