前言

计算机是由若干系统功能部件构成的,这些系统功能部件只有连接在一起协调工作才能形成一个完整的计算机硬件系统。

起到连接和信息传输功能的部件就是总线。各个功能部件只有通过总线进行有效连接后,才能实现彼此间的通信及资源共享。

正文

一、总线的概念

总线是构成计算机系统的互连机构,是多个系统功能部件之间进行数据传送的公共通路。

形象说,就好比两个景区之间的高速公路。

1、总线的特点:

共享性

总线是供所有部件通信共享的,任何两个部件之间的数据传输都是通过共享的公共总线进行的。

独占性

当一个部件占用总线与另一个部件进行数据通信时,其他部件就不能再占用总线。

2、总线的分类(按总线上传输信号的不同来分):

地址总线

传送的是从CPU等主设备发往从设备的地址信号。

控制总线

传送的是一个部件对另一个部件的控制或状态信息,如CPU对存储器的读、写控制信号等。

数据总线

传送的是各部件之间交换的数据信息,数据总线通常是双向的。

以CPU读存储器为例简要说明三类总线的作用,CPU首先通过地址总线发出想要访问的存储单元的地址(即通过地址总线找到访问对象),然后通过控制总线发出读信号(即通过控制总线决定数据传输方向),最后经过数据总线把数据从存储器读到CPU(即通过数据总线完成真正的数据传输)。

3、总线的特性:

物理特性

指的是总线的物理连接方式,包括:总线的根数,总线的插头、插座的形状,引脚线的排列方式等。

功能特性

指的是总线中每根传输线的功能,例如:地址总线用来传输地址码,数据总线他、用来传送数据等。

电气特性

指的是每根线上信号的传递方向及有效电平范围,一般规定送入CPU的信号叫输入信号(IN),从CPU发出的信号叫输出信号(OUT),定义高电平为1,低电平为0。

时间特性

指的是每根线在什么时间有效,也就是说,只有规定了总线上各信号有效的时序关系,整个计算机系统的各个功能部件才能有条不紊的协调工作。

4、总线的工作原理:

如果说主板是一座城市,那么总线就像是城市里的公共汽车,能按照固定行车路线,传输来回不停运作的比特。一条线路在同一时间内都仅能负责传输一个比特。

因此,必须同时采用多条线路才能传送更多数据,而总线可同时传输的数据数就称为宽度,以比特为单位,总线宽度愈大,传输性能就愈佳。

总线的带宽(即单位时间内可以传输的总数据数)为:总线带宽 = 频率 x 宽度/8(Bytes/sec) 。当总线空闲(其他器件都以高阻态形式连接在总线上)且一个器件要与目的器件通信时,发起通信的器件驱动总线,发出地址和数据。其他以高阻态形式连接在总线上的器件如果收到(或能够收到)与自己相符的地址信息后,即接收总线上的数据。发送器件完成通信,将总线让出(输出变为高阻态)。

二、总线的连接方式

由于外设设备较多,且种类繁杂、速度各异,不能简单地把它们连到CPU上,因此必须寻找一种将外围设备同CPU连接起来的方法。这项工作一般都是由适配器部件来完成的,适配器通常也称为I/O接口。

根据连接方式不同,单处理机系统中采用的总线结构有两种:单总线结构和多总线结构。

1. 单总线结构:

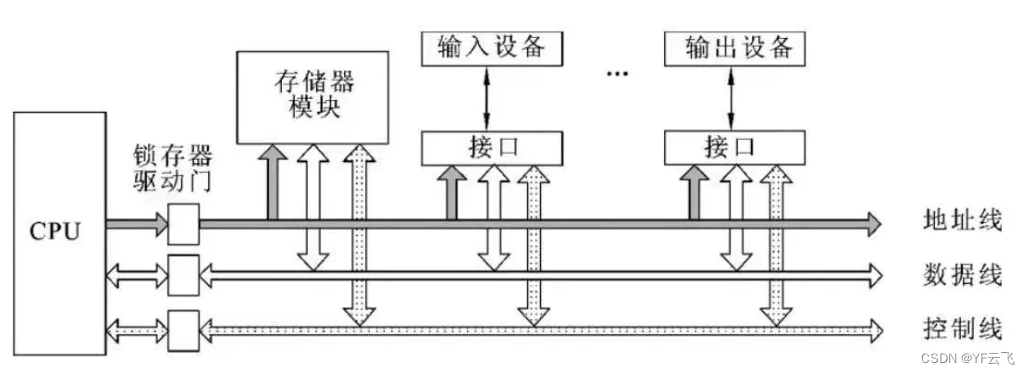

在许多单处理器的计算机中,使用单一的系统总线来连接CPU、主存和I/O设备,叫做单总线结构,允许I/O设备之间、I/O设备与CPU之间、I/O设备与主存之间直接交换信息。如下图所示:

这种结构简单,便于扩充,但缺点是所有的传送都通过这组共享的总线,因此极易形成计算机系统的瓶颈。

这类总线多数被小型计算机或微型计算机所使用。

2. 多总线结构:

多总线结构是CPU和cache之间采用高速的CPU总线。通过桥(具有缓冲、转换、控制功能的逻辑电路),CPU总线、系统总线和高速总线彼此相连。如下图所示:

多总线结构实现了高速、中速、低速设备同时连接到不同的总线上进行工作,极大地提高了总线的效率和吞吐量。

三、总线的内部结构

1. 早期:

早期的总线内部结构是处理器芯片引脚的延伸,是处理器与I/O设备适配器的通道,这种简单的总线一般也由50 —100条线组成。如下图所示:

这种总线结构的不足之处在于:

CPU总是唯一的主控者;

总线信号是CPU引脚信号的延伸,故总线结构与CPU紧密相关,通用性较差。

2. 当代:

当代流行的总线内部结构是一些标准总线,追求的是与硬件结构、CPU、技术无关的开发标准,并满足包括多个CPU在内的主控者环境的需求。如下图所示:

由上图可以看出,CPU和片内cache一起作为一个模块与总线相连。同时,在系统中允许有多个这样的处理器模块。而总线控制器完成几个总线请求者之间的协调与仲裁。

整个总线分成以下四个部分:

数据传送总线

由地址总线、数据总线、控制总线组成。为了减少布线,数据总线常常和地址总线采用多路复用的方式。

仲裁总线

包括总线请求线和总线授权线。

中断和同步总线

用于处理带优先级的中断操作,包括中断请求线和中断认可线。

公用线

包括时钟信号线、电源线、地线、系统复位线及加电或断电的时序信号线等。

大多数计算机采用了分层次的多总线结构。在这种结构中,速度差异较大的设备模块使用不用速度的总线,而速度相近的设备模块使用同一类总线。

四、总线的技术指标

总线的带宽指的是单位时间内总线上传送的数据量,即每秒钟传送MB的最大稳态数据传输率 [2] 。与总线密切相关的两个因素是总线的位宽和总线的工作频率,它们之间的关系:

总线的带宽=总线的工作频率*总线的位宽/8

或者 总线的带宽=(总线的位宽/8 )/总线周期

2、总线的位宽

总线的位宽指的是总线能同时传送的二进制数据的位数,或数据总线的位数,即32位、64位等总线宽度的概念。总线的位宽越宽,每秒钟数据传输率越大,总线的带宽越宽。

3、总线的工作频率

总线的工作时钟频率以MHZ为单位,工作频率越高,总线工作速度越快,总线带宽越宽。

五、总线的发展史

ISA总线

(Industry Standard Architecture)

⬇

PCI总线

(Peripheral Component Interconnect)

⬇

AGP 总线

(Accelerated Graphics Port)

⬇

PCI-Express

六、总线的专业术语

1. |

intermediate distribution bus 中间分布总线 |

2. |

VESA local bus (VL-bus) VESA 局域总线 |

3. |

analysis, bus bounce 总线跳动分析 |

4. |

analog summing bus 模拟加法总线 |

5. |

architecture, micro-channel bus (MCA) 微通道总线(体系)结构 |

6. |

arbitration bus 判优总线 |

7. |

arbiter, bus 总线判优器 |

8. |

backplane bus 基架总线 |

9. |

back-off, bus 总线退出 |

10. |

base bus 基底总线 |

11. |

bus-timing emulation 总线时序仿真 |

12. |

bus-intensive 总线密集 |

13. |

bus-control unit 总线控制单元 |

14. |

bus, utility 公用程序总线 |

15. |

bus, summing 加法总线 |

16. |

bus, realtime system integration (RTSIBus) 即时系统综合总线 |

17. |

bus, peripheral interface 外设接口总线 |

18. |

bus, multisystem extension interface (MXIbus) 多系统延伸接口总线 |

19. |

bus, multidrop parallel 分支平行总线 |

20. |

bus, micro-channel 微通道总线 |