时钟组与其他时钟特性

一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人可能会提到对于特定算法和协议的理解,有些人或许会提到对于软硬件的结合划分,作者想说,这些说法,其实对也不对,硬件描述语言,翻来覆去无非是always和assign这几个语句的反复使用,而一些基础的协议算法,深究起来其实也并不复杂,于作者而言,在常规的技能以外,有两项额外的技能颇为重要,其中之一便为sdc/STA的分析能力,它的重要之处在于作为桥梁建立了前端和后端的连接,虽然对于DE工程师而言,初版交付的sdc往往不甚准确,也没有办法通过这份sdc生成一份无误的timing report,但sdc的内容体现却是完完整整的将时序约束从行为级的描述映射到了gate level这样一个真实的电路层次上面。

写此专栏,一为学习记录,二为交流分享,以犒粉丝读者。

1.1 快速导航链接·

静态时序分析简明教程(一)绪论

静态时序分析简明教程(二)基础知识:建立保持时间,违例修复,时序分析路径

静态时序分析简明教程(三)备战秋招,如何看懂一个陌生的timing report

静态时序分析简明教程(四)时钟常约束

静态时序分析简明教程(五)生成时钟

静态时序分析简明教程(六)时钟组与其他时钟特性

静态时序分析简明教程(七)端口延迟

静态时序分析简明教程(七)完整端口约束

静态时序分析简明教程(八)虚假路径

静态时序分析简明教程(九)多周期路径

静态时序分析简明教程(十)组合电路路径

静态时序分析简明教程(十一)模式分析与约束管理

静态时序分析简明教程(十二)浅议tcl语言

二、时钟组

2.1 引入时钟组

对于同步电路而言,正确的建立时间和保持时间的检测,就可以确保捕获可靠的数据,但是对于异步时钟而言,我们没有办法确定几个时钟之间的相位关系,因此没有办法使用常规的STA分析方法,对于这样的时序路径,我们需要让时序工具加以忽略,时钟组的引入,给予设计人员这样的机会。

2.2 set_clock_group

对于set_clock_group而言,它的BNF(巴斯科范式)表达式如下

set_clock_groups [-name group_name]

[-group clock_list]

[-logically_exclusive]

[-physically_exclusive]

[-asynchronous]

[-allow_paths]

[-comment comment_string]

我们也将进一步的进行解释

2.2.1 -name

提供时钟组唯一的名称,与时钟常规约束类似,详情可见静态时序分析简明教程(四)时钟常归约束中的3.3节内容,通过-name的形式设定名称。

2.2.2 -group clock_list

-group可以将设定好的单个时钟信号分入各组,案例如下

create_clock -period 10 -name C1 [get_ports A]

#创建一个时钟C1

create_clock -period 13 -name C2 [get_ports B]

#创建一个时钟C2

set_clock_groups -name CLK_GRP -group C1 -group C2

#通过-group的形式把他们放到一个时钟组,时钟组命名为CLK_GRP

2.2.3 -logically_exclusive|-physically_exclusive|-asynchronous

接下来的这三个命令要放到一块进行讨论,原因是这三个命令是互斥的,在命名时钟组的时候只能挑其中一个使用,虽然使用他们的任意一个都代表时钟组内的时序路径不用考虑,但是他们还是有细微的差别如下

| -logically_exclusive | -physically_exclusive | -asynchronous |

|---|---|---|

| 设计中共存多个时钟,并且电路仅选择一个 | 设计中不能共存多个时钟 | 设计中共存多个时钟,却没有相位关系 |

有关于-asynchronous的使用最为频繁,对于异步电路而言,我们频繁的需要使用这个指令来拒绝STA工具分析CDC的路径问题

2.2.4 -allow_path

在工艺进入深亚微米后,由于串扰的影响,建立时间和保持时间的检查也会受串扰的影响而产生变动,当用户希望执行串扰分析时,可以使用-allow_path这个选项,这个选项仅可以和–asynchronous一块,代表执行串扰分析而不禁用时钟之间的时序电路路径。

这种串扰的分析确实也不归设计人员管,所以略过这里即可

2.2.5 -comment

参见静态时序分析简明教程(四)时钟常约束中3.6的内容,使用-comment的尾缀增加时钟注释。

三、其他时钟特性

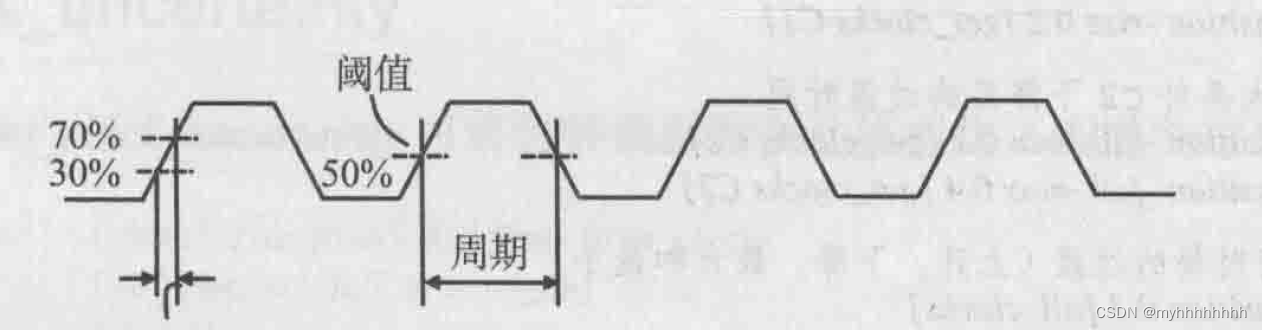

3.1 过渡时间

理想的时钟边沿,从0到1和从1到0,时间为均0,但是实际上的clk,从0到1和从1到0会在一个有限的时间内完成,我们使用过渡时间来描述信号从一个状态转变为另一个状态的时间,当然什么样的摆幅算0,什么样的摆幅算1,其实是由设计人员决定的,我们可以在30%到70%的区间上定义过渡时间。

时钟的过渡时间使用set_clock_transition来描述,该指令的BNF为

set_clock_transition [-rise]

[-fall]

[-max]

[-min]

clock_list

transition_time

需要注意的是,该指令仅用于预布局阶段,在时钟树生成之后,该指令不应再用于时序分析

该指令的案例如下:

#设置C1的上升沿过渡时间

set_clock_transition -rise 0.2 [get_clocks C1]

#设置C2的下降沿最大和最小的过渡时间

set_clock_transition -fall -min 0.2 [get_clocks C2]

set_clock_transition -fall -max 0.4 [get_clocks C2]

#设计所有时间的过渡时间

set_clock_transition 0.3 [all_clocks]

3.2 偏移与抖动

抖动:由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。

偏斜:同样的时钟产生的多个子时钟信号,他们之间存在的延时差异。是时钟相位上的不确定。

抖动和偏斜,都会影响建立时间和保持时间检查的要求,为了应对这种不确定性,我们可以使用set_clock_uncertainty去进行偏移与抖动的约束,它的BNF表达式如下所示

set_clock_uncertainty [-from|rise_from |-fall_from from_clock]

[-to|-rise_to|-fall_to to_clock]

[-setup]

[-hold]

[-rise]

[-fall]

[object_list]

Uncertainty_value

我们可以通过上面的语句,分别设置上升沿/下降沿的不确定度,亦或是设置建立时间/保持时间的不确定度,同样可以设置某两个点之间的不确定度,比如

# 从C1到C2的建立时间和保持时间的不确定度

set_clock_uncertainty -from C1 -to C2 -setup 0.5

set_clock_uncertainty -from C1 -to C2 -hold 0.5

而通常情况下,作为SDC交付的第一版,在同步电路中,DE人员也可以简略的将不确定度设置为

set_clock_uncertainty 0.5 [get_clocks CLK]

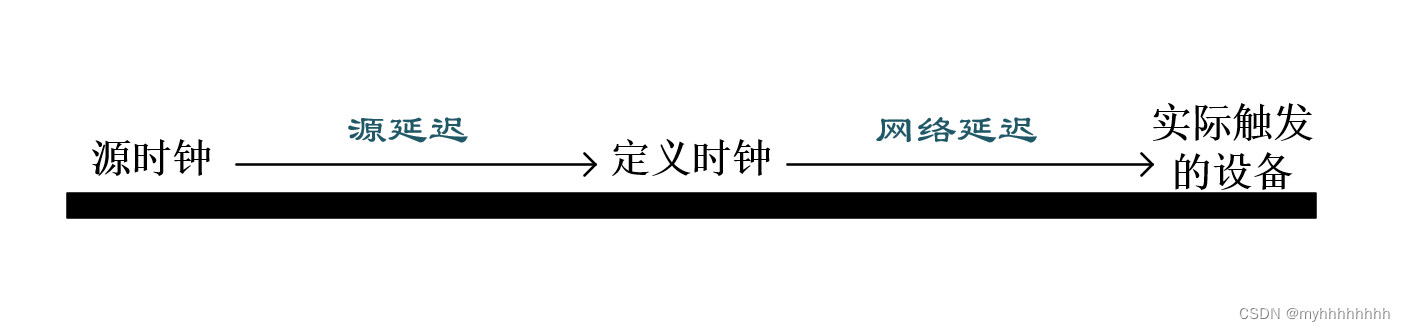

3.3 时钟延迟

时钟延迟主要是指,源时钟(通常为PLL)和时钟触发的设备之间的延迟,它有两个来源,分别是源延迟和网络延迟,一个形象的图片描述如下

我们可以通过set_clock_latency来建模网络延迟,不需要建模源延迟的原因是它的延迟与时钟树相关,要在布局布线后才能得到,该指令的BNF为

set_clock_latency [-rise]

[-fall]

[-min]

[-max]

[-source]

[-late]

[-early]

[-clock clock_list]

delay

object_list

通过-rise/fall来指定上升沿和下降沿的延迟,通过-min和-max指定最小延迟和最大延迟,通过-source指定设置延迟的源组件,通过-late/-early来设置最长路径延迟和最短路径延迟

四、总结

在第二章中,我们讨论了一个复杂的电路设计不可能只存在一个时钟域,面对不可避免地多时钟域问题,我们采用时钟组的方式来描述不同时钟之间的关系。

而在第三章中,我们使用SDC命令去约束和描述那些非理想的时钟特性,如过渡时间、偏移、抖动、延迟等。

虽然说在布局布线完成后,他们的数值或者形态会发生改变,但这些约束依旧值得学习,因为他们在整个芯片设计的前面阶段为我们提供了重要的参考。