- 时钟的时序特性主要分为:时钟周期(clock period)、始终占空比(clock duty cycle)、时钟转换时间(clock transition time)、时钟延迟(clock latency)、时钟偏斜(clock skew)、时钟抖动(clock jetter)

- 时钟转换时间之前的文章有介绍

- 时钟延迟-时钟信号从时钟源端口到达时序单元时钟输入端口所需的传播时间

- 时钟偏斜:非理想情况下,由于时钟线长度以及时钟树叶节点负载不同等因素,导致时钟信号到达同意时序路径下的相邻两个时序单元的时钟端口的时间并不相同,这种时钟信号之间的偏移就是相同时钟信号之间的时钟偏斜。

5.时钟抖动:

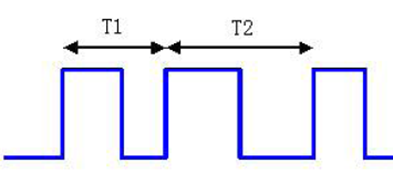

所谓抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响

jitter=T2-T1