| 芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球 |

|---|

| 四社区联合力荐!近500篇数字IC精品文章收录! |

| 【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 |

case的综合结果,你究竟会了吗?

一、写在前面

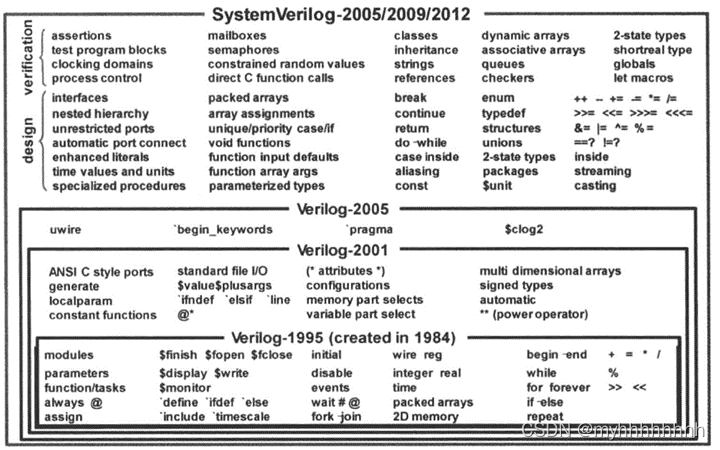

本专栏为作者在 【数字IC手撕代码】 【数字IC笔试面经分享】 【数字IC工具解析】 以外开设的第四个独立专栏,旨在学习并提供有关Verilog硬件描述语言中非基础性的高阶语法特性知识,因本身专栏的独特定位,因此作者并不会涉及基础Verilog语言如阻塞式非阻塞赋值,过程块,数据类型等内容;同时受限于作者知识有限,本专栏也不会涉及System Verilog的相关内容,若按照IEEE的相关标准来看,本专栏将会聚焦Verilog-2005,即“IEEE Std 1364™-2005”以及之前的有关内容,提供相关的IC设计领域语法特性。以下为Verilog的进阶框图,有更多学习需求的读者可以检索相关英文标准进行学习。

二、case的综合结果

在【数字IC手撕代码】Verilog固定优先级仲裁器|题目|原理|设计|仿真中,我们浅议了有关case语句的串行综合结果和parallel综合结果,这个问题容易被忽视,但却很重要,因为一个串行结构和一个并行结构的STA分析时序路径不一样长,假如ASIC设计工程师错将一个顺序的case当成了并行的case,可能会造成整体电路频率的降低,并引发更为严重的后果,如前后仿不一致,除此以外,case语句的错误使用,还有可能造成锁存器或无法综合的情况出现,在本文中我们会具体讲解和体现。

2.1 case综合出锁存器

以下的case语句会综合出latch,原因是case的可能条件不全,以下面的代码为例,默认sel为2‘b11的时候,y的值保持,即综合过程中出现了latch。

always@(a or b or c or sel)

case(sel)

2'b00 : y = a;

2'b01 : y = b;

2'b10 : y = c;

endcase

2.1.1 解决方式一

针对这种情况,我们有两种解决方法,一为写全sel的可能情况,即补充sel = 2’b11的可能性

always@(a or b or c or sel)

case(sel)

2'b00 : y = a;

2'b01 : y = b;

2'b10 : y = c;、

2’b11 : y = d;

endcase

2.1.2 解决方式二

二为熟悉而常见的增加default语句,如下所示,我们也可以避免出现latch,因为2’b11的情况包含在了default里面了。

always@(a or b or c or sel)

case(sel)

2'b00 : y = a;

2'b01 : y = b;

2'b10 : y = c;

default: y = d;

endcase

2.2 case综合出并行结构

我们通常情况下讨论的case语句都是并行结构,比如代码如下

always@(a or b or c or sel)

case(sel)

2'b00 : outc = a;

2'b01 : outc = b;

2'b10 : outc = c;

2’b11 : outc = d;

endcase

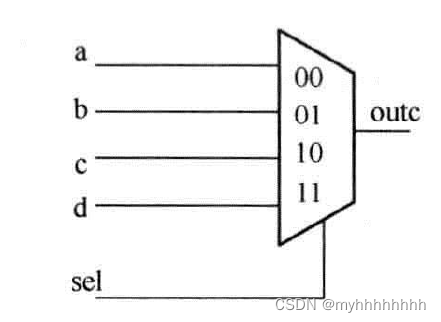

这段代码的综合结果为4选1的mux,如下图所示,即为并行结构,但并非所有的case语句都会被综合成并行的结构。

2.3 case综合出串行结构

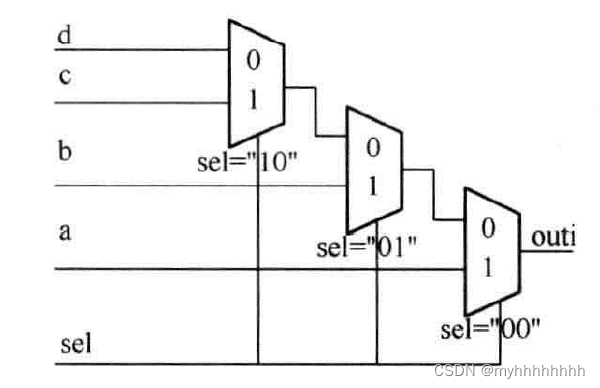

如以下代码,case语句的综合结果会出现与if嵌套相似的串行结构

那么我们如何去判断case语句综合是串行的还是并行的呢?假如下面代码中request这个值为4’b1111的话,若为并行结构,则从第三行到第六行的语句都会被执行,即产生了冲突,因此它应该是一个串行的结构,换言之,通过遍历条件在case中是否只会被执行一次,我们可以判断case的综合结果为串行还是并行。

always@(*)

case(1'b1)

request[3] : grant_reg = 4'b1000;

request[2] : grant_reg = 4'b0100;

request[1] : grant_reg = 4'b0010;

request[0] : grant_reg = 4'b0001;

default: grant_reg = 4'b0000;

图片虽然与代码不符,但是串行结构的结构是相似的,该电路结构的判断是有先后顺序的,这种写法的case和if语句实现的功能相同,也可以相互改写。

2.4 不可综合的case语句

x和z的case比较有可能会出现不可综合的情况,对于casex而言,前仿会把x值的输入当作不关心,而后仿会在条件检查时把x在门级模型中传播,冲突出现。

casez也会出现相似的问题,虽说casez可以写出更加简洁的表达式,如优先级编码器和地址译码器等,但与casex相似的,casez也会出现错误匹配的问题。

相关的语句casez和casex虽然在前仿中可以进行对应的比较,但有关x或z态的代码却是不可以综合的,在使用中需要多加注意。

三、更多资料

更多的内容可以参考“CummingsSNUG1999Boston_FullParallelCase”这是一篇来自1999年的英文论文,共有20页,但里面的内容放在今天也不过时,google相关文章即可阅读。

四、往期【Verilog】高级教程文章

- 多维数组:灭霸打个响指的功夫,看懂Verilog多维数组

- clog2系统函数: 关于Verilog自动计算位宽的系统函数$clog2,这些是你不得不知道的

- UDP用户原语:玩转UDP用户原语,这篇文章就够了

- $monitor系统函数:放学前的最后几分钟,看懂Verilog中的monitor系统函数

- generate语句:一把王者的时间,学会Verilog中的generate语句

- parameter常量:玩转parameter与localparameter,这篇文章就够了

- inout双向端口:通俗易懂的带你解读inout双向端口

- task与function区别:芯片人必会的task与function区别详解