文章目录

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/08/03 14:51:58

// Design Name:

// Module Name: tb_fifo_ctrl

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_fifo_ctrl();

reg rst_n;

reg wr_clk;

reg rd_clk;

reg [15:0] din;

reg wr_en;

reg rd_en;

wire [15:0] dout;

wire full;

wire empty;

wire [4:0] rd_data_count;

wire [4:0] wr_data_count;

initial begin

rst_n = 1'b1;

wr_clk = 1'b0;

rd_clk = 1'b0;

din = 16'd5;

wr_en = 1'b0;

rd_en = 1'b0;

#121;

rst_n = 1'b0;

#20;

@(posedge wr_clk)

wr_en = 1'b1;

@(posedge wr_clk)

wr_en = 1'b0;

#1000;

@(posedge rd_clk)

rd_en = 1'b1;

@(posedge rd_clk)

rd_en = 1'b0;

end

always #10 wr_clk <= ~wr_clk;

always #5 rd_clk <= ~rd_clk;

fifo_ctrl fifo_ctrl_inst(

.rst_n (rst_n),

.wr_clk (wr_clk),

.rd_clk (rd_clk),

.din (din),

.wr_en (wr_en),

.rd_en (rd_en),

.dout (dout),

.full (full),

.empty (empty),

.rd_data_count (rd_data_count),

.wr_data_count (wr_data_count)

);

endmodule

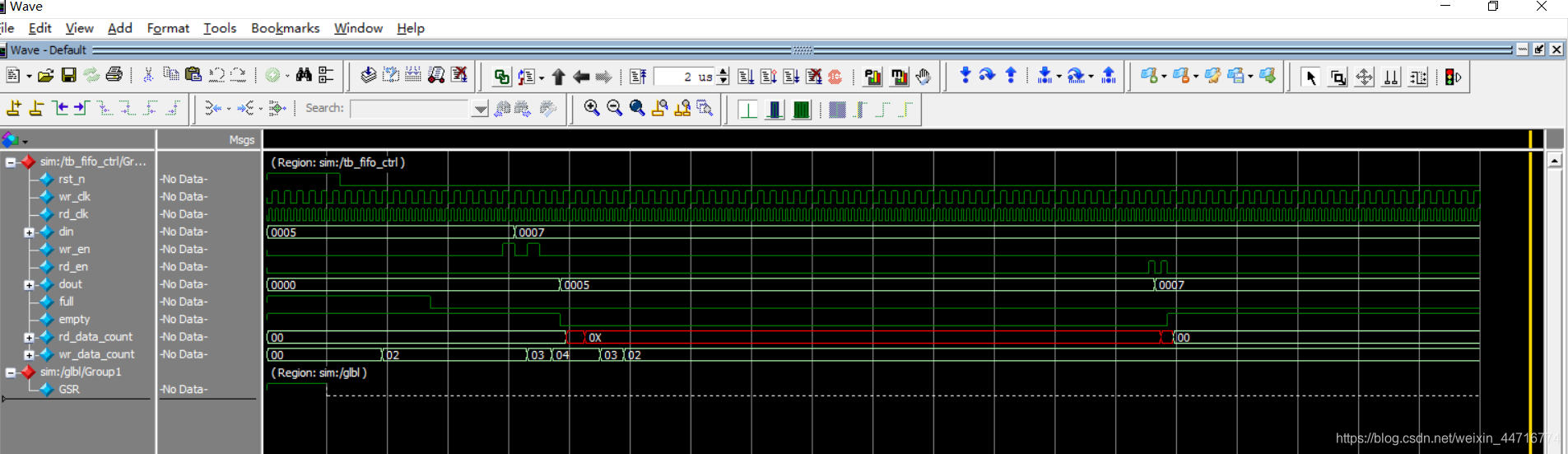

由此可见,full并不是一开始就拉低的,empty也不是一写入数据就拉低的,data计数器是不怎么准确的,但是当读空了会立即拉高(记得即使fwft模式下,数据会提前出来,所以rd_en也要给够。