门电路、组合电路、时序电路的Verilog编程实例

目录

HDLBits — Verilog Practice 在线练习Verilog编程网站;

在线Verilog编程网站学习。从门电路、组合电路、时序电路中各选3个以上的例题实践完成。

一、门电路

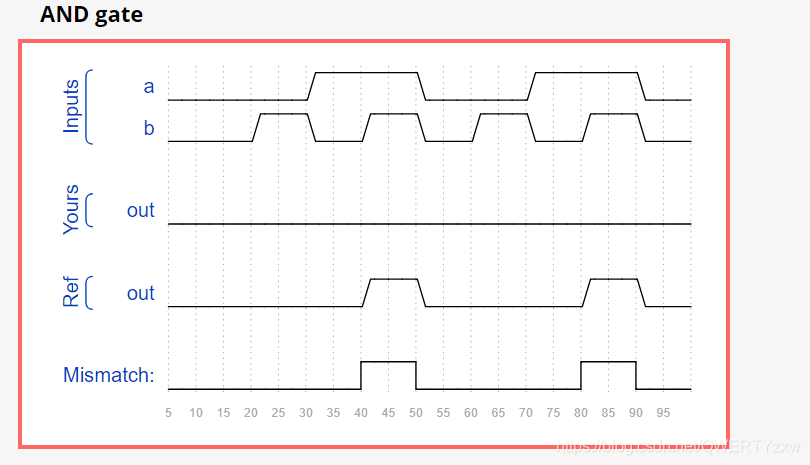

1、和门

模块声明:

module top_module(

input a,

input b,

output out );

endmodule

仿真结果:

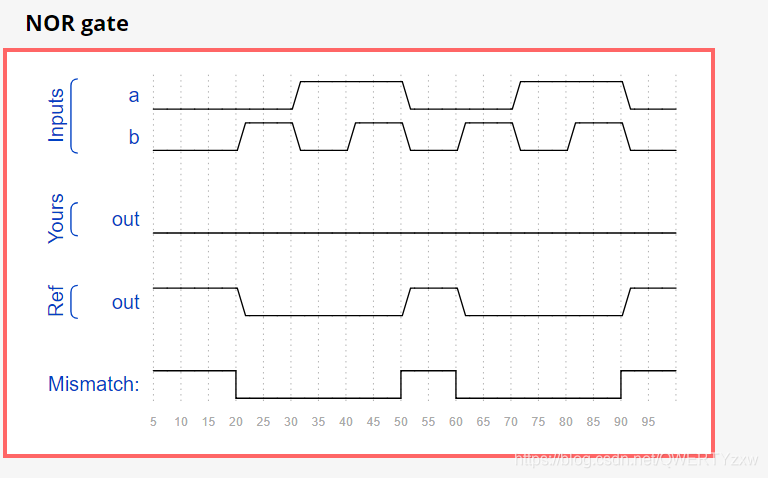

2、无门

模块声明:

module top_module(

input a,

input b,

output out );

endmodule

仿真结果:

3、XNOR门

模块声明:

module top_module(

input a,

input b,

output out );

endmodule

仿真结果:

二、组合电路

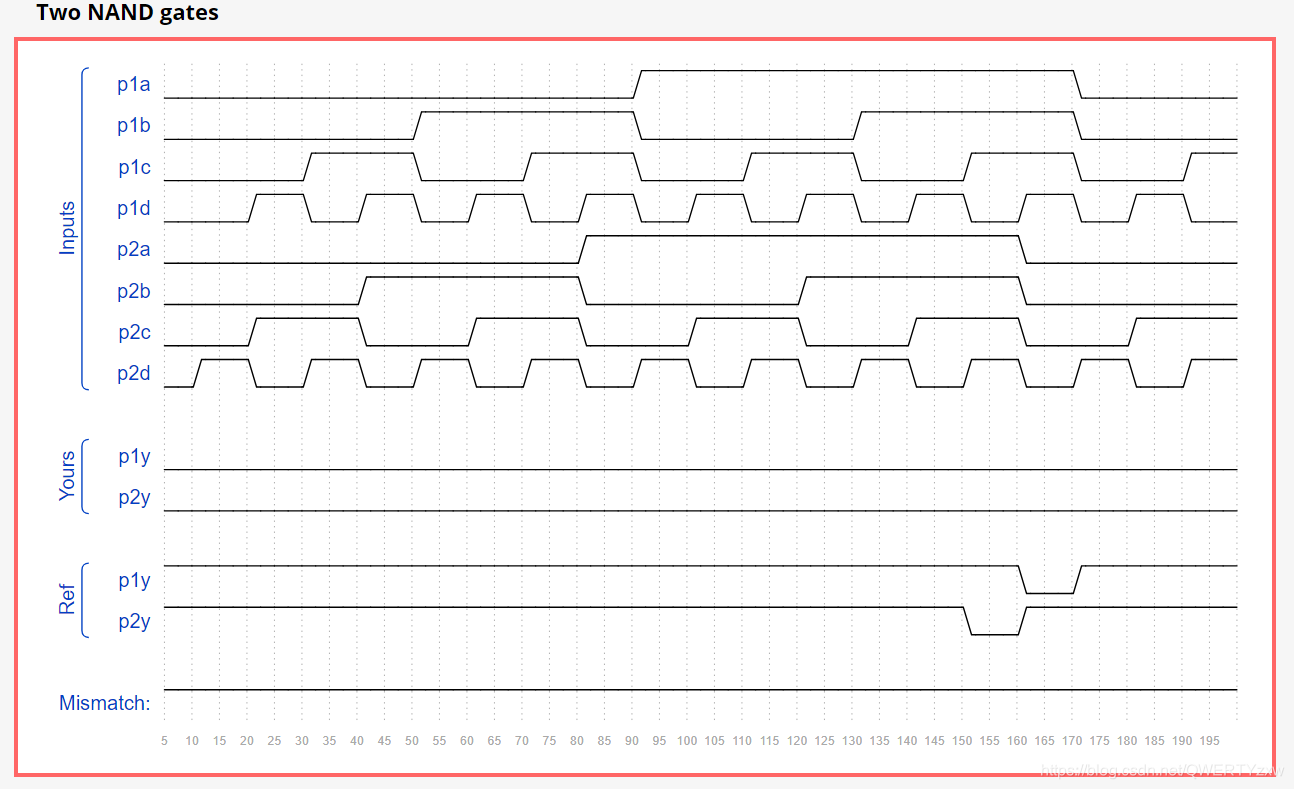

1、7420芯片

模块声明:

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

endmodule

仿真结果:

扫描二维码关注公众号,回复:

13521521 查看本文章

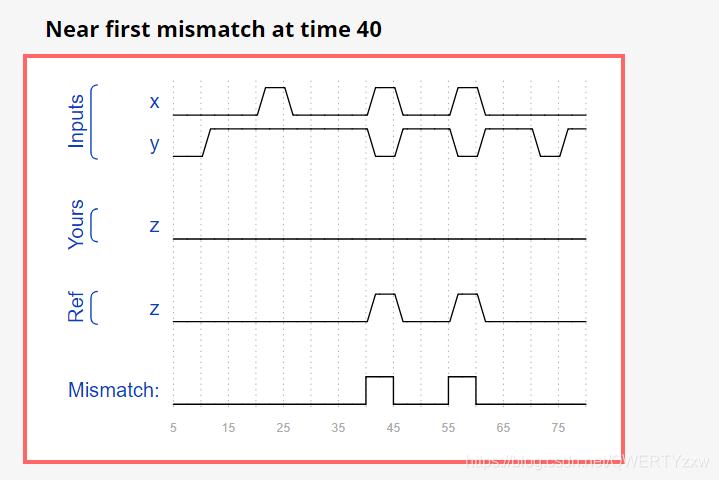

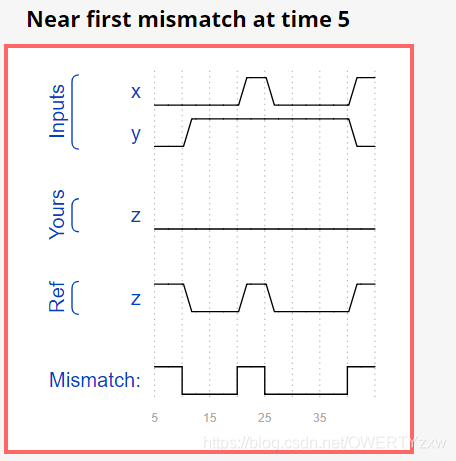

2、简单电路

模块声明:

module top_module (input x, input y, output z);

endmodule

仿真结果:

3、组合电路

模块声明:

module top_module (input x, input y, output z);

endmodule

仿真结果:

三、时序电路

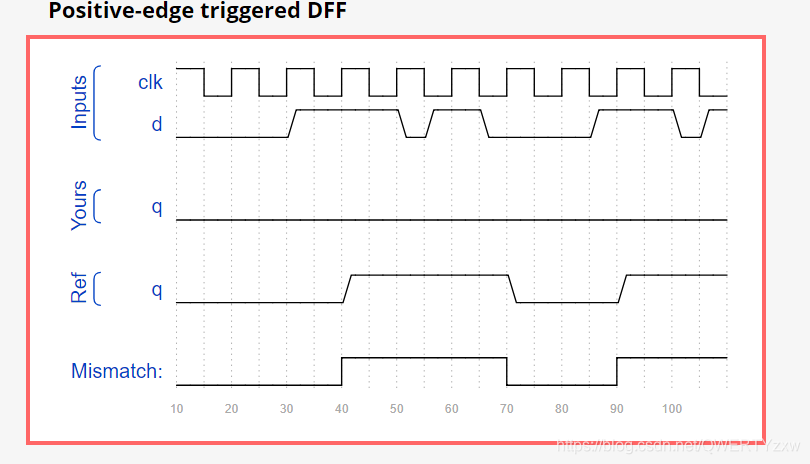

1、D触发器

模块声明:

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

endmodule

仿真结果:

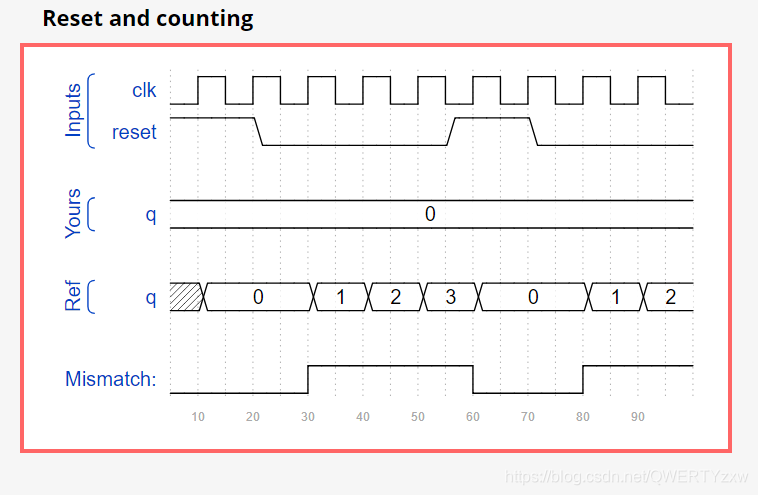

2、四位二进制计数器

模块声明:

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

endmodule

仿真结果:

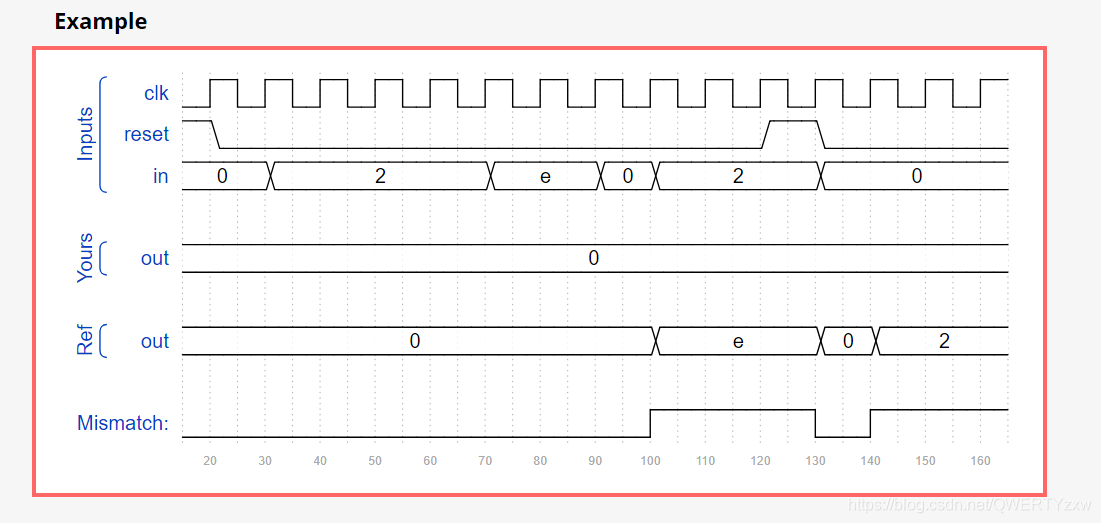

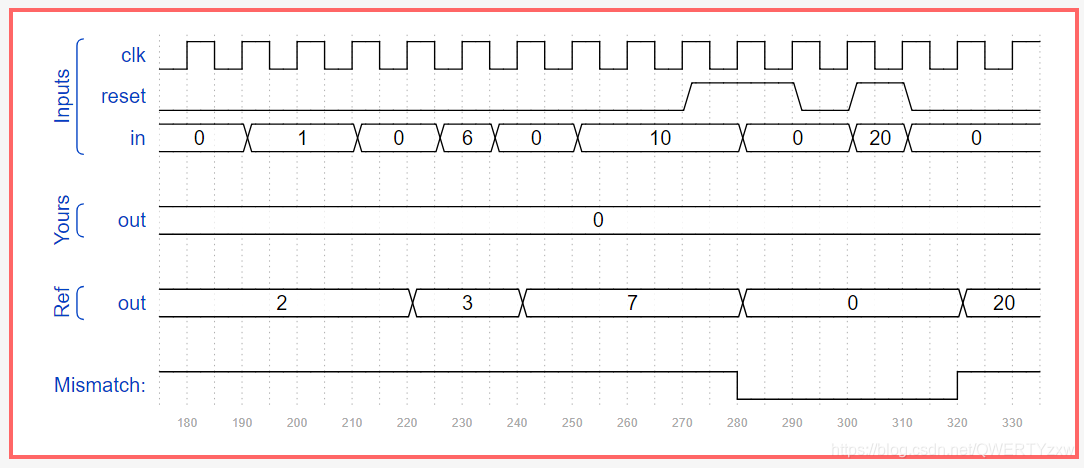

3、边缘捕获寄存器

模块声明:

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

endmodule

仿真结果:

四、总结与参考资料

1、总结

本篇文章对时序逻辑电路等的Verilog编程介绍。更多的学习可以参考下面资料。