Xilinx FIFO Generator 需要注意Actual Depth

系列文章推荐

- Xilinx FIFO Generator 需要注意RST复位

- Xilinx FIFO Generator 需要注意Actual Depth

- Xilinx FIFO Generator 需注意非对称位宽

- Xilinx FIFO Generator 需要注意BRAMs的资源消耗

又是没有仔细看手册掉入的坑,提醒一定注意例化FIFO的时候,注意FIFO的实际深度Actual Depth;

这么个现象

平时使用FIFO的时候,很少有使用到FULL的状态;而且由于开发板资源足够,所有的FIFO也都是留有一部分(至少30%)的冗余;

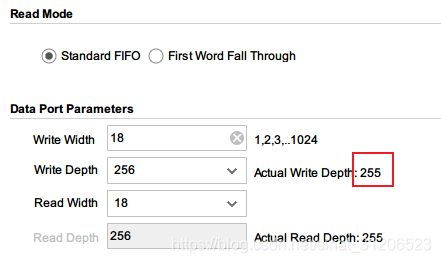

某次使用FIFO的时候 ,发现256的深度,老是计数记不到256,仿真中才发现,FIFO内部一共就只存进去了255个数据;

查看手册

在手册pg-057_fifo_generator.pdf的Page137中,对Actual FIFO Depth有详细介绍;

最重要的是理解FIFO的有效深度或者实际深度不是必须与在GUI中选择的一致,因为FIFO的实际深度取决于它的实现方式并且影响其实现的功能。在Vivado IDE中,FIFO的实际深度信息下面展示,下面部分提供了用于计算深度的信息。

Block RAM,Distributed RAM and Shift RAM FIFOs

这些FIFO的实际深度受影响于实现的改变,包含以下特点:

- Common or Independent Clock

- Standard or FWFT Read Mode

- Symmetric or Non-symmetric Port Aspect Ratio

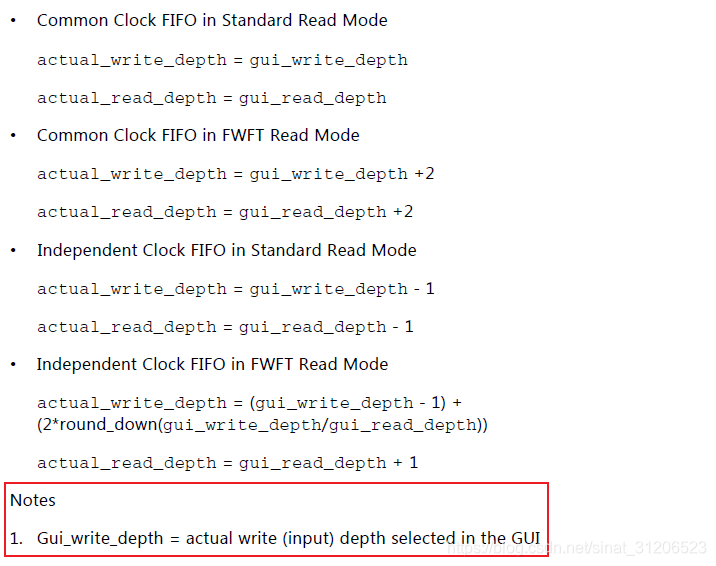

拒绝与FIFO的配置,FIFO的深度也不同: [外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-mzEXP2a1-1604323425225)(Xilinx FIFO Generate 需要注意Actual Depth.assets/image-20201102133808071.png)]

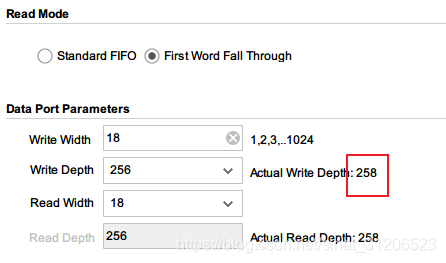

可以在FIFO Generator GUI中看到选在的FIFO配置不同,对应的Actual Depth有不同的显示:

- Common Clock FIFO in Standard Read Mode:

- Common Clock FIFO in FWFT Read Mode:

- Independent Clock FIFO in Standard Read Mode:

- Independent Clock FIFO in FWFT Read Mode:

Built_In FIFOs

Built-In FIFO的实际深度取决于下面由实现改变而引起的特点:

- Common or Independent Clock

- Standard or FWFT Read Mode

- Built-In FIFO primitive used in implenmentation(minimum depth is 512)

不同的FIFO配置不同,FIFO深度的计算也不同;

(非完整表,后续未展示)

Warning

在GUI上面进行FIFO配置的时候,一定要注意显示的内容;

如果对内容不理解,强烈建议GUI配置之后,单独IP跑仿真去观察重要信号的含义;

在Vivado中可以运行对实例化的FIFO IP 仿真,观察FIFO的容量,FULL,EMPTY等信号,可以了解FIFO的工作状态,对后续设计提供便捷性。