VIO(Virtual Input/Output)有两个主要功能

监测设计中的内部信号;

驱动设计中的内部信号。

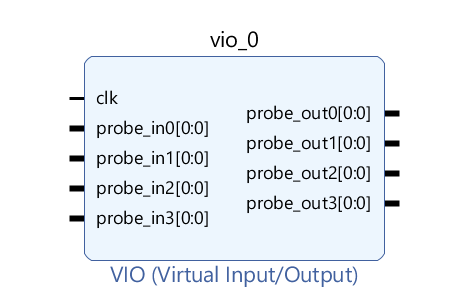

既然是Virtual(虚拟的),就表明这个输入或输出并不是真实存在于FPGA设计中。下图显示了VIO的输入、输出管脚。其中,输入、输出管脚最大可支持到256位。如果需要监测设计中的某个信号,则需要将该信号连接到VIO的输入端;如果需要驱动设计中的某个信号,则需要将该信号与VIO的输出端相连。

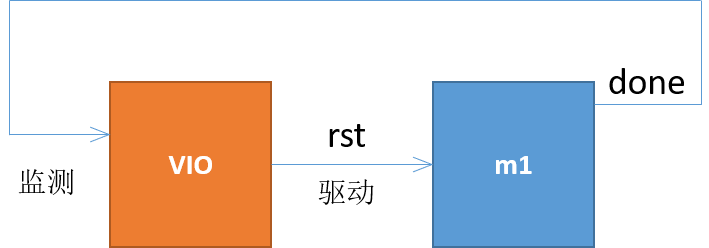

例如,需要监测模块m1的输出信号done,则将done信号连接到VIO的输入端probe_in0;同时需要驱动m1的复位信号,则将复位信号rst连接到VIO的输出端probe_out0。不难看出,就监测功能而言,VIO类似于一个简单的显示器,显示待监测信号的状态;就驱动功能而言,VIO类似于板卡上的一个按钮开关。

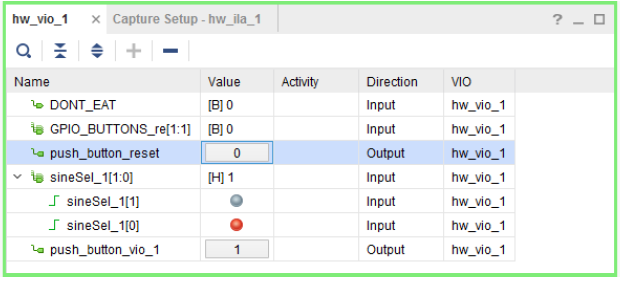

即使设计中只有VIO而没有ILA,Vivado也会生成相应的.ltx文件。打开Vivado Logic Analyzer之后,添加信号到VIO窗口,如下图所示,即可监测信号,或者改变驱动信号的值。

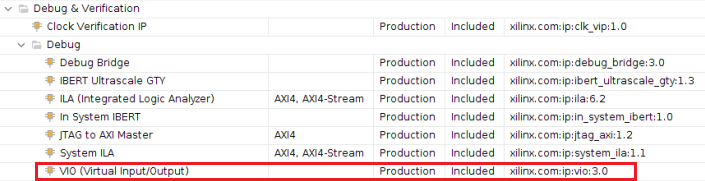

VIO以IP Core的形式存在于Vivado IP Catalog中,如下图所示。不同于ILA,VIO只能通过实例化的方式在设计中使用,而不能通过类似于ILA直接在综合后的网表中插入的方式使用。同时,也可以在Block Design中使用VIO。