对于寄存器,如果没有明确指定其初始值,Vivado会根据其类型(FDCE/FDRE/FDPE/FDRE)设定合适的初始值。有些工程师喜欢使用复位信号,对所有的寄存器进行上电复位,使其在处理数据之前达到期望初始状态。但这会有一个不利之处就是复位信号的扇出很大,从而消耗了大量的布线资源,甚至造成布线拥塞。那么能不能让寄存器在上电之后不用通过复位就输出期望值呢?答案是肯定的。

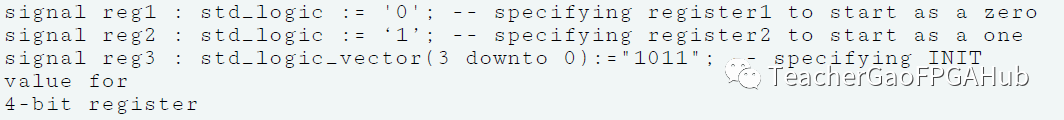

Xilinx也建议对于同步元件,最好设定其初始值。这里我们以最常用的寄存器为例。如果使用的是VHDL,可以采用下面的方法设定寄存器初始值,如下图所示。

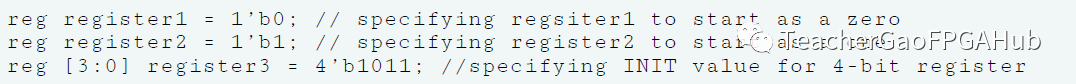

如果使用的是Verilog,可以采用下面的方法设定寄存器初始值,如下图所示。

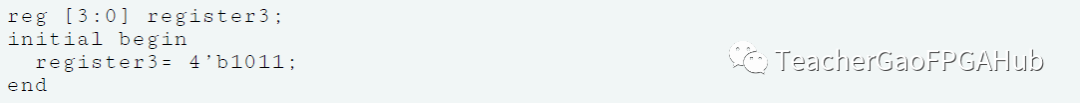

此外,对于Verilog,也可通过initial设定初始值,如下图所示。

采用这种方法的好处是:综合工具是支持的,这样生成bit文件时这些初始值会被写入配置文件中,上电即可生效,避免了使用复位造成的扇出过大;同时在仿真时,也能跟实际业务相匹配。

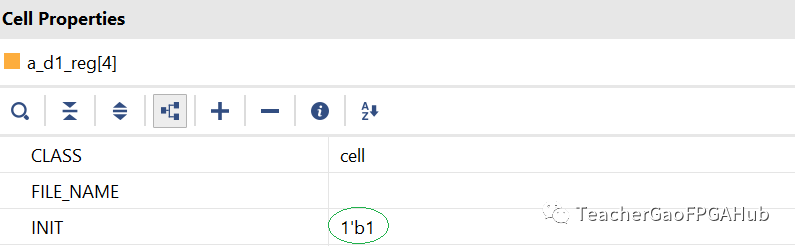

为了验证这个方法是否生效,只需要打开综合后的.dcp,找到相应的寄存器,在其Property窗口中查看属性INIT的值,如下图所示。