1.问题描述:

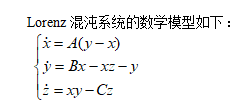

基于FPGA设计混沌信号发生器的一种改进方法。首先,采用Euler算法,将连续混沌系统转换为离散混沌系统。其次,基于IEEE-754单精度浮点数标准和模块化设计理念,利用Quartus II软件,采用VHDL和原理图相结合的方式设计混沌信号发生器。最后,在FPGA实验系统上进行实验,在示波器上显示了混沌吸引子的相图及时域混沌信号。由于采用了基于数据选择器的面积优化方法,复用耗费逻辑资源较多的浮点运算模块,大大减少了混沌信号发生器所占用的FPGA逻辑资源。实验结果证明了该方法的有效性和通用性。

2.部分程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY lpm;

USE lpm.all;

ENTITY MYDFF IS

PORT

(

clock : IN STD_LOGIC ;

data : IN STD_LOGIC_VECTOR (31 DOWNTO 0);

q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0)

);

END MYDFF;

ARCHITECTURE SYN OF mydff IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (31 DOWNTO 0);

COMPONENT lpm_ff

GENERIC (

lpm_fftype : STRING;

lpm_type : STRING;

lpm_width : NATURAL

);

PORT (

clock : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (31 DOWNTO 0);

data : IN STD_LOGIC_VECTOR (31 DOWNTO 0)

);

END COMPONENT;

BEGIN

q <= sub_wire0(31 DOWNTO 0);

lpm_ff_component : lpm_ff

GENERIC MAP (

lpm_fftype => "DFF",

lpm_type => "LPM_FF",

lpm_width => 32

)

PORT MAP (

clock => clock,

data => data,

q => sub_wire0

);

END SYN;

3.仿真结论:

A-007-0004