前言

写出这篇博客是因为在spartan6使用中,发现PLL产生的时钟不能直接接在通用I/O管脚上,两者之间通常会加上ODDR2缓冲来实现连接。

ODDR2模块

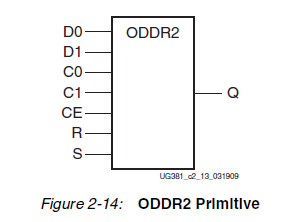

通过查看spartan6 selectio可知道ODDR2原语使用规则,其输入输出端口如下:

其引脚定义如下:

① D0、D1 : 输入数据;

② C0、C1 :输入时钟,C1是相对于C0的180°反相;

③ CE: 时钟使能,高电平有效;

④ R : 复位,通常设置1’b0;

⑤ S : 通常设置1’b0,R S不能同时为高;

⑥ Q : 数据输出;

模块调用

原语调用方式可以从ISE language templates中获取到:

ODDR2 #(

.DDR_ALIGNMENT(“NONE”), // Sets output alignment to “NONE”, “C0” or “C1”

.INIT(1’b0), // Sets initial state of the Q output to 1’b0 or 1’b1

.SRTYPE(“SYNC”) // Specifies “SYNC” or “ASYNC” set/reset

) ODDR2_inst (

.Q(Q), // 1-bit DDR output data

.C0(C0), // 1-bit clock input

.C1(C1), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D0(D0), // 1-bit data input (associated with C0)

.D1(D1), // 1-bit data input (associated with C1)

.R®, // 1-bit reset input

.S(S) // 1-bit set input

);

由上知参数设置有三项:

1、DDR_ALIGNMENT,设置对齐方式,ODDR2包括三种工作模式,这主要是根据对齐方式划分的。

①、NONE:两路数据D0、D1输入分别以C0、C1时钟作为参考时钟捕获数据。

②、C0:两路数据D0、D1输入分别以C0时钟作为参考时钟捕获数据,即两路数据对齐到C0时钟。

③、C1:两路数据D0、D1输入分别以C1时钟作为参考时钟捕获数据,即两路数据对齐到C1时钟。

2、INIT:设置输出信号初始状态

3、SRTYPE:设置输出信号是否同步

test

时钟通过ODDR输出到外部IO,ODDR2调用如下

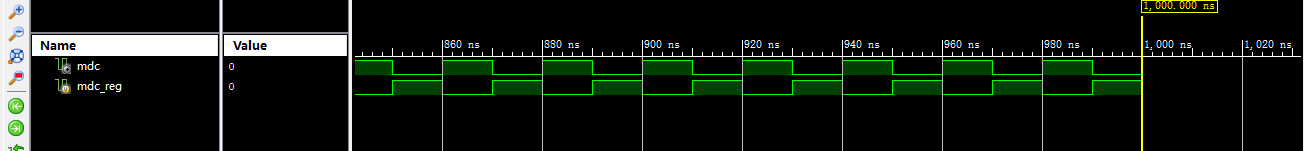

测试输入输出关系如下图:

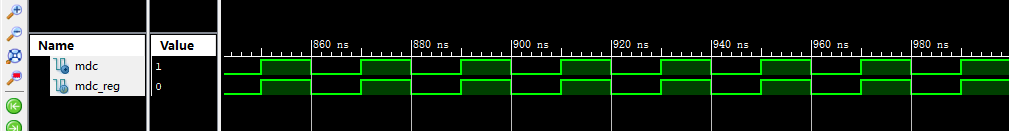

更换数据,相当于延时半个clk周期

测试输入输出关系如下图: