5.1 流水线数据相关问题

- 结构相关:由于硬件资源满足不了指令执行的要求,发生硬件资源冲突而产生的相关。比如,指令和数据都共享一个存储器,在某个时钟周期,流水线既要完成某条指令对存储器中数据的访问操作,又要完成后续的取指令操作,这样就会发生存储器访问冲突,产生结构相关。

- 数据相关:流水线中执行的几条指令中,一条指令依赖前面指令的执行结果。

- 控制相关:流水线中的分支指令或者其他需要改写PC的指令造成的相关。

- 本节重点讨论数据相关的问题,分三种情况:RAW,WAR,WAW

(1) RAW: read after write,指令j在指令i后,必须i执行完成之后j才能执行

(2) WAR:write after read,…

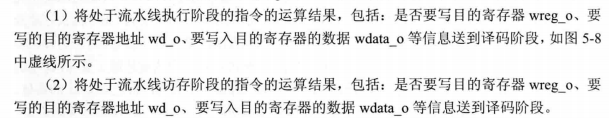

(3)WAW:write after write,指令j是在指令i后面执行的指令,i将数据写入寄存器后j再写入寄存器,否则该寄存器的值不是最新值。 - 分析流水线的工作流程,WAW和WAR都不存在,只存在RAW,包括3种情况:

(1)相邻指令间存在数据相关,也称为流水线译码,执行阶段数据相关

(2)相隔1条指令的指令间存在数据相关,也称为流水线译码,访存阶段数据相关

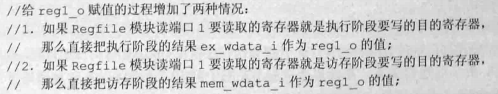

(3)相隔2条指令的指令间存在数据相关,也称为流水线译码,回写阶段存在数据相关 - (3)的解决方法,判断要读取的寄存器是否是在下一个时钟上升沿要写入的寄存器,那么将要写入的数据直接作为结果输出。

- 对于(1)和(2)的解决方法有三种:

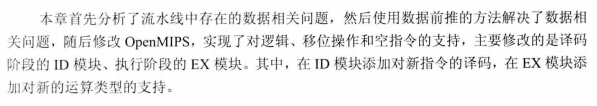

(1)插入暂停周期

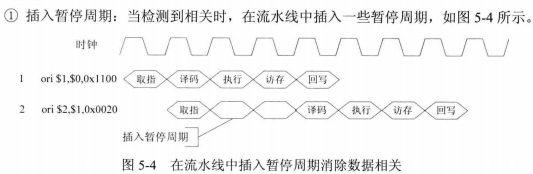

(2)编译器调度

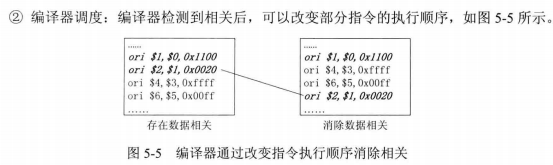

(3)数据前推:

5.2 OpenMIPS对数据相关问题的解决措施

- 采用数据前推的方法

译码阶段的ID模块回根据送入的信息,进行综合判断,解决数据相关,给出最后要参与运算的操作数。

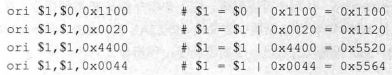

5.3 测试数据相关问题的解决效果

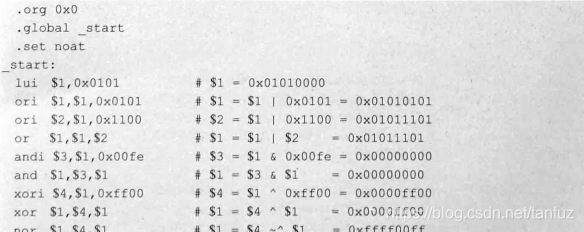

编译、仿真,观察$1变化过程是否与预期相同

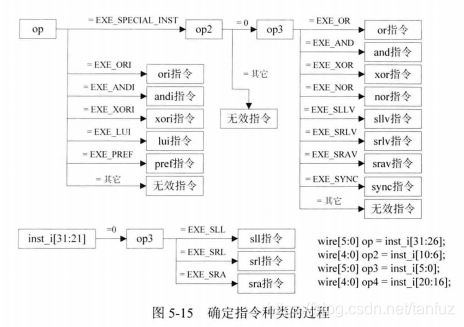

5.4 逻辑、移位操作与空指令说明

- 逻辑操作指令8条:and,andi,or,ori,xor,xori,nor,lui,其中or指令已经实现,现在补充实现其余7条指令

- 移位操作指令6条:sll,sllv.sra.srav.srl.srlv

- 空指令2条:nop,ssnop

- sync,pref两条指令分别用于保证加载存储顺序,缓存预取,在OpenMIPS中都当做nop指令

5.5 修改OpenMIPS以实现逻辑、移位操作与空指令

5.5.1 修改译码阶段的ID模块

5.5.2 修改执行阶段的EX模块

5.6 测试程序1-测试逻辑操作实现效果

5.7 测试程序2-测试移位操作与空指令实现效果

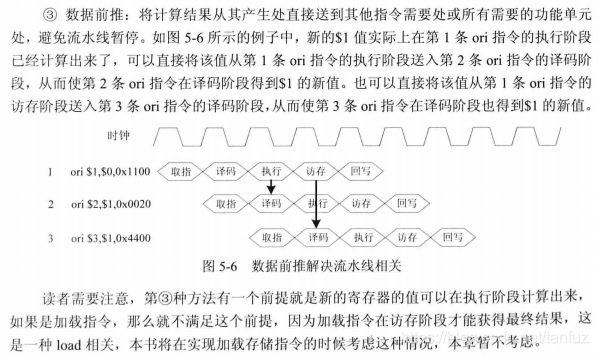

5.8 小结