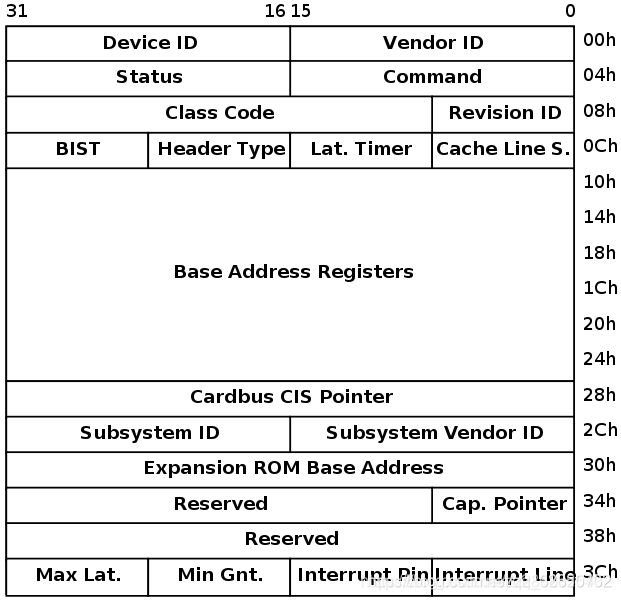

先给上面这个图,每一个PCI设备都有一个256 byte的配置寄存器空间,它分为64 byte的头标区(如上图所示,固定不变)和192 byte 的设备关联区(设备自己独有)。上图右边的呢,是表示4个 byte的递增。

1、前几个寄存器,是一些ID,操作系统根据其信息加载相应的驱动程序。

2、然后接着就有6个BAR,每一个BAR对应该设备里的一片存储器或IO空间,在上电的时候,BAR中的内容表达了该寄存器申请了多少存储器空间或IO空间,通过读这些BAR在系统的存储器和IO地址空间为其分配一片独立的存储器或IO地址空间,并把起始地址再写入BAR。(from 《pci原理及体系架构》)

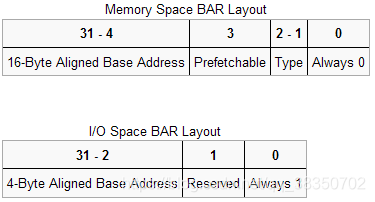

BAR记录了设备所需要的地址空间的类型(memory space或者I/O space),基址以及其他属性。BAR的格式如下:

可以看出,设备可以申请两类地址空间,memory space和I/O space,它们用BAR的最后一位区别开来。说到地址空间,计算机系统中,除了我们常说的memory address(包括逻辑地址、虚拟地址(线性地址)、CPU地址(物理地址)),还有I/O address,这是为了访问I/O设备(主要是设备中的寄存器)而设立的,

memory address和I/O address是共用一套地址总线,但通过控制总线上的信号区别当前地址总线上的地址是memory address还是I/O address。北桥芯片(Northbridge,Intel称其Memory Controller Hub,MCH)负责地址的路由工作,它内部有一张address map,记录了memory address,I/O address的映射信息,根据控制总线上的信号,北桥首先可以识别地址属于memory space还是I/O space,然后分别做处理。

比如若是memory space,则根据address map找出目标设备(DRAM或Memory Mapped I/O),若是DRAM或VGA,则转换地址然后发送给内存控制器或VGA控制器,若是其它I/O设备,则发送给南桥。

若是I/O space,则发送给南桥(Southbridge,Intel称其I/O Controller Hub,ICH),南桥负责解析出目标设备的bus, device, function号,并发送信息给它。

PCI设备可以通过两种方式将自己的I/O存储器(Registers/RAM/ROM)暴露给CPU:在memory space申请地址空间,或者在I/O space申请地址空间。这样,PCI设备的I/O存储器就分别被映射到CPU-relative memory space和CPU-relative I/O space,使得驱动以及操作系统得以正常访问PCI设备。