Verilog是综合的前端,HDL允许设计用工艺无关的方式来表示。然鹅,在编写设计的HDL描述方式上,综合加了一定限制。不是所有的HDL结构都能被综合,综合希望用特定的方式编写HDL代码,也可以说,综合是模板驱动的,用于综合的模板以及器编码模式称为编码风格。为了得到更好的结果,设计人员必须对编码风格、逻辑推断及DC生成的对应逻辑结构进行深入的理解;

不完全敏感列表

敏感列表中确实触发进程的激活信号。

存储元件推断

存储元件:锁存器和触发器。锁存器是电平敏感存储元件,触发器是边沿敏感。只要锁存器的使能是有效的,锁存器就是透明的。一旦锁存器的使能无效,则输出Q保持输入D的值不变。触发器由时钟的上升或下降沿触发。锁存器是简单器件,因而与触发器相比占的面积要小。锁存器通常比较麻烦,因为设计中会因为锁存器的存在使得DFT的扫描变得困难,设计中应尽量避免锁存器以及在需要的时候会推荐锁存器。

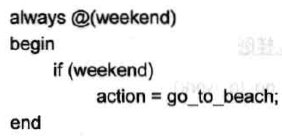

锁存器推断

当条件语句没有完全指定时就会推断出锁存器。如确实else部分的if语句就是一个不完全指定条件的例子。上述语句可使得DC推断一个由信号“weekend"使能的锁存器,解决方案,假设else语句,或者在if之外使用default语句实现。

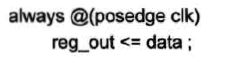

寄存器推断

为了支持不同的时钟边沿类型和复位机制,DC为寄存器推断提供了各式模板,当敏感信号列表中指定了一个边沿就可以推断出一个寄存器,这个边沿可以是正沿也可以是负沿。使用如下的模板推断出简单的正沿触发的D触发器:

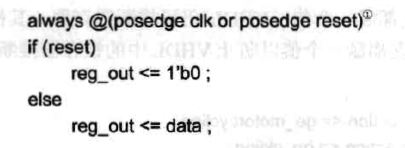

为了推断出带复位的寄存器,向敏感列表中添加复位信号并在always块中编写复位逻辑,以下是一个带异步复位的D触发器的例子:

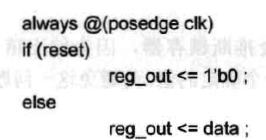

简单的把reset信号从敏感信号列表中去掉,即得到同步复位,由于过程块由时钟沿触发,所以也只在时钟边沿进行复位。

多路选择器推断

通常if语句用于推断锁存器和优先级编码器。而case语句用来推断多路选择器。

1、使用case语句的多路选择器

为了避免在case中推断出锁存器,default语句不可或缺。例如,对于状态机,default子句覆盖了所有状态引起到”开始“状态的跳转。

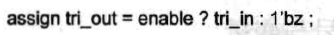

三态推断

当高阻(Z)赋值给输出时,推断出三态逻辑。通常不提倡随意使用三态逻辑,因为:

1、三态逻辑降低可测性;

2、三态逻辑难以被优化,因为它不能被缓冲,导致max_fanout违例和重负载连线;

优点:能显著节省面积;

逻辑推断

猜你喜欢

转载自blog.csdn.net/lilliana/article/details/106618843

今日推荐

周排行