目录

一、SDRAM基本介绍及实验平台:

1、SDRAM简介:

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM),可以实现数据的存储和读取。这里主要注意的是同步、动态、随机。

同步:SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。这个词在FPGA中经常遇到,体现了SDRAM必须遵守的时序要求,就是数据、命令在时钟上进行同步。

动态:RAM这中存储结构会掉电丢失,在上电的时候也会丢失。因为SDRAM内部存储的数据是二进制数据,非0则1。用来存储该二进制数据的电路是由电容构成的,由于电容这种器件会随着时间而慢慢放电,因此需要不断地去刷新里面的存储电路,以此来达到存储数据的功能。相较于SRAM的不需要刷新电路就能存储数据来说,在SDRAM多了一步刷新操作,但可以节约大量成本,因此选取器件需要从功能和成本等很多方面考虑。

随机:从字面意思可以看出,SDRAM是可以对内部地址随机地进行数据存取操作的。

2、SDRAM历史:

SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

第一代SDRAM采用单端(Single-Ended)时钟信号,第二代、第三代与第四代由于工作频率比较快,所以采用可降低干扰的差分时钟信号作为同步时钟。

SDR SDRAM的时钟频率就是数据存储的频率,第一代内存用时钟频率命名,如pc100,pc133则表明时钟信号为100或133MHz,数据读写速率也为100或133MHz。

之后的第二,三,四代DDR(Double Data Rate)内存则采用数据读写速率作为命名标准,并且在前面加上表示其DDR代数的符号,PC-即DDR,PC2=DDR2,PC3=DDR3。如PC2700是DDR333,其工作频率是333/2=166MHz,2700表示带宽为2.7G。

DDR的读写频率从DDR200到DDR400,DDR2从DDR2-400到DDR2-800,DDR3从DDR3-800到DDR3-1600。

很多人将SDRAM错误的理解为第一代也就是 SDR SDRAM,并且作为名词解释,皆属误导。

SDR不等于SDRAM。

3、实验的SDRAM介绍:

1.存储器架构

本实验使用的是winbond公司的W9812G6KH-6型号的SDRAM芯片,使用的小梅哥的AC620FPGA开发板,写SDRAM接口前首先要了解一下这个SDRAM的系统架构以及总体概述。从网上可以下载到这个型号存储器的数据手册:

图1:IS42S16400F存储器架构

IS42S16400F存储器主要包括指令译码器、地址线、数据线、存储块、模式寄存器和动态电路控制。

(1)指令译码器

指令译码器中包括时钟信号(clk)和时钟使能(cke)以及控制指令信号(cs/ras/cas/we),控制指令信号通过译码后对存储器进行一系列控制动作。

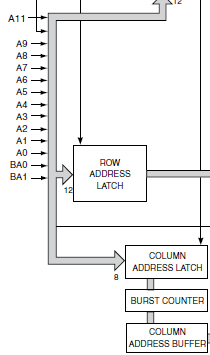

(2)地址线

地址线包括16位行列地址线及2位块地址线,行列地址线是A0-A11,是复用总线,行列地址分时复用。块地址线ba0和ba1选取存储器的块ram。

(3)数据线

数据线为16位数据总线dq,为三态信号,是数据写入和读出的数据接口。

(4)存储块

IS42S16400F共有四个存储块,每个块都可以存储数据,可以通过ba0和ba1选取存储块。

(5)模式寄存器

模式寄存器是配置该SDRAM的工作模式,读写方式、突发长度等。

(6)动态电路控制

这几个模块主要包括行列地址的编码、自刷新定时和自刷新操作。

2.基本特点

(1)时钟频率:200,166,143MHz)

(2)完全同步,时钟上升沿输出数据

(3)3.3V供电

(4)可编程冲突长度(1,2,4,8,全页)

(5)每64ms刷新4096次

(6)可编程cas延时(2,3个时钟周期)(这里后边会讲)

(7)突发读写或单读写

(8)字节由LDQM和UDQM控制

(9)存储量1Mbit * 16bit * 4Bank = 64Mbit

存储深度:IS42S16400F有4个块,行地址12bit,列地址8bit。所以每个块有2^12 * 2^8 = 4096 * 256 = 1,048,576

存储宽度:每个存储单元16bit

存储容量:4 * 1,048,576 * 16 = 64Mbit

二、SDRAM—W9812G6KH-6功能描述:

1、总体描述:

64Mb SDRAM是一个高速CMOS,动态设计用于3.3V的随机存取存储器,可存储67,108,864位数据。每个16,777,216位的存储区被组织为4,096行 x 256列个存储单元,每个单元存储16位数据。

64Mb SDRAM包括一个自动刷新模式、省电和掉电模式。所有信号都是在时钟信号CLK的上升沿寄存。

所有输入和输出均兼容LVTTL。

64Mb SDRAM具有同步冲突的能力,突发结束时启动自定时行预充电。

在访问其中一个Bank时,为一个Bank预充电其他三个银行将隐藏预充电周期并提供无缝,高速,随机访问操作。

SDRAM读写访问是面向突发的,读写访问选定的位置并继续对选定位置下继续访问。读写访问前需要一个激活命令,然后是READ或WRITE命令,结束后启动预充电。可编程的READ或WRITE突发长度包括1、2、4和8个位置或整页,带有突发终止选项。

2、大体工作过程:

通电时首先初始化SDRAM,其初始化过程包括:

(1)上电等待时钟稳定,DQM高,CKE高。

(2)200μs的延迟,期间除了No – Operation命令,其他命令不能有。在此期间至少有一个 No – Operation命令。

(3)200us后给出PRECHARGE命令。给所有Bank预充电,使所有Bank处于空闲状态。

(4)两个自动刷新操作。

(5)配置模式寄存器。

初始化后,SDRAM就处于空闲状态,就可以对SDRAM进行其他操作,例如读操作,写操作,自动刷新操作。自动刷新操作从上篇文章中写到,每64ms刷新4096次,就是每64ms就对4096行存储单元刷新一次,防止数据丢失。读写操作前都必须有激活命令(ACTIVE),对确定的bank和确定的行进行激活,再进行读写操作,读写完需要预充电命令。

引脚功能介绍:

以下为IS42S16400F芯片引脚图及引脚描述表:

A0-A11(Input):地址输入。在ACTIVE命令(行地址A0-A11)和READ / WRITE命令(A0-A7,其中A10定义自动预充电)期间采样A0-A11,以从相应存储体的存储器阵列中选择一个位置。 在PRECHARGE命令期间对A10进行采样,以确定是否要对所有存储体进行预充电(A10为高)或由BA0,BA1选择的存储体为(LOW)。 地址输入还在LOAD MODE REGISTER命令期间提供操作码。

DQ0-DQ15(Inout):I / O引脚。 通过这些引脚的I / O可以使用LDQM和UDQM引脚以字节为单位进行控制。

BA0, BA1(Input):Bank选择地址。BA0和BA1定义了正在应用ACTIVE,READ,WRITE或PRECHARGE命令的存储体。

CLK(Input):CLK是该设备的主时钟输入。 除CKE以外,与此引脚的上升沿同步获取该器件的所有输入。

CKE(Input):CKE输入确定是否启用CLK输入。 CLK信号的下一个上升沿在CKE为高电平时有效,而在低电平时无效。当CKE为LOW时,器件将处于掉电模式,时钟挂起模式或自我刷新模式。 CKE是异步输入。

CS(Input):CS输入确定是否在设备内启用了命令输入。当CS为LOW时启用命令输入,而CS为HIGH则禁用命令输入。 当CS为高电平时,设备保持先前状态。

CAS(Input):CAS与RAS和WE一起构成设备命令。 有关设备命令的详细信息,请参见“命令真值表”(下边会给出)。

RAS(Input):RAS与CAS和WE一起构成设备命令。 有关设备命令的详细信息,请参见“命令真值表”(下边会给出)。

WE(Input):WE与RAS和CAS一起形成设备命令。 有关设备命令的详细信息,请参见“命令真值表”(下边会给出)。

LDQM,UDQM(Input):LDQM和UDQM控制I / O缓冲区的低字节和高字节。 在读取模式下,LDQM和UDQM控制输出缓冲区。 当LDQM或UDQM为LOW时,相应的缓冲字节被使能,而当HIGH时,其禁用。 LDQM / UDQM为高电平时,输出进入高阻抗状态。 此功能对应于常规DRAM中的OE。 在写模式下,LDQM和UDQM控制输入缓冲区。 当LDQM或UDQM为LOW时,启用相应的缓冲区字节,并且可以将数据写入设备。 当LDQM或UDQM为高电平时,输入数据被屏蔽,无法写入设备。

VDDQ(pow):输出缓冲电源。

GNDQ(pow):输出缓冲地。

VDD(pow):设备内部电源。

GND(pow):设备内部地。

下表是命令和DQM操作的真值表:

SDRAM由CS/RAS/CAD/WE控制的主要命令有:PRECHARGE、ACTIVE、AUTO_REFRESH、READ、WRITE、No – Operation、Mode Register Set。