FlexSPI是一个功能强大的接口,和普通SPI相比,使用比较复杂,较难上手。近期调试FlexSPI与FPGA接口,将通过系列博客进行记录。

先看RT1052参考手册1694页

在这之前先介绍一个概念:serial root clock ,手册中提及的serial root clock 是FlexSPI接口工作的基础时钟,SCK可以在serial root clock的基础上得到。在SDR模式下,SCK周期是serial root clock的两倍,DDR模式下,SCK周期等于serial root clock。之前对这部分理解有误。

/* Set flexspi root clock to 332MHZ. */

const clock_usb_pll_config_t g_ccmConfigUsbPll = {.loopDivider = 0U};

CLOCK_InitUsb1Pll(&g_ccmConfigUsbPll);

CLOCK_InitUsb1Pfd(kCLOCK_Pfd0, 26); /* Set PLL3 PFD0 clock 332MHZ. */

CLOCK_SetMux(kCLOCK_FlexspiMux, 0x3); /* Choose PLL3 PFD0 clock as flexspi source clock. */

CLOCK_SetDiv(kCLOCK_FlexspiDiv, 5);

27.5.13 FlexSPI输出时序

本节描述FlexSPI中的输出计时。

27.5.13.1 数据与SCLK之间的输出时序

本节描述数据(A口/B口)和SCLK的输出时序关系。数据输出定时有三种情况:

SDR序列中的SDR指令

SDR序列是只包含SDR指令的序列。在这种情况下,所有数据位在FlexSPI接口持续一个串行根时钟周期。下面的图表示了串行根时钟、数据和SCLK的关系:

DDR序列中的SDR指令

DDR序列是一个flash访问命令序列,它包含的DDR指令不是无效填充的,它可以选择性地包含SDR指令。在DDR序列的SDR指令情况下,所有数据位在FlexSPI接口持续两个串行根时钟周期。下面的图表示了串行根时钟、数据和SCLK的关系:

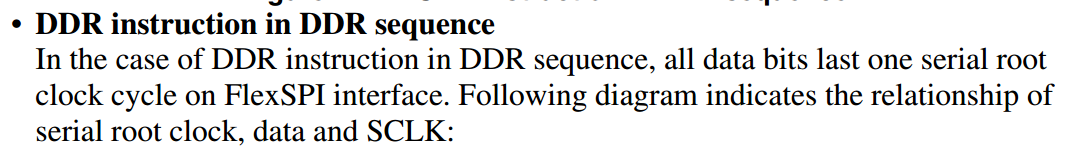

DDR指令按DDR顺序执行

在DDR指令在DDR序列的情况下,所有的数据位在FlexSPI接口持续一个串行根时钟周期。下面的图表示了串行根时钟、数据和SCLK的关系:

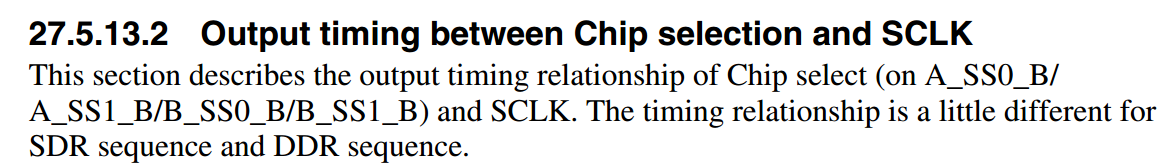

27.5.13.2 CS与SCLK之间的输出时序

本节描述芯片选择(在A_SS0_B/A SS1 B/B_SS0 B/B_SS1 B)和SCLK的输出时序关系。SDR序列和DDR序列的时间关系略有不同。

SDR序列下的片选时序

对SDR序列来说,从CS片选有效到SCLK上升边的时延为(FLSHxCR1[TCSS]+0.5)个串行根时钟周期;

从SCLK下降沿到片选无效的延迟是FLSHxCR1[TCSH]个串行根时钟周期。片选与SCLK之间的时序关系如下图所示:

•DDR顺序的片选时序

对于DDR序列,芯片选择有效和SCLK上升边产生的延迟为(TCSS+0.5)个串行根时钟周期;来自SCLK下降边缘和芯片选择无效的延迟是(TCSH+0.5)个串行根时钟的周期。芯片选择与SCLK之间的时序关系如下图所示:

对于某些设备(如FPGA设备),芯片选择有效的间隔是有限制的。如果寄存器字段FLSHxCR1[CSINTER VAL]被设置为非零值,FlexSPI将确保芯片选择之间的延迟时间有效。延迟时间为:CSINTERVAL*1024周期的串行根时钟,无论SDR或DDR序列。

如果外部设备没有此限制,请将此寄存器字段值设置为零。下图显示了芯片选择间隔的时间。

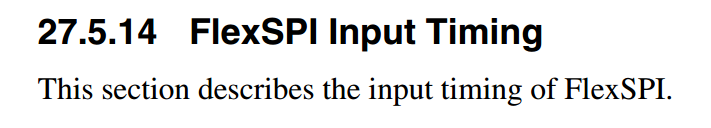

27.5.14 FlexSPI输入时序

本节描述FlexSPI的输入时序。

27.5.14.1 RX时钟源特性

本节描述每个RX时钟源的特性。

内部虚拟读探测和内部环回流(MCR0 [RXCLKSRC = = 0) (kFLEXSPI_ReadSampleClkLoopbackInternally)

支持零设备输出保持时间的遗留设备;

节省一个引脚(DQS pad);

支持低频时钟开机使用。

内部虚拟读探测和环路从DQS引脚(MCR0[RXCLKSRC]==1)(kFLEXSPI_ReadSampleClkLoopbackFromDqsPad)

比上一种模式频率更高(66M);

支持不提供读选通脉冲的器件。

Flash提供读取选通脉冲信号(MCRO[RXCLKSRC]==3) (kFLEXSPI_ReadSampleClkExternalInputFromDqsPad)

支持最高频率(166M);

支持装置提供读取选通脉冲。

27.5.14.2用伪读选通脉冲采样的输入时序

本节描述了使用内部虚拟读取读选通脉(MCR0[RXCLKSRC]设置为0x0或0x1)采样时的输入时序。内部虚拟读环回和从DQS引脚环回的时序是非常类似的。但在DQS引脚上采用虚拟读环回采样,可以补偿SCLK输出路径和数据引脚输入路径的延迟,从而实现更高的读取频率。SDR模式和DDR模式的输入时序不同。

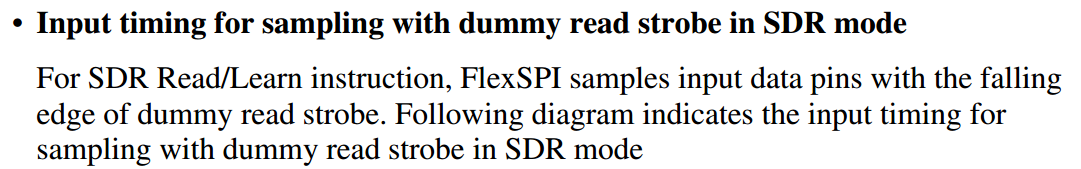

在SDR模式下使用虚拟读取脉冲进行采样的输入时序

对于SDR读/学习指令,FlexSPI用虚拟读脉冲的下降边对输入数据引脚进行采样。下图显示了SDR模式下使用虚拟读取脉冲采样的输入时序

DDR模式下使用伪读脉冲进行采样的输入时序

对于DDR读/学习指令,FlexSPI在虚拟读脉冲上升和下降边缘采样输入数据引脚。下图显示了DDR模式下使用伪读脉冲进行采样的输入时序

27.5.14.3 带有读脉冲采样的输入时序

本节描述了用外部提供的读脉冲进行采样时的输入时序(MCRO[RXCLKSRC]设置为0x3)。SDR模式和DDR模式的输入时序不同。

注意:没有已知的器件能提供读脉冲并且支持SDR模式操作。

有两种FLASH提供的读脉冲:

FLASH提供读取脉冲与SCLK

对于某些闪存设备,它通过SCLK提供读数据和读脉冲。然后读取脉冲边缘与读取数据变化对齐。FlexSPI控制器应该延迟读脉冲半个周期用串行根时钟(带有DLL),然后用延迟后的读脉冲采样读数据。有关采样的详细信息,请参考DLL配置。下图显示了SDR模式和DDR模式下脉冲采样的输入时序:

27.5.14.4 DLL 采样 配置

四个采样时钟源的输入时序是不同的。这是通过根据采样时钟源模式不同地设置寄存器DLLxCR来处理的。DLL是一个硬件延迟线链,它可以被设置为一个固定数量的延迟单元或自动调整锁定在参考时钟的某个相位延迟。

在以下情况下,DLLxCR设置为0x00000100 (DLL延迟链中1个固定延迟单元)

采样数据与虚拟读脉冲环回内部(MCR0[RXCLKSRC] = 0x0)

用虚拟读脉冲从DQS引脚环回采样数据(MCR0[RXCLKSRC]= 0x1)

当Flash提供读脉冲(MCR0[RXCLKSRC]=0x3)和Flash提供读脉冲用SCLK采样数据时,应设置DLL为:锁定参考时钟(串行根时钟)的半个周期

SLVDLYTARGET=0xF

DLLEN=0x1

OVRDEN=0x0

DLLxCR中的其他字段应该保持复位值(0)

注意

如果串行根时钟低于100M。DLL无法锁定串行根时钟的半周,因为延迟单元数在延迟链中是有限的。那么DLL应该配置如下:

OVRDEN = 0x1

OVRDVAL=N;

DLL中每个延迟单元约为75 ps-225 ps(Delay_cell delay), DLL延迟链的时延为(N * Delay_cell delay), N应根据最大值进行设置。

当前项目支持的DDR频率,N = 17,请注意这是一个推荐值。如果失败,可能需要在实际应用中调整。

DLLxCR中的其他字段应该保持为重置值(全部为零)。

小结

以上,手册中的基本内容介绍完毕,下一篇介绍程序配置。