看书的一个学习过程,做一个记录,欢迎指正....

s3c2440时钟控制既可以接

外接晶振,或者通过

内部电路产生时钟源,或者采用

外部提供的时钟源。

时钟控制逻辑提供三种时钟:

FCLK: 用于CPU核

HCLK:AHB(Advanced High Performance Bus)总线上设备,高性能模块。如中断,LCD,DMA等

PCLK: APB总线上设备,低快带模块 如UART、I2C等

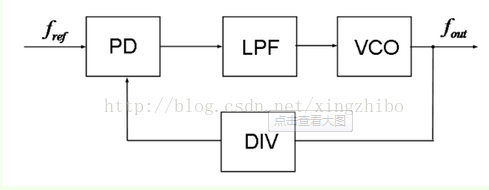

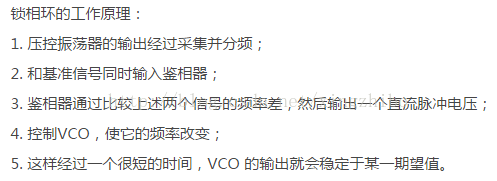

PLL:锁相环,在数字电路中用于保证 输入、输出的频率和相位相同。可以用来实现分频和倍频。

锁相环的特点:利用外部输入的参考信号控制环路内部震荡信号的频率和相位。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压 的相位被锁住,这就是锁相环名称的由来

PD:鉴相器 LPF :环路滤波器 VCO :压控振荡器题外话: PLL怎样实现分频和倍频

有时间可以详细理解,就是一个自动控制反馈过程。

s3c2440有俩个PLL:MPLL 和UPLL. UPLL用于USB。 MPLL用于FCLK、PCLK、HCLK

系统提高系统时钟的过程,来匹配CPU

s3c2440有俩个PLL:MPLL 和UPLL. UPLL用于USB。 MPLL用于FCLK、PCLK、HCLK

系统提高系统时钟的过程,来匹配CPU

上图中VCO用于配合锁相环,调整频率

倍频过程:

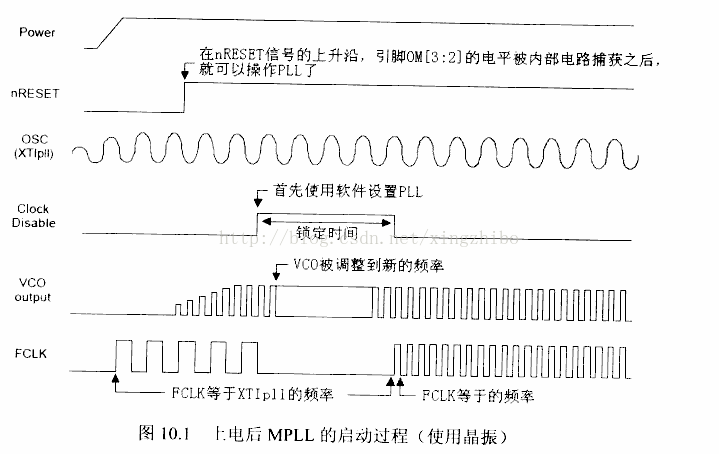

1.上电时,PLL没有启动,没有倍频、分频,采用外部晶振频率,所以此时FCLK = 12M。再往后,nREST信号上升沿触发,CPU开始执行指令。

我们设置OM[3:2]来为s3c2440选择时钟源,这个s3c2440默认是接地的,采用晶振用来倍频。

2.

我们可以程序开头启动MPLL,设置MPLL的几个寄存器,过一段时间(称为Lock Time)MPLL稳定,此阶段FCLK停振。

3.LockTime之后,CPU以新的FCLK开始运行。

程序实现:

1.<LOCKTIME寄存器>设置LockTime

默认

2.<MPLLCON寄存器>MPLL(FCLK) = (2 * m * Fin) / (p * 2 ^s); //LockTime之后,CPU工作在新的FCLK,一个

倍频或分频过程

m = MDIV + 8.p = PDIV + 2 s = SDIV

3.<CLKDIVN寄存器>设置FCLK、PCLK、HCLK

比例。对于s3c2440还要设置一个CAMDIVN

可以查看s3c2440芯片手册,阅读详细信息。

s3c2440有俩个PLL:MPLL 和UPLL. UPLL用于USB。 MPLL用于FCLK、PCLK、HCLK

系统提高系统时钟的过程,来匹配CPU