结构化模型

电路的功能和结构

调用专用硬件,低级元件

可综合

结构化设计

VHDL 结构化设计需要元件声明和元件例化

结构化声明

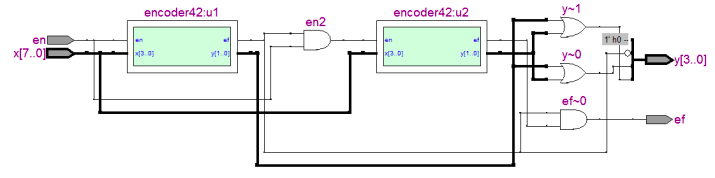

结构化VHDL描述了元件的安排和内联.

注意与行为描述之区别,行为描述是描述对输入信号的响应

结构化描述可以表示出代码和物理硬件之间更紧密的关系.

结构化描述展示了任何抽象级别之间的连接.

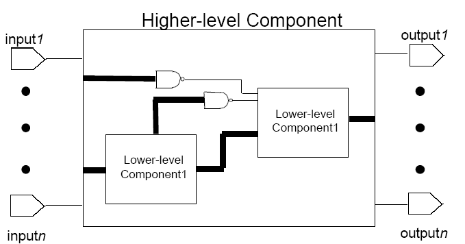

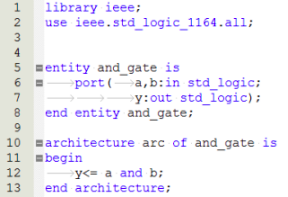

元件

一个元件代表一个实体-结构对.

使用元件可设计更复杂的电路.

一个元件例化语句定义了设计实体中的位于更低层次的部分,

使用信号将实体之间的端口相连接。可以对元件的类属进行赋值。

元件必须在一个包中或者在结构中事先声明。

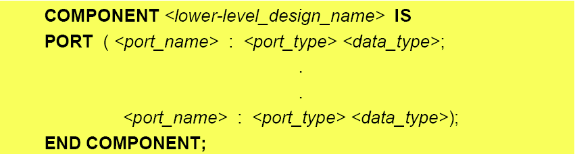

元件声明和元件例化语句

元件声明:用于声明端口类型和数据类型

元件例化:端口映射

元件例化是结构化描述的一个模块.

元件例化过程需要元件声明和元件例化语句.

元件例化声明了在结构内部元件之间的接口关系.

例化时,仅接口可见

元件内部隐藏.

例子:

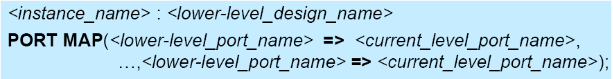

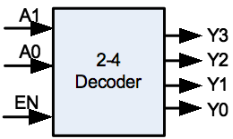

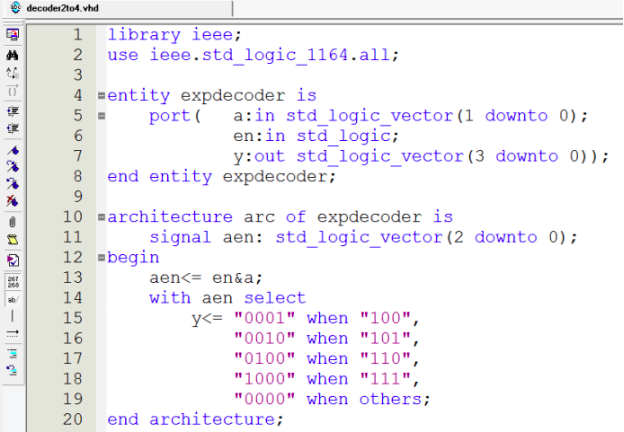

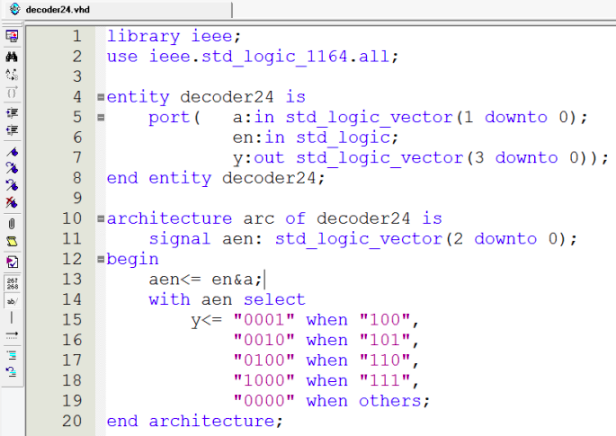

2-4 Decoder

功能描述

(1) EN=‘0’, Y <= “0000”;

(2) EN=1,

A=“00”, Y <=“0001”

A =“01”, Y<=“0010”

A =“10”, Y<=“0100”

A =“11”, Y<=“1000”

NOTE: A = A1A0 Y = Y3Y2Y1Y0

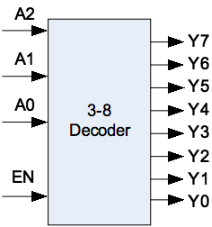

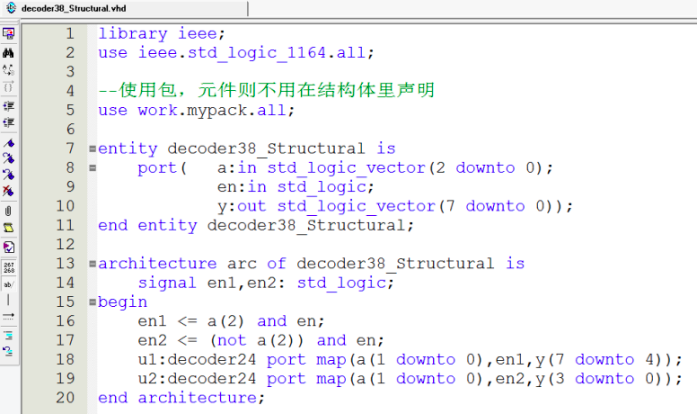

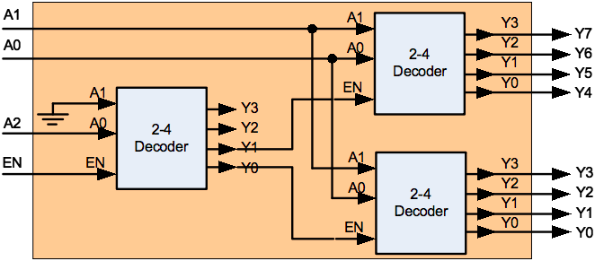

3-8 Decoder

功能描述

(1) EN=0, Y<=x“00”

(2) EN=1,

If A2A1A0=“000”, Y<=x“01”;

If A2A1A0=“001”, Y<=x“02”;

If A2A1A0=“010”, Y<=x“04”;

If A2A1A0=“011”, Y<=x“08”;

If A2A1A0=“100”, Y<=x“10”;

If A2A1A0=“101”, Y<=x“20”;

If A2A1A0=“110”, Y<=x“40”;

If A2A1A0=“111” , Y<=x“80”

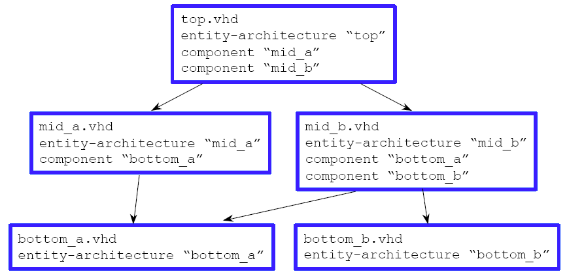

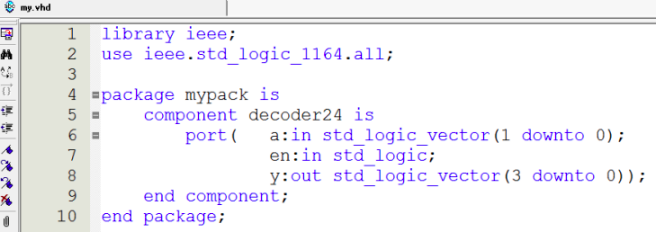

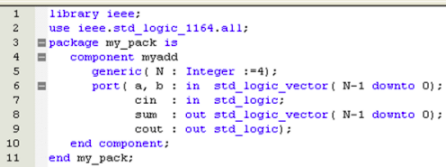

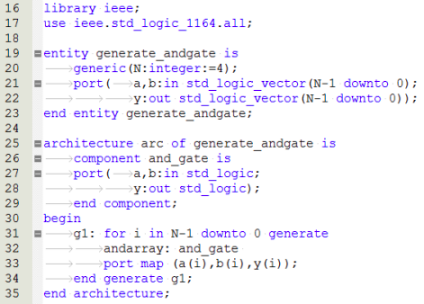

元件库

元件可在包内声明. 并不一定非要在结构内

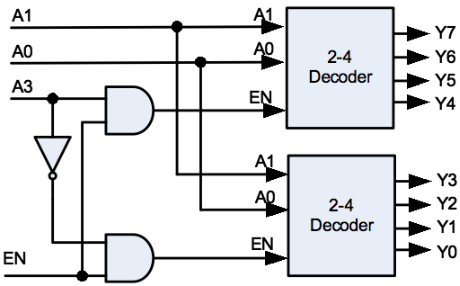

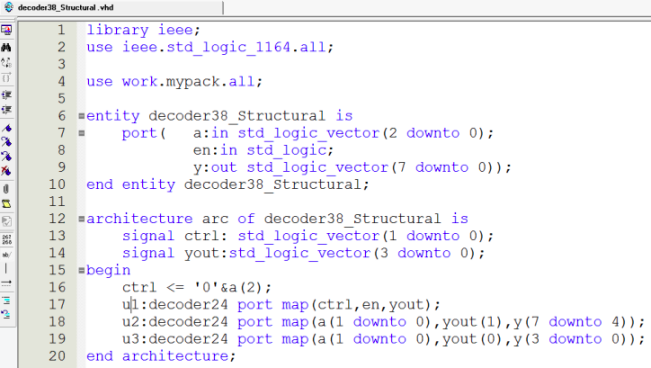

Another 3-8 Decoder

类属

在例化之前,类属可使用户自定义元件.

使用类属在实体和结构之间传递信息.

类属的使用

自定义定时

改变子类型范围

改变数组大小

类属映射类似于端口映射,它是将某个值传递给类属.

generic Map(L)

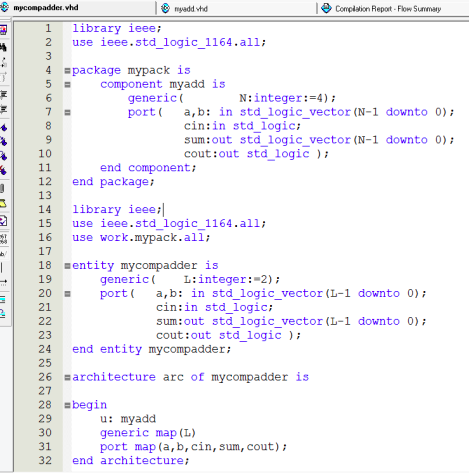

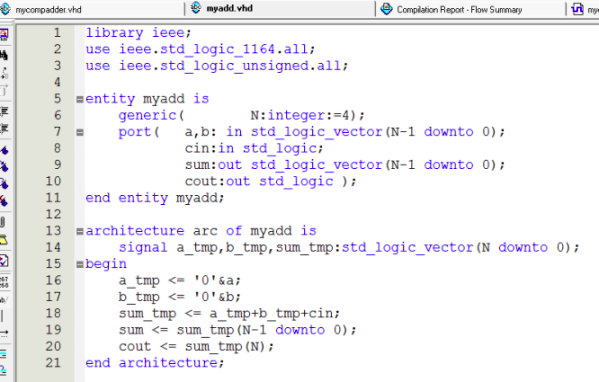

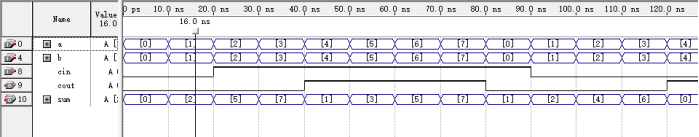

可变总线宽度的全加器

注意:

a_tmp <= '0' & a ;

这个叫做并置,看到没有,在定义Signal 时都是预留多一位。

sum_tmp <= a_tmp + b_tmp + cin ;

std_logic_vector的加法,就是加法。

cin 作为1位的std_logic自动会转化到最低位。

cout <= 截取低N位 (N -> 0) , ( N-1 -> 0)

当L=3:

当L=2:

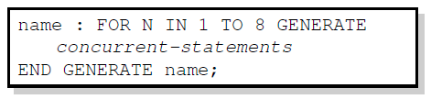

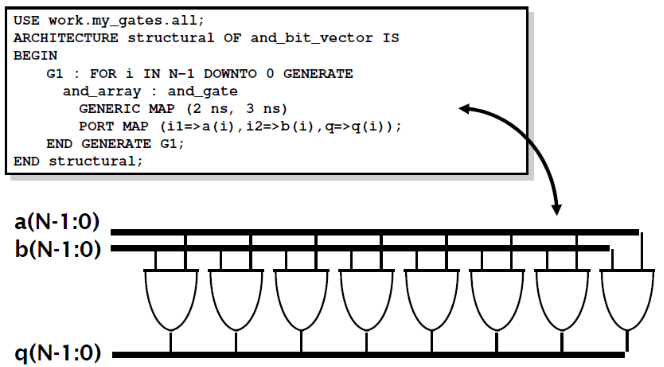

Generate 语句

结构化 for-loop: Generate语句

有些数字硬件中的结构是可重复的. (RAM, ROM, registers, adders, multipliers, …)

VHDL 提供 GENERATE 语句自动产生元件.

任何VHDL并发语句都可以包含在GENERATE语句中.

所有的对象以相同的方式产生.

GENERATE 参数必须是离散的,并在GENERATE 语句之外声明.

例子:AND门阵列

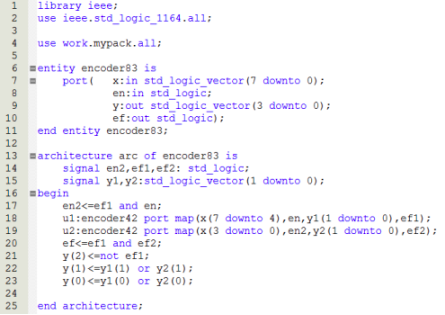

8-3 优先级编码器