在从零开始学编码5中使用双掷继电器设计了四种基本逻辑门(与门、或门、或非门、与非门),双掷继电器有缓冲器串联为与门,并联为或门;反向器串联为或非门,并联为与非门。

这次我们来看看如何使用逻辑门来搭建一个二进制加法器,而减法、乘法和除法都可以用加法来实现。在计算机发展史的早期,有大能设计了机械结构的十进制加法器,但是被历史所淘汰。现在我们所使用的计算机cpu都是二进制,之所以使用二进制,是因为在很容易实现两种状态,高电平和低电平,现在的信息世界已经由二进制构成了,如果采用高电平,低电平,零电平三种状态表达的三进制或者四种状态表达的四进制计算机,可能计算机技术就会有一个新的发展方向。而实现一个二进制加法器首先需要分析二进制数加法。

而目前计算机只认识0和1,它也只能计算0+0等于0,0+1等于1,1+0等于1,1+1等于0,进位为1。这样可以使用带有前导零的加法表来表示:

+ 0 1

0 00 01

1 01 10

像上表中一对二进制相加有两个数位,右边的叫加法位,左边的叫做进位位,为了更简单一点,将二进制加法表分成两个表,一个是表示加法位的表,一个是表示进位位的表。

+加法 0 1 +进位 0 1

0 0 1 0 0 0

1 1 0 1 0 1

由上面的两个表来看,进位表和上篇文章的与门输出结果是一致的。利用与门我们能设计二进制加法器的进位。

AND 0 1

0 0 0

1 0 1

而加法位的表和上篇文章所介绍的四个基础逻辑门都不一样,但是我们看以看出它和或门以及与非门都有相似之处,我们再来看一下或门和与非门的结果表:

OR 0 1 NAND 0 1

0 0 1 0 1 1

1 1 1 1 1 0

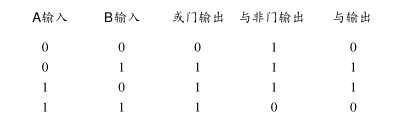

如果将或门和与非门以及一个与门相连接,就可以得到我们想要的加法位表。如下图所示:

上面的电路输入输出结果表为:

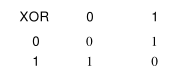

这个输入输出和我们所需要的加法位表一致,这个电路是一个新的逻辑门,叫做“异或门”,简写为XOR,之所以叫做异或门是因为,若想结果为1,要么让A输入为1,要么让B输入为1,如果两个输入同时为1,其结果为0,我们也可以用一个专门的符号来表示这个逻辑门:

异或门的结果表如下:

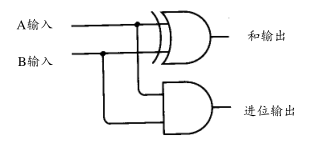

通过上面的分析我们可以知道,二进制数相加的加法位可以由异或门的输出来表达,进位位可以用与门来表达,所以我们可以将与门和异或门连在一起来计算二进制数:

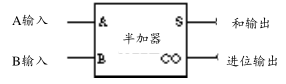

这时我们可以再次抽象一层,将这个电路用下面的符号来表示,这个符号叫做“半加器”(Half Adder):

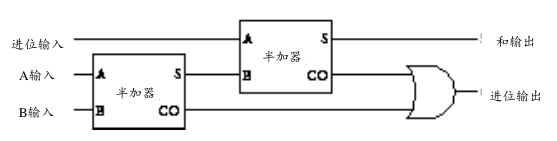

这由一个与门和一个异或门组成的电路之所以叫做半加器,是因为它将两个二进制数相加,得出加法位和进位位,但是并不能将进位位纳入下一次的计算中,所以需要设计一个新的电路来使进位位也参与计算(你大概也忘了小学一年级时做加法时,是不是总忘了加上进位而被老师批评),对于多个二进制数加法运算,可以将两个半加器和一个或门连接在一起:

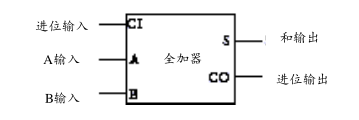

在这个电路中,左边的半加器的加法位还要和它的前一个半加器(并没有画出)的进位在右边的半加器中进行计算,右边的半加器输出的加法位是最终加法位结果,而左边半加器的进位需要和右边半加器的进位进行或运算,其结果为进位输出,这里我们要注意,两个半加器的进位输出最多只能有一个是1,就像我们进行十进制加法时,进位只能进1个数,不能进2个数。这个电路我们可以用一个新符合来表示,这个符号叫做“全加器”(Full Adder):

全加器的输入组合和输出结果如下表所示:

我们使用继电器,通过一层又一层的抽象,设计出来全加器,而我们制作一个8位的二进制加法器需要144个继电器,与门、或门、与非门这四个基础逻辑门都需要两个继电器,因此异或门由6个继电器组成,一个半加器由一个异或门和一个与门组成,就需要8个继电器,而一个全加器由两个半加器和一个或门组成,需要18个继电器。8个全加器组成的8位二进制加法器,需要18*8=144个继电器。

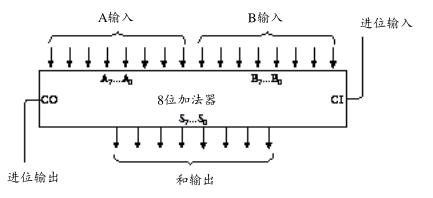

下面是使用8个全加器连接而成的8位二进制加法器:

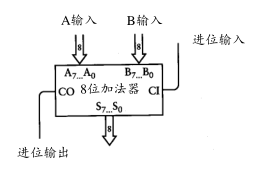

我们再进行一层抽象封装,将这个8位二进制加法器封装到一个盒子里,输入标记为A0~A7和B0~B7,输出标记为:S0~S7,其中A0、B0、S0是最低有效位,A7、B7、S7是最高有效位,如下图所示:

我们也可以用另一种更简单的方式来表示:

你已经搭建出来一个8位二进制加法器,这是可以级联两个8位二进制加法器,扩展出来一个16位加法器:

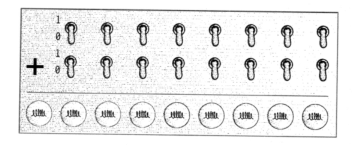

下面是一个使用开关和灯泡组成的8位加法器的控制面板,输入时开关向下为0,开关向上为1;输出时灯泡点亮为1,灯泡不亮为0:

由上面的加法器可以看出,这种电路连接方式制作的加法器,其最低有效位的一对数字相加所得出的一个进位输出,将要参与接下来的加法运算,由此得到的进位输出,又要参与下一对数字的加法运算,加法器的总速度等于数字位数乘以全加器的器件速度,这种叫做行波进位或脉冲进位。更快的加法器运用了一个前置进位的电路来提高运算的速度。

这篇文章中,我们学习了一个新的逻辑门--异或门,以及抽象出来的半加器,全加器,8位二进制加法器等。有了加法器,我们就可以在下一篇文章中通过加法实现减法。