最近的这几篇文章,对有些朋友来说可能有些难以理解,特别是半路转行来当程序员的,因为有前辈们将计算机的世界进行一层又一层抽象和封装,让我们可以选择一门感兴趣的编程语言,掌握这门语言的API,掌握编程思想,选一款好用的IDE,也能很好的完成工作,甚至做出很好的成就,拿到不菲的薪水,但是人类是有好奇心和求知欲的,你就不想知道,你输入的一行行代码,怎么变成机器码0和1,计算机又怎么处理这些0和1吗?特别最近M国对我国进行科技打压,暴露出来我国的计算机基础科学的短板,虽然我们有很多个大型IT公司,但是都是业务驱动型的,芯片研发,操作系统,编程语言,开发工具,数据库系统等等,这类IT公司并没有太知名的。我们拂去心中的浮躁,细细去琢磨这个用继电器来构建计算机的模型,如果能有所得,对真正计算机知识的理解应该大有脾益。

前面我们讲了继电器,以及由继电器构成的四种基础逻辑电路(与门,或门,或非门,与非门),由或门、与非门和与门构成的异或门,然后在向上一级抽象,使用异或门和与门连接成半加器,两个半加器和一个或门连接成一个全加器,8个全加器可以组成8位二进制加法器,再连入8异或门合并而成的求补器,就是一个支持加减法的8位加法器。这时我们这个加法器就支持了加法、减法、乘法(连加)、除法(连减)。而计算机还有一个重要的功能,就是计数。接下来就来设计一个可以计数的电路。

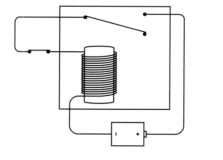

我上小学的时候,学校的铃声是学校的树上吊着一个一米长的铁轨,到时间了就有老师去敲响铁轨,大家都希望老师的手表可以走快一点,可以早点放学。等初中去乡里上学时,因为学校比较大,使用的一电铃,一到时间那铃声就像噪音一样,尖锐、短促、快速,记得当时的地理老师说,听这铃声要少活很多年啊。不过据说他后来混成副校长的时候,把电铃换成了电子合成的音乐声。听过那种电铃的朋友有没有好奇过,为什么那个电铃敲击的那么快?我们先来看下面这个继电器的连线方式:

我们前面的所用电路,都需要人力来控制,通过开关面板,拨动开关,进行一步又一步操作,就算继电器再慢也比人手动操作快的多,所以能够自动运行的电路系统是一个美妙的想法。而上图的电路,是一个连成回路的反相器,当我们闭合开关时,电路导通,电磁铁吸附上面的金属弹片,电路就断开了,然后电磁铁没有电流通过就失去磁力,金属弹片又弹回去,电路又导通,电磁铁又有磁力将上面的金属弹片吸附下来。就这样周而复始,电路自动在连通和断开之间切换,自我驱动。如果将金属弹片前端是一把小锤子,旁边放一个铁盘,这样就构成了一个电铃。其状态图如下所示:

这种电路输出结果要么是0,要么是1,并且不需要人干涉的情况下,可以自发的工作,这种电路称为“振荡器”。振荡器又经常被成为时钟,可以用来计数也可以用来计时。它可以与其他电路组合后形成自动控制系统,使不同组件同步工作。

振荡器从某个初始状态开始,经过一段时间又回到先前的初始状态,这一段间隔定义为振荡器的一个循环或者周期。而周期的倒数就是振荡器的频率,表示每秒钟振荡器产生多少次循环,频率的单位是“赫兹(Hz)”。

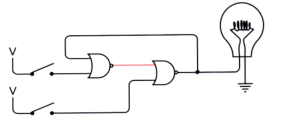

前面我们说过或非门,或非门的特点是,两个输入端都没电压时,输出端才产生电压,下面是用两个或非门连成的特殊电路:

这个电路中,左边或非门的输出,是右边或非门的输入;右边或非门的输出,是左边或非门的输入。这种连接方式叫“反馈(feedback)”。反馈电路的工作原理如下:

通过上面的五个状态,我们可以看出:

1.接通上面的开关,灯泡被点亮,断开此开关,灯泡仍然亮着。

2.接通下面的开关,灯泡被熄灭,断开此开关,灯泡仍然不亮。

这类电路被称为“触发器(Flip-Flop)”,它的特点是可以保持信息,“记住”一位(bit)的信息,如果能记住一位信息,是不是就代表可以记住多个。有记忆功能的电路,是不是代表我们计算多个数据连加时,不用在纸上记下结果,然后再次输入进去,让这个结果参与下次计算,后面我们可以使用一个由触发器组成的电路来记住连加产生的中间结果。让我们快点往下面进行,看看它的魔力吧。

(有时候我们越学习越迷茫,是因为我们接触的知识平面是被人一层又一层抽象完善出来的知识树体系,是为了让我们快速的接收知识,让本来很复杂的东西给抽象成一个简单的定理或者公式,又或者一个方法论,又或者一套API。当我们学习的时候,就觉得勾三股四弦五是理所当然的,我们觉得计算机能够记住很多东西,能够计算,能够播放视频,音乐,能够展示出来一个多姿多彩的网络世界是理所当然的。但是我觉得以软件开发为生的我们,适当的突破这个平面,进入下一个知识体系,了解一些原理,还是挺有必要的,所以才会写这些博文,现在教人编程的博文太多了,经常吃大鱼大肉,适当吃点蔬菜,也挺健康的。)

触发器种类繁多, 上面是最简单的一种触发器,叫做“R-S触发器”。通常用下面的标识符来表示:

其中,R和S是输入端,Q和Q反是输出端,S用来置位,R用来复位,Q和Q反的值总是相反的。就是上面电路的一个抽象,其结论如下:

R-S触发器可以简化为带有输入和输出标志的小框图,如下所示:

R-S触发器的突出特点在于,它可以记住哪个输入端的最终状态为1,但是我们需要记忆能力更强大的电路,例如能记住某个时间点上的一个信号是0还是1。这种功能电路需要存在两个输入,其中一个我们称为数据端(Data),取值为0或者1;另一个输入被称为保持位(Hold That Bit),保持位的作用就是使当前状态被“记住”,通常保持位被设为0,这时数据端对电路不产生影响,当保持位置1时,数据端的值就会在电路系统中被“记住”。随后保持位有置为0,这时电路已经将数据端的最后一次输入记住,而后数据端的输入变化不会对电路产生影响。其真值表如下:

由于当保持位为0时,数据端的输入并不会影响输出,所以我们可以简化这个真值表,用X表示:其取值情况与结果无关。

为了实现上面的真值表逻辑关系,我们需要在R-S触发器电路中增加两个与门。

这个电路中,如果保持位输入为0,那么置位和复位的输入对电路输出没有影响,如果保持位为1,那么置位和复位的输入可以改变电路的输入,和R-S触发器功能一样。如下图所示:

根据上面的真值表,其实我们只想要两个输入,数据端和保持位,那么我们可以分析置位和复位,通过R-S的真值表可以看出,置位和复位都输入0时,是没有意义的,输出保持不变。而都为1时,是非法输入,要避免。真正有意义的是S为0,R为1;或者S为1,R为0。那么我们可以添加一个反向器来优化这个电路,如下图所示:

这个电路叫做电平触发的D型触发器,D表示数据端输入。所谓电平触发就是指当保持位为某一特定电平(上图中为1)时,触发器才保持数据端的输入值。而通常将保持位标记为时钟(clock),并不指真正的时钟,而是它在0和1之间有规律的变化,像时钟的属性。这时我们将数据端简称为D,时钟端简写为Clk,其真值表如下:

通过观察其真值表,这个电路可以称为电平触发的D型锁存器,它表示电路锁住一位数据并保持它,以便将来使用,也可以被称为1位存储器。多个1位存储器连接起来就是多位存储器。我们将8个锁存器的时钟输入端连在一起,这个锁存器就可以一次保存8位数,如下图所示:

我们也可以将8位锁存器的8个数据输入和8个Q输出端画为两组线,如下图所示:

这时,我们还可以对D触发器进行改进,为它添加一个或门和一个清零(Clear)的输入信号。清零信号通常为0,如果它为1时,Q的输出为0,也就是说清零信号能强制使Q输出为0,以达到使触发器清零的目的,如下图所示:

如果我们将8位的锁存器与8位加法器连在一起呢?如下图所示:

上图这个电路,就可以实现连加功能,首先,通过清零开关,将8位锁存器清零,并使加法器B输入的全是0,然后通过A输入8位加数,闭合相加开关。然后加法器将结果存入8位锁存器,并通过B读入到加法器中,又通过A输入新的加数,这样周而复始,实现连加。当然这只是锁存器的一个功能,下面我们看锁存器的另一个功能。

前面我们所设计的D触发器是电平触发的,也就是说时钟端输入为1时,数据端的输入是可以改变的。那么就存在一个问题,计算机内部有多个振荡器协同工作,如果在时钟输入为1时,可能数据端被多次修改,就会造成结果和所期望的不一致。这时电平触发时钟就不适用了,使用边沿触发时钟输入更精准有效。

所谓边沿触发器而言,有且只有时钟从0跳变到1时,才会引起输出的变化。边沿触发的D型触发器是由两级R-S触发器按如下方式连接而成的:

边沿触发器的D型触发器的真值表,需要一个新的符号来表示从0到1的瞬时变化,即用一个向上的箭头表示,如下表所示:

当表中的时钟端输入从0变为1时,Q端的输出与D端的输入相同。边沿触发器的符号如下所示:

边沿触发器的符号与电平触发器的符号的差别在于时钟端输入时,有一个小三角符号。

前面我们说了将一个取反器的输出连到输入,就会构造成振荡器,如果我们将振荡器的输出端边沿触发D型触发器的时钟端输入连接,同时将Q反端输出连接到本身的D输入端,这个触发器的输出同时又是它自己的输入,反馈再反馈。其电路如下:

分析其输入输出,可以得到下面的真值表:

通过上表可以总结:每当时钟输入由0变成1时,Q端输出就会发生变化,或者从0到1,或者从1到0,通过下面的时序图可以更加清晰的说明这个问题:

通过这个时序图可以看出来,Q的输出频率是Clk输入频率的一半,所以这种电路也成为“分频器”,它的Q反输出,反馈到触发器的数据端输入D上。当然,分频器的输出可以作为另一个分频器的Clk输入,并进行下一次分频。如下图所示:

三个分频器电路中的信号变化规律如下所示:

如果将这个图顺时针旋转90度,然后可以得出下面的一个表:

这时,这个电路具备了一个计数功能,如果添加更多的触发器,计数范围就会更大,我们将8个触发器连接在一起,放入一个盒子中,构成一个8位计数器,其可以计数的最大值为11111111(255)。因为每个触发器的输出都是下一个触发器的输入,变化在触发器中一级一级的顺序传递,这种计数器叫做“8位行波计数器”。更先进的是并行计数器,并行计数器的所有输出是同一时间改变的。

随着触发器的功能增加,它的结构也更加复杂,下面设计的是一个带预置和清零功能的边沿型D触发器,通常情况下,预置和清零输入都为0,预置信号为1时,Q变为1。当清零信号为1时,Q变为0。预置和清零信号不能同时为1。其他情况下和普通的边沿D触发器是一样的。其连接方式如下图:

其运行时的输入输出真值表为:

其电路符号如下所示:

通过继电器的一层又一层封装,我们懂得继电器可以用来做加法、减法和计数了。如果不想麻烦的去理解电路,可以直接通过真值表中的输入和输出来了解这些电路能实现的逻辑功能,这样也可以方便理解。