博文目录

写在前面

- 个人博客首页

- 注:学习交流使用!

从初学者对数字设计的疑问?到什么是FPGA?什么是ASIC?在到布尔代数如何在FPGA内部实现?最后到数字设计的核心元件触发器?

本文将从简洁的角度带你认识这些数字设计的必备基础知识!

正文

初学者数字设计

您应该问自己的第一个问题是什么是数字设计师?数字设计师通常是工程师,他们针对FPGA或ASIC编写代码,也称为硬件。 Digital Designer使用两种主要的编程语言:VHDL和Verilog。这种类型的代码与软件根本不同!主要区别在于软件代码以处理器为目标,而硬件代码则不是。

中央处理器(CPU)或仅仅是处理器,是软件设计人员需要了解的中央组件。 CPU一次处理一个指令以执行任务。例如,一条指令可能是将寄存器A的内容添加到寄存器B,然后将结果存储在寄存器C中。软件设计人员使用像C这样的语言编写代码,该代码由编译器进行编译。编译器的工作是获取软件设计人员编写的高级代码,并将其转换为处理器可以理解的低级代码。必须理解,在硬件设计中没有编译器!没有什么可以像使用软件编译器那样将代码带入指令中了。

这是因为Digital Designer没有要定位的处理器。相反,它们具有成千上万的离散数字组件,例如查找表,寄存器,RAM,数字信号处理组件等。我们将在以下文章中逐一介绍这些内容,因为它们非常重要。这些是您的基石!数字设计师所编写的代码比软件工程师要低得多。 Digital Designer面向FPGA的各个组件,并且可以控制一切!

您可能会问自己,为什么CPU如此之快,还要使用硬件设计?这是一个好问题。答案是,CPU适用于大量任务,但不是所有任务。没有数字设计师,将无法实现诸如视频处理,雷达数字信号处理,高速股票交易,高速电信等许多功能。学习数字设计很有趣,因为它是最低级别的编程。您的代码用于字面上在诸如和门和或门之类的组件之间布线!让我们开始您进入数字设计世界的美好旅程!

什么是FPGA? 什么是ASIC?

FPGA代表现场可编程门阵列。 FPGA是可以被认为是可以通过电线连接在一起的大量数字组件(门,查找表,触发器)的组件。您编写的代码与电线建立了真正的物理连接,以执行所需的功能。 FPGA和ASIC之所以与众不同,是因为它们擅长并行(同时)执行大量操作。它们用于高速,高性能任务,例如图像处理,电信,数字信号处理,高频股票市场交易等。

ASIC代表专用集成电路。 ASIC在理论上与FPGA相似,不同之处在于ASIC是作为定制电路制造的。 这意味着-与FPGA不同-它是不可重新编程的,因此您最好在第一时间正确! 由于ASIC是定制电路,因此与FPGA相比,它们的速度非常快且功耗更低。 对于手机,mp3播放器和其他电池供电的设备等对功耗敏感的应用,这可能至关重要。

ASIC的最大缺点是成本。 要让一家公司为您构建ASIC,初期投资将花费数十万美元!

FPGA和ASIC均采用硬件描述语言(HDL)设计。 两种最受欢迎的硬件描述语言是VHDL和Verilog。

数字设计师如何使用布尔代数?

布尔代数是FPGA操作的基础。 布尔代数描述了输入和输出取值为true或false(分别为1或0)的操作。 因此,如果您不擅长微积分,则不必担心,布尔代数是最基本的数学运算! 它是由数学家George Boole于1854年引入的。 利用布尔代数建立的规则,可以创建执行所有基本逻辑运算的基础。 下文将讨论的操作是:AND,OR,NOT,XOR(异或)和NAND。 有了这些数字逻辑的基本构建块,就有可能创建更复杂的操作,例如加法,减法,除法等。但是首先我们必须了解基础知识。

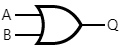

与门

需要理解的第一个概念称为真值表。 真值表是根据输入和输出描述功能的表。 通过查看“与”门的真值表可以最好地证明这一点。

2输入与门表示与门具有2个输入和1个输出。 这些值中的每一个都可以具有值0或1,并且输出值取决于2个输入值。 当两个输入值均为1时,输出仅为1。下面是与门的真值表。

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

或门

或门具有2个输入和1个输出。 当两个输入值中的任意一个为1时,输出均为1。以下是“或”门的真值表。

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

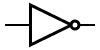

非门

非门表示非门有1个输入和1个输出。 输出与输入值相反。 以下是非门的真值表。

| Input A | Output Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

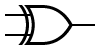

异或门

XOR(异或)门表示XOR(异或)门具有2个输入和1个输出。 当两个输入值不同时,输出为1。 以下是XOR门的真值表。

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

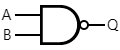

与非门

真值表输出与与门的输出相反。 当两个输入都设置为1时,它仅为0,否则为1。以下是“与非”门的真值表。

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

使用查找表(LUT)在FPGA内部执行布尔代数

上节讨论了布尔代数的基础,即AND,OR,NOT,XOR和NAND门的工作方式。 讨论了真值表的概念。 在此页面中,我们将扩展有关真值表如何工作的主题,并讨论更复杂的布尔代数方程。

首先应该注意,我们前面讨论的所有那些离散逻辑门(AND,OR等)实际上实际上并不存在于FPGA内部! 但是可以执行那些功能。 FPGA能够执行布尔代数的方法是使用查找表(LUT)。 查找表是可以由Digital Designer编程的离散功能块。 LUT使用相同的真值表概念将输出与输入相关联。 让我们尝试一个例子。

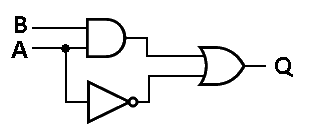

为以下布尔方程式创建一个真值表:Q = A * B + A’。 也许我们应该定义这些符号的含义。

* = AND

+ = OR

' = NOT

^ = NAND

因此,从语言上讲,布尔方程Q = A * B + A’可以读为“输出Q等于A与B或A非”。 让我们看一下真值表和该方程式创建的电路。 从下图可以看出,制作此电路总共需要三个门。

Truth Table - A*B + A’

| Input A | Input B | Output Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

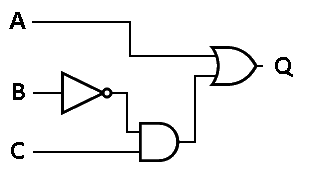

上例中的真值表有两个输入(A和B),这意味着有四种可能的输出可能性。 每个输入将可能的输出数量增加2倍。因此,对于一个输入,有2个输出可能性,对于2个输入,有4个输出可能性,对于3个输入,有8个输出可能性,等等。在数学上,这可以表示为2 ^ (输入的数量)。 现在让我们再看一个具有三个输入的示例。 这是我们要为以下项创建真值表的方程:Q = A +(C * B’)。 注意,圆括号表示操作C AND NOT B发生在OR操作之前。

Truth Table - A + (C*B’)

| Input A | Input B | Input C | Output Q |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

如本文开头所述,FPGA内部实际上并不存在离散逻辑门。相反,FPGA使用查找表或LUT。 LUT由数字设计师编程以执行布尔代数方程,就像我们上面看到的两个一样。如您所料,布尔表达式的所有可能组合都需要能够被编程到查找表中。我将再次以不同的方式说:一个3输入LUT可以使您想到使用3个输入信号的任何布尔代数方程。惊人!

根据所使用的FPGA,LUT的大小可能不同,但它们的行为方式相同。 3输入LUT不久前就已成为标准,但今天4输入甚至5输入LUT都很普遍。如果您需要做出更复杂的表达式,则可以使用更多的查找表。 LUT是FPGA中两个最基本的组件之一。单个FPGA具有数千个这些组件。既然您已经更加熟悉了这些功能强大的通用组件,那么现在该讨论FPGA内部另一个最重要的元素了:

触发器如何在FPGA中工作?

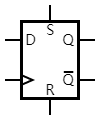

在上一节中,我们讨论了查找表(LUT)组件。 这是FPGA内部两个最重要的组件之一,另一个最重要的组件是触发器。 触发器有几种不同的类型(JK,T,D),但最常用的是D触发器。

请注意,在上图中,设备顶部有一个标记为S的引脚。这被称为置位引脚。 在设备底部,有一个标记为R的引脚。这称为复位引脚。 此外,在设备的右侧,有一个标记为Qbar的引脚。 该引脚将始终包含与引脚Q上的值相反的值。既然您知道这些引脚是什么,那就让我们忽略它们! 它们很重要,但不是本文重点。 触发器上最重要的三个引脚是:

D 数据输入到触发器

Q 触发器的Q数据输出

> 时钟输入到触发器

您可能会问自己的第一个问题是,时钟是什么?

注意,不是这种类型的时钟!

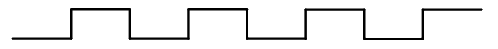

而是这种类型的时钟!

数字时钟是使几乎所有数字电路都可以运行的原因。 考虑系统时钟的一种方法是考虑齿轮组。 为了使系统中的任何齿轮都能转动,必须有一些主齿轮来驱动所有其他齿轮。 这实际上是数字逻辑中时钟的目的。 它提供了电压从低到高到低的稳定过渡流,使您的FPGA能够顺畅运行。 此外,类比很有趣,因为齿轮看上去有点像数字时钟的方波。

时钟是允许触发器用作数据存储元件的时钟。 任何数据存储元素都称为寄存逻辑。 寄存逻辑在时钟的跃迁上运行。 99.9%的时间将是上升沿(时钟从0变为1时)。 当触发器看到时钟的上升沿时,它将数据从输入D寄存到输出Q。触发器使复杂的FPGA成为可能! 让我们看一些事件的波形。

上面的波形显示了三个时钟周期事件,由时钟上升沿上的红色箭头表示。 在时钟的第一和第二上升沿之间,D输入从低到高。 输出Q看到D在第二个时钟周期的上升沿从低变高。 上升沿是当触发器采样输入数据的时刻。 此时,Q变为与输入D相同的值。在第三个上升沿,Q再次采样D的值并将其寄存(这就是为什么触发器通常被称为寄存器)的原因。 由于它没有变化,因此Q保持较高。 我们来看另一个波形。

上图显示了D触发器的输入波形和输出的波形。 D触发器对时钟的上升沿敏感,因此当上升沿出现时,输入D会传递到输出Q。这仅发生在上升沿。在第一个时钟周期,Q看到D已变为1,因此它从0切换到1。在第二个时钟沿,Q再次检查D的值并发现它再次为低,因此变为低。

现在您了解了它们是如何工作的,让我们讨论它们为什么对数字设计如此重要。同样,我提到 触发器 和LUT是FPGA内部两个最重要的组件。触发器(寄存器)如何工作的概念对于成为一名优秀的数字设计师至关重要。这些小家伙无处不在!触发器是FPGA中的主要组件,用于将状态保持在芯片内部。

如果一切都是由LUT组成的,则无法在FPGA中保持状态。这意味着FPGA将不知道以前发生了什么。输入上的所有更改都将立即被评估,并通过一个很长的与门、或门等链发送给输出。但是,为了完成绝大多数任务,FPGA需要了解一些过去的知识。这样,它可以跟踪计数器,状态机和事物的状态。触发器使这成为可能。如果您仍然不太了解这个概念,好吧,这是一种抽象的思维方式。使用硬件描述语言(HDL)的工作越多,触发器在FPGA设计中的重要性就越明显。

参考资料

交个朋友

-

个人微信公众号:FPGA LAB,左下角二维码;

-

知乎:李锐博恩,右下角二维码。