文章目录

嵌入式系统概述

基本概念

嵌入式系统:以应用为中心,以计算机技术为基础、软硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统

嵌入式系统的重要特征:

- 系统内核小:因为系统资源有限,内核不能太大

- 专用性强:针对具体应用场景,做软硬件剪裁

- 系统精简:一般没有系统软件和应用软件之分,全部为应用服务

- 多任务操作系统:要保证程序的实时性、可靠性

- 专用的开发工具和环境:需要主机做开发,程序烧到目标板

嵌入式系统的发展

发展历史

70年代的单片机,51单片机,跑操作系统的单片机,RTOS

发展趋势

- 嵌入式开发称为一项系统工程,除了软硬件本身,还需要开发环境支持

- 网络化、信息化,产品功能不再单一,产品要适应网络发展

- 精简系统内核、算法,降低功耗和成本

- 友好的人机界面

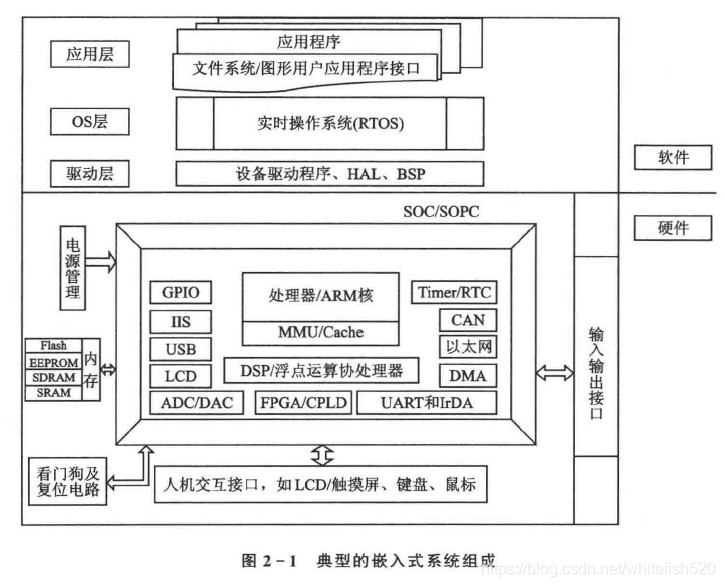

组成结构

一般分4个部分:处理器、存储器、IO、软件

设备驱动层

使用任何外部设备都需要有响应的驱动程序支持,它为上层提供设备的操作接口

驱动层一般包括硬件抽象层HAL、板级支持包BSP、设备驱动程序

硬件抽象层HAL

- 硬件抽象层HAL(hardware abstraction layer)是位于操作系统内核与硬件电路之间的接口层,其目的在于将硬件抽象化

- 这样使得设备驱动程序与硬件设备无关,从而大大提高系统的可移植性

- 抽象层一般应包括相关硬件的初始化、数据的输入/输出操作、硬件设备的配置操作等功能

板级支持包BSP

- 板级支持包BSP(board support package)是介于主板硬件和操作系统中驱动程序之间的一层,一般认为它属于操作系统的一部分,主要是实现对操作系统的支持,为上层的驱动程序提供访问硬件设备寄存器的函数包,使之能够更好地运行于硬件主板

- BSP是相对于OS而言的,不同的OS有不同形式定义的BSP

- BSP实现的功能大体有两个方面:

- 系统启动时,完成硬件的初始化(系统内存、寄存器、中断等)

- 为驱动程序提供访问硬件的函数

设备驱动程序

驱动程序为上层软件提供设备的操作接口,上层软件只需调用驱动提供的接口,而不用理会设备内部的操作

实时操作系统RTOS

OS一般以内核映像的形式下载到目标系统中

OS的应用程序接口API

API(application programming interface)是一系列复杂的函数、消息、结构的结合体

OS中提供的标准API函数,可以加快应用程序的开发,便于移植和升级

应用程序APP

应用程序完成用户自定义的任务,任务之间的协调依赖于系统的消息队列

嵌入式处理器

微处理器

micro processor unit,MPU,由通用计算机中的CPU演化而来

具有体积小、重量轻、成本低、可靠性高的优点

微控制器

microcontroller unit,MCU,典型代表是单片机

和MPU相比,它的特点是单片化,片上外设丰富,适合于做控制

DSP

digital signal processor,DSP处理器专门用于信号处理方面,其系统结构和指令算法方面做了特殊设计,具有很高的编译效率和指令的执行速度,在数字滤波、傅里叶变换、频谱分析等各种仪器上大规模应用

SOC

system on chip,片上系统,追求产品系统最大包容的集成器件,最大的特点是实现了软硬件的无缝结合,直接在处理器片内嵌入操作系统的代码模块,大部分SOC都是专用的

典型嵌入式处理器介绍

MIPS处理器

无内部互锁流水级的处理器(microprocessor without interlockd piped stages),目前使用量仅次于ARM处理器

Power PC处理器

特点是可伸缩性好、方便灵活

Sparc处理器

SUN公司的s系列

ARM处理器

advanced RISC machines(ARM)公司的产品,采用IP授权的方式允许半导体公司生产基于ARM内核的处理器

ARM概述

计算机体系结构的分类

冯洛伊曼结构

- 将数据和指令,存放在一个存储器中

- 这种结构的计算机由一个CPU和一个存储器组成

哈弗结构

- 数据和指令分开存储,有各自独立的存储器

ARM技术的发展过程

略,不同指令集的发展史

ARM内核的特点

RISC技术

CISC:(complex instruction set computer,复杂指令集计算机),随着计算机技术的发展而不断引入新的复杂的指令集,体系结构原来越复杂,部分指令会反复使用,大部分指令不怎么使用,因此结构不合理

RISC:(reduced instruction set computer,精简指令集计算机),选择使用频率最高的简单指令,避免复杂指令,将指令长度固定,指令格式和寻址方式种类减少

流水线技术

简单的三级流水线如下:

- 取指级:完成程序存储器中指令的读取,并放入指令流水线中

- 译码级:对指令进行译码,为下一周期准备数据路径需要的控制信号,这一级指令“占有”译码逻辑,而不“占有”数据路径

- 执行级:指令“占有”数据路径,寄存器堆栈被读取,操作数在桶形移位器重被移位,ALU产生相应的运算结果并写会目的寄存器,ALU结果根据指令需求更改状态寄存器中的条件位

每个时钟周期,某一级流水线完成一条指令

一条指令需要3个时钟周期的执行时间,但是因为有了三级流水线,所以吞吐率(throughput)是每个周期一条指令

超标量技术

通过重复设置多套指令执行部件,同时处理并完成多条指令,实现并行操作来达到提高处理速度的目的

在一个时钟周期内,同时执行多条指令,因此CPU的效率大大提高

基于ARM的微处理器

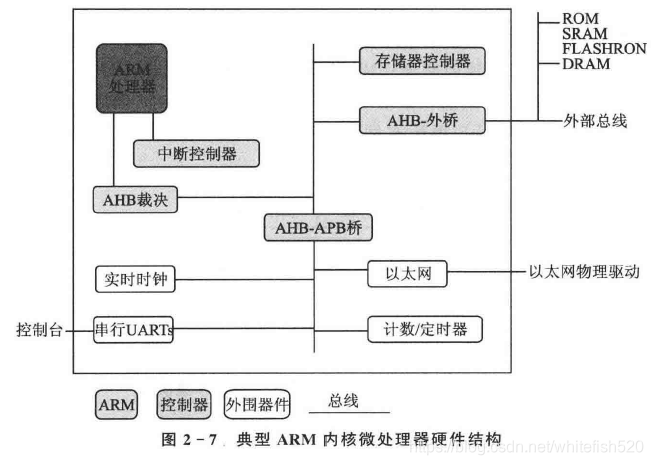

基于ARM核的硬件结构

各大厂商从ARM公司买其设计的ARM微处理器核,根据不同的应用,加入适当的外围电路,形成自己的ARM微处理器芯片

这个器件可以分为4个部分

- ARM处理器:控制整个器件,包含内核、外围部件

- 控制器:协调系统的重要功能模块,最常见的是中断控制器和存储器控制器

- 外设接口部件:提供芯片与外部的输入输出

- 总线:用在器件不同部件之间进行通信,包含高性能总线AHB,连接高性能的片内外设,外设总线APB连接较慢的片内外设,还有一条总线用于连接片外外设,它需要一个特殊的桥,用于和AHB总线连接

ARM核的数据流模型

load指令,存储器 -> 寄存器

store指令,寄存器 -> 存储器

典型的源寄存器Rn、Rm,目的寄存器Rd

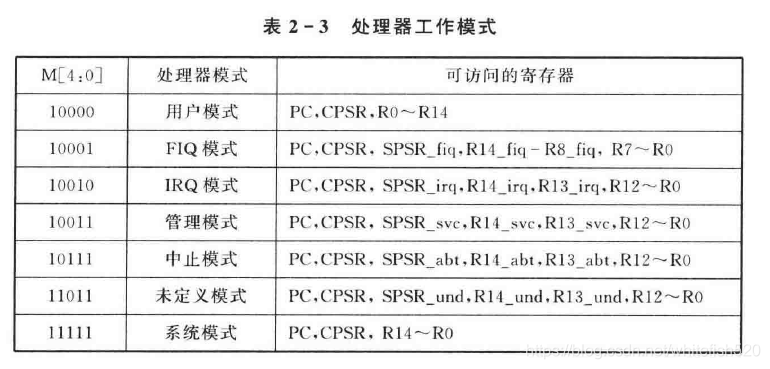

工作模式

- 用户模式(usr):正常的程序执行状态

- 快速中断模式(fiq):用于高速数据传输或通道处理

- 外部中断模式(irq):用于通用的中断处理

- 管理模式(svc):操作系统使用的保护模式

- 终止模式(abt):当数据或指令预取终止时进入该模式,用于虚拟存储及存储保护

- 未定义指令模式(und):当未定义的指令执行时进入该模式,用于支持硬件协处理器的软件仿真

- 系统模式(sys):运行具有特权的操作系统任务

除用户模式和系统模式,其余5种称为异常模式,常用语处理中断异常或访问受保护的资源

工作状态

ARM状态:执行32位的ARM指令集

Thumb状态:执行16位的Thumb指令集

在开始执行时,只能是ARM状态,执行过程中,可与切换

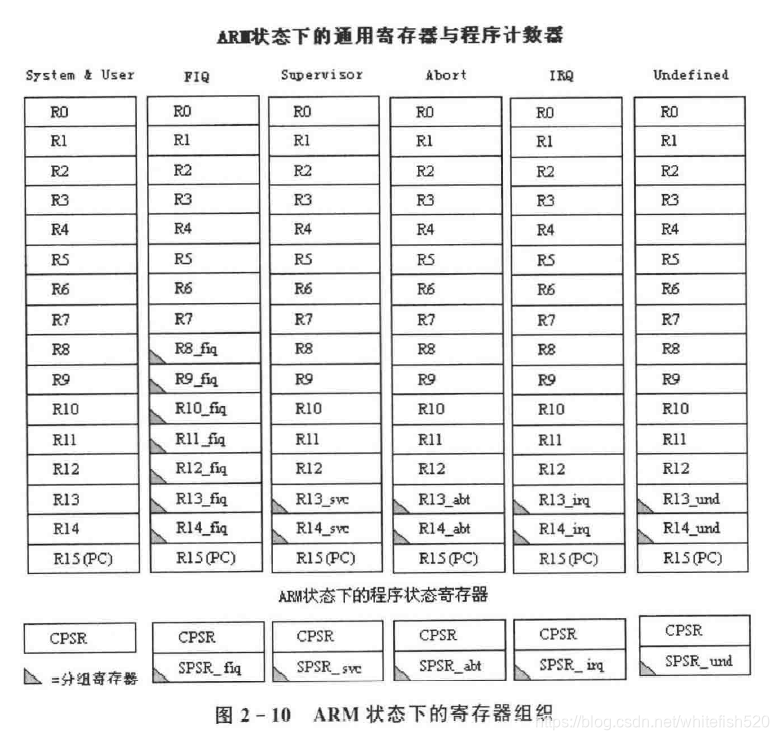

ARM寄存器

- 分为通用寄存器和状态寄存器,一共37个

- 通用寄存器保存数据和地址,有31个

- 状态寄存器用以标识或设置处理器的工作模式、状态,有6个

- 这37个寄存器不能被同时访问,最多有18个活动的寄存器,16个数据寄存器,2个处理器状态寄存器

通用寄存器

用以保存数据和地址,用字母R为前缀,加该寄存器的序号来标识

例如寄存器0,标识为R0,范围是R0-R15

可以分为三类

未分组寄存器

包括R0 - R7,在所有工作模式下,未分组寄存器都指向同一个物理寄存器

在中断或异常处理时,因为使用相同的物理寄存器,可能造成数据破坏

分组寄存器

包括R8 - R14,它们每一次访问的物理寄存器与当前的工作模式有关

采用标记来区分不同的物理寄存器,如 R13

R13一般用作堆栈指针

R14称作子程序连接寄存器(subroutine link register)或连接寄存器LR

当执行BL子程序调用指令时,R14中得到R15(程序计数器PC)的备份

程序计数器

R15用作程序计数器(PC),用于控制程序中指令的执行顺序

正常情况下,PC指向CPU运行的下一条指令,每次执行后,PC的值会自动修改

当程序执行顺序改变,则PC也需要改变

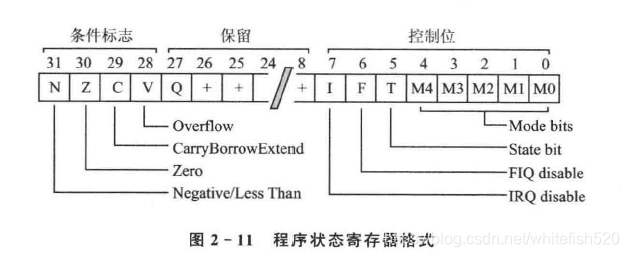

状态寄存器

包含一个当前程序状态寄存器CPSR,和5个备份的程序状态寄存器SPSRs

CSPR可以在任何工作模式下被访问,用来保存ALU中的当前操作信息、允许/禁止中断、设置处理器的工作模式

备份寄存器用来进行异常处理

条件码标志

N Z C V 均为条件码标志位,他们的内容可以被算术或逻辑运算的结果改变,并且可以决定某条指令是否被执行

- N:Negative,正负标志位,N=1结果为负数,N=1结果为非负数

- Z:Zero,零标志,Z=1结果为0,Z=0结果非零

- C:CarryBorrow,进位、借位标志,加法C=1进位,减法C=0借位

- V:Overflow,V=1溢出,V=0未溢出

控制位

CPSR 的低8位(I,F,T,M[4:0])称为控制位,当发生异常时,这些位可以被改变

中断禁止位

包括I、F,用来禁止或允许IRQ和FIQ两类中断

- I :I=1表示禁止IRQ中断

- F :F=1表示禁止FIQ中断

T标志位

T标志位用来标识/设置处理器的工作状态

对于ARM体系结构v4及以上版本的T系列处理器,该位为1时,程序运行于Thumb状态,该位为0时,运行于ARM状态

ARM指令集和Thumb指令集均有切换处理器状态的指令,可以修改T位

工作模式位

M [4:0] 用来标识或设置处理器的工作模式,常用的是系统模式和用户模式

注意,不能使用无效的模式,否则不可恢复

保留位

不要使用保留位保存数据

每一种工作模式下,有一个专门的物理状态寄存器,称为SPSR(saved program status register)

当发生异常时,SPSR保存CPSR的值,恢复时,用来恢复CPSR

用户模式和系统模式不属于异常模式,没有SPSR

Thumb寄存器

Thumb状态下的寄存器集,是ARM状态下寄存器集的一个子集,程序可以直接访问8个通用寄存器(R0~R7)、程序计数器(PC)、堆栈指针(SP)、连接寄存器(LR)、状态寄存器(CPSR),同时,在每一种特权模式下都有一组SP、LR、SPSR

Thumb状态下的寄存器组织与ARM状态下的寄存器组织的关系

- Thumb状态下和ARM状态下的R0-R7是相同的

- Thumb状态下和ARM状态下的CPSR和所有的SPSR是相同的

- Thumb状态下的SP对应于ARM状态下的R13

- Thumb状态下的LR对应于ARM状态下的R14

- Thumb状态下的PC对应于ARM状态下的R15

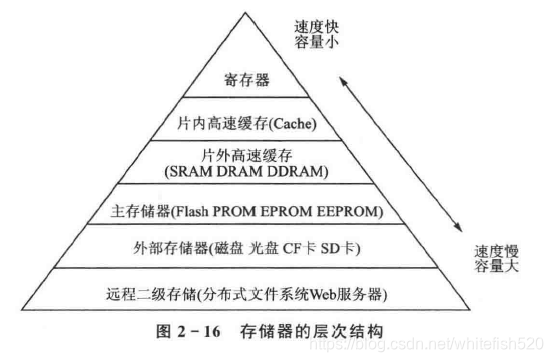

ARM的存储系统简介

存储器Memory是计算机用来存放二进制数据和程序的部件

一般分为RAM和ROM

- 随机存取存储器:RAM(random access memory)

- 静态随机存储器:SRAM

- 动态随机存储器:DRAM

- 双倍速率随机存储器:DDRAM

- 只读存储器:ROM(read only memory)

掩膜ROM、PROM、EPROM、EEPROM、Flash memory

存储器的层次结构

一般情况下,基于ARM的嵌入式系统用到的芯片如下

- ROM:只读存储器,一般情况不再次编程,一般用来放启动代码

- Flash:可读可写,但是速度较慢,因此不适合动态数据,一般用来存放断电后需要保存的数据

- DRAM:在RAM里价格低,但是动态刷新,因此使用前要先设置好DRAM控制器

- SRAM:比DRAM快,而且不需要刷新,价格高容量小,一般用于高速存储器和cache

- SDRAM:使用时钟,频率与CPU总线同步,传输效率较高

数据类型与存储器格式

地址空间

ARM体系结构将存储器看作是零地址开始字节的线性组合

32位处理器支持的最大寻址空间为4gb

每执行一条ARM指令,PC增加4,执行一条Thumb指令,PC增加2

数据类型

ARM处理器的指令长度是32位(ARM指令),也可以是16位(Thumb指令)

支持8位、16位、32位数据

存储格式

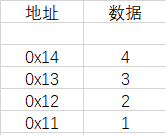

大端格式

数据的高字节存储在低地址中,低字节存储在高地址中

例如:0x1234,在如下的地址存放

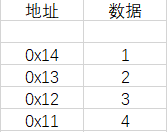

小端格式

与大端模式相反,数据的高字节存储在高地址中,低字节存储在低地址中

ARM处理器可以配置为任意一种模式,但是小端模式是默认格式

例如:0x1234,在如下地址存放

非对齐的存储器访问

所谓非对齐的存储访问操作,是指:

- 位于ARM状态期间,访问地址的低二位不为00

- 位于Thumb期间,访问地址的最低位不为0

非对齐的指令预取操作和数据访问操作的约定如下

非对齐指令预取操作

如果写入寄存器PC的值是非对齐的,要么执行结果不可预知,要么地址中响应的位被忽略

是否要忽略,由系统决定

非对齐数据访问操作

对于laod/store操作,如果出现非对齐的数据访问操作,有两种可能

- 执行结果不可预知

- 忽略数据地址的低2位或者最后一位