- 引脚说明

- 基本结构

- 工作方式

- 相关寄存器

**

一、引脚说明(以正点原子精英版所用stm32f103zet6为例)

**

STM32F103ZET6:

- 一共有7组IO口——GPIOA~GPIOG

- 每组IO口有16个IO——PA0~PA15…PG0~PG15

- 一共有7X16=112个IO口

这是一个ZET6芯片IO口的数量位置分布,在不同的芯片IO口数量也不同

**

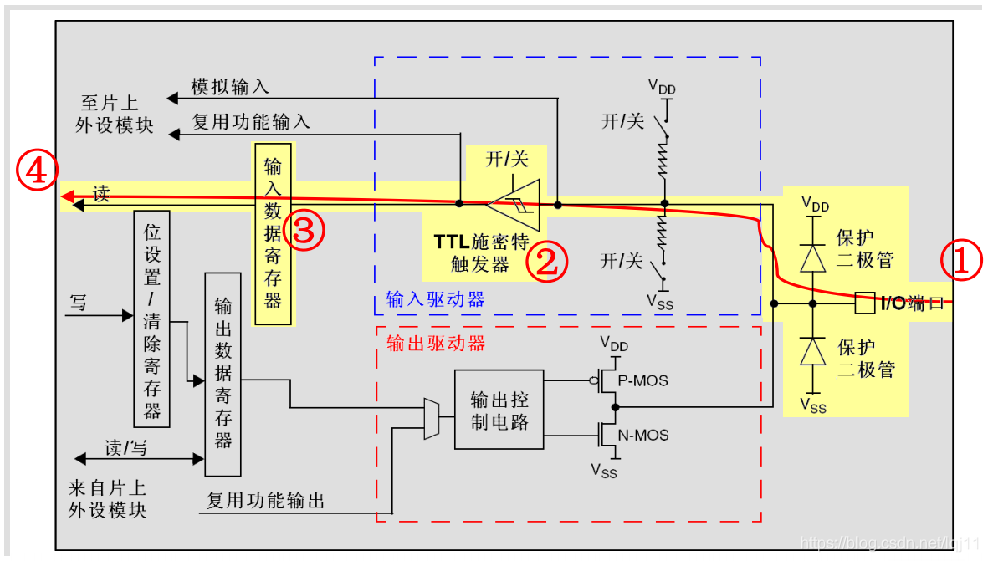

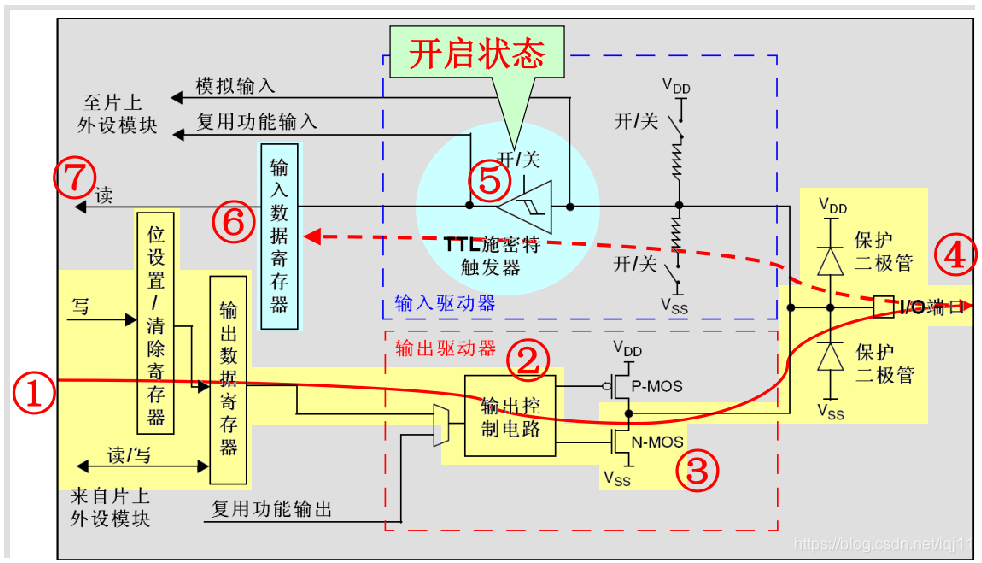

二、基本结构

**

先把这张图放在这里

**

三、工作方式

**

输入模式4种:

- 输入浮空

- 输入上拉

- 输入下拉

- 模拟输入

输出模式4种:

- 开漏输出

- 开漏复用功能

- 推挽式输出

- 推挽式复用功能

输入浮空模式:

IO端口的状态传到施密特触发器,经过施密特触发器处理进入输入数据寄存器,由CPU读取输入数据寄存器得到这个引脚的状态。

需要注意的是:在输入浮空下引脚的状态仅有外部所加的电平有关,具有不确定性。

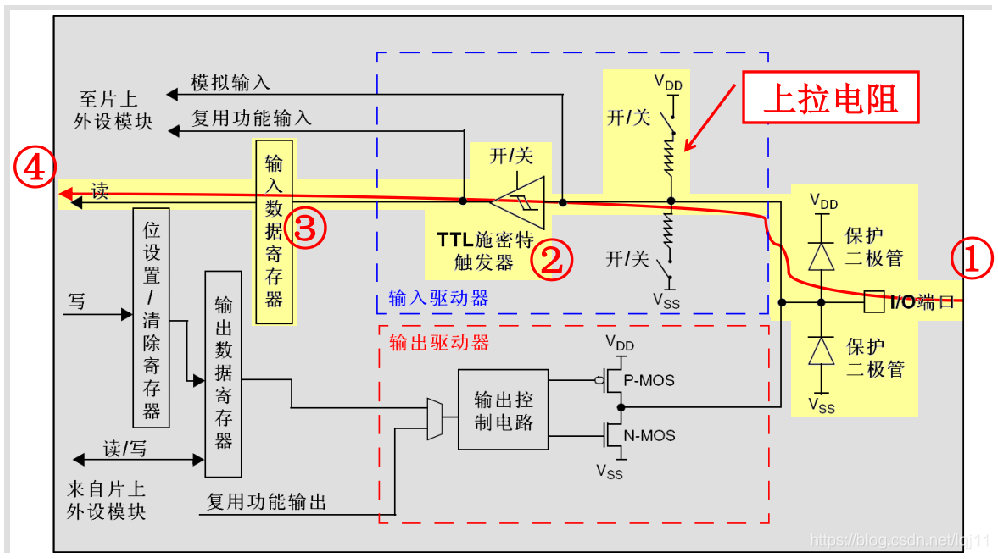

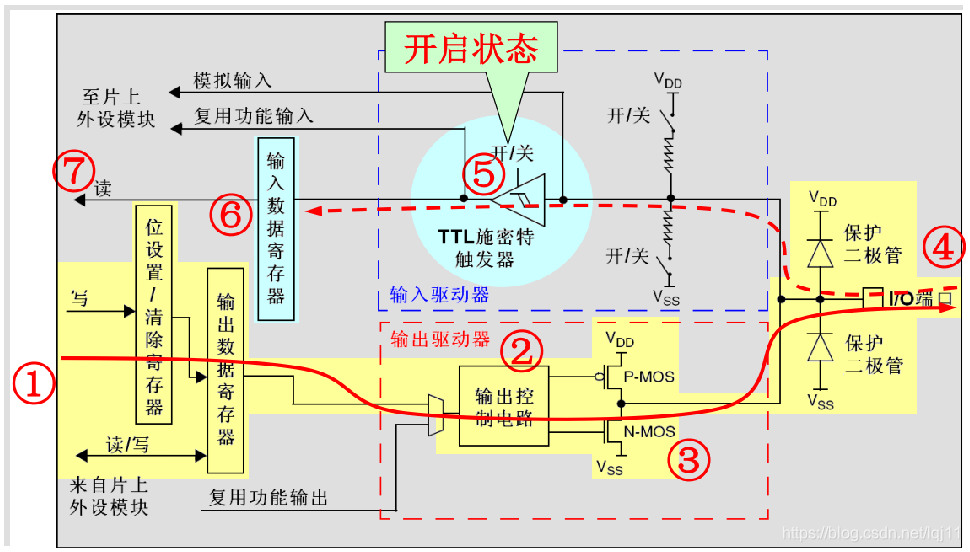

输入上拉模式:

相当于在浮空输入的基础上加了一个上拉电阻,因为在浮空输入模式且未加外部电压的情况下下IO口的电平状态是不确定的,加上拉电阻,就把不确定的电平钳制在了高电平,所以在上拉输入模式下,默认IO口的状态为高电平。

输入下拉模式:

与上拉模式唯一的不同是输入下拉模式中加的是下拉电阻,将不确定的状态钳制在了低电平。

输入上拉与输入下拉模式一个最常见的应用就是在读取按键状态上。如果按键是低电平有效,那么需要接上拉电阻,默认状态就是高电平,只有在按键被按下的时候才是低电平的有效状态,松开立刻回到高电平状态。

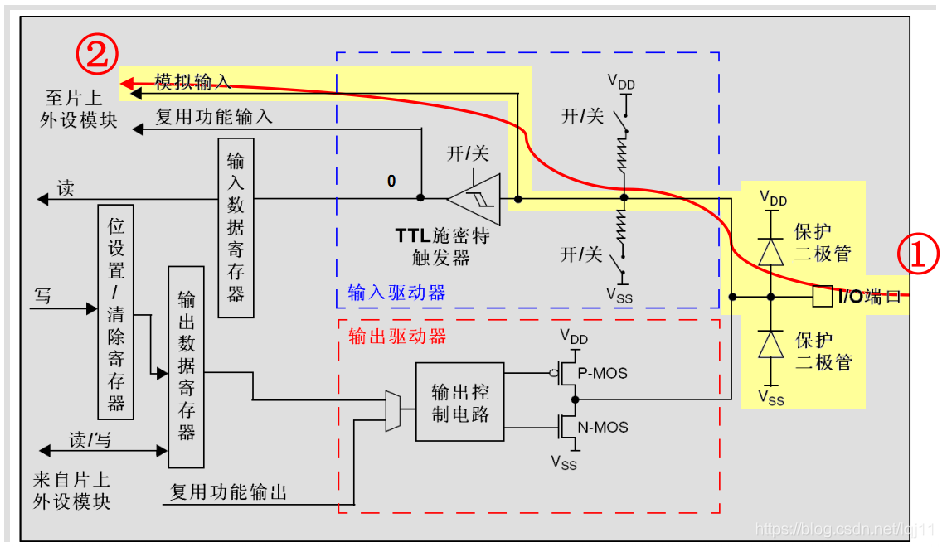

模拟输入模式:

将外部读取到的模拟信号传入到外设模块AD/DA上完成模数转换。

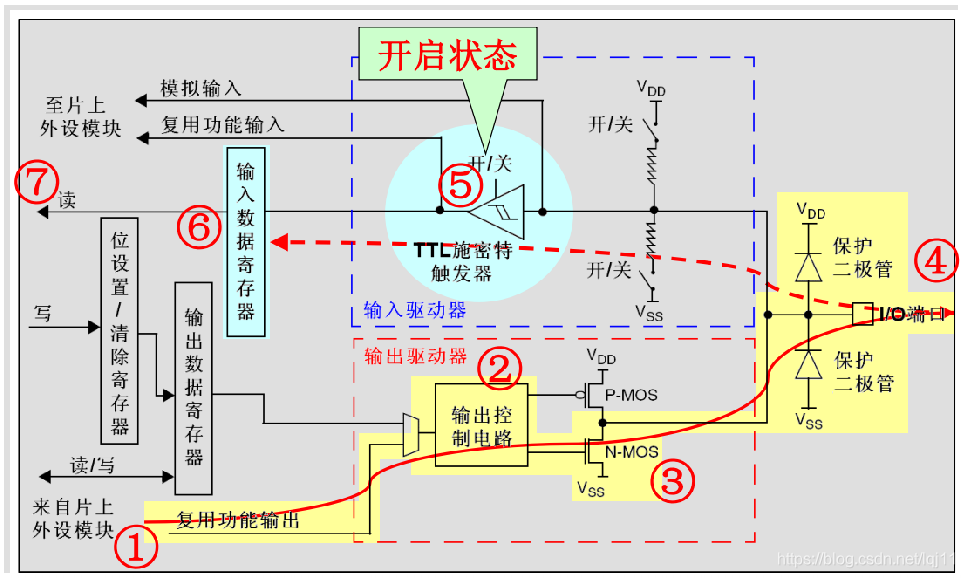

开漏输出模式:

当CPU写入一个电平值时,经过前两个寄存器到达输出控制电路,写入高电平1时,M-MOS管截止,IO口状态不由写入的值决定,仅有外部上下拉电阻决定,写入低电平0时,N-MOS管导通,整条线路被拉低到VSS,IO口输出低电平。

总的来说,在开漏输出下,写高无效,写低有效。

开漏复用输出模式:

与开漏输出唯一的区别在于控制信号的来源不同,开漏输出的来源是内部CPU,而开漏复用的来源来自外设模块。

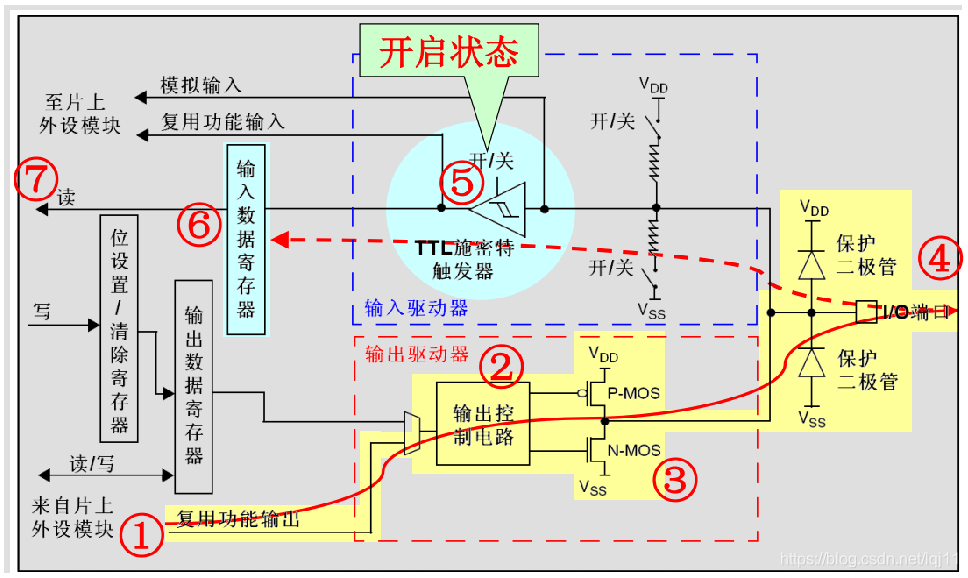

推挽输出模式:

与开漏输出类似,当写入高电平1时,P-MOS管导通,N-MOS管截止,整条线路就处在VDD高电平,IO口输出高电平。当写入低电平0时,P-MOS管截止,N-MOS管导通,整条线路被拉低到VSS,IO口输出低电平。

推挽输出输出强高低电平。

推挽复用输出:

和开漏与开漏复用的对比类似,也是来源与推挽输出不同。

**

四、相关寄存器

**

每组IO口由7个寄存器控制,它们是:

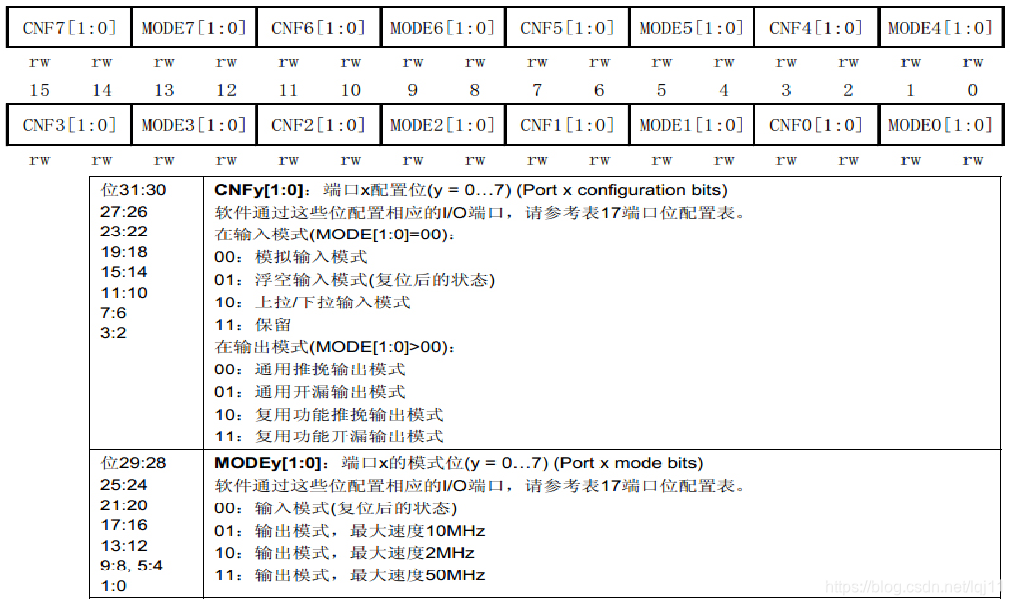

两个32位配置寄存器(GPIOx_CRL ,GPIOx_CRH)

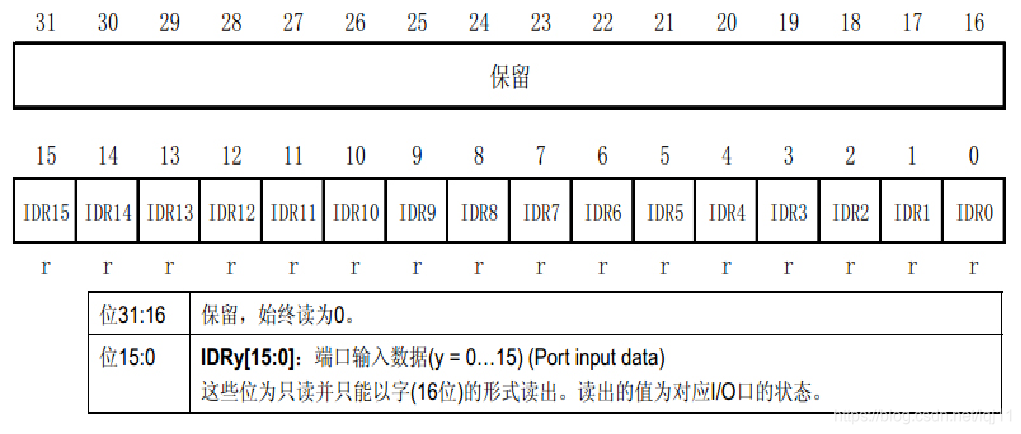

两个32位数据寄存器 (GPIOx_IDR和GPIOx_ODR)

一个32位置位/ 复位寄存器(GPIOx_BSRR)

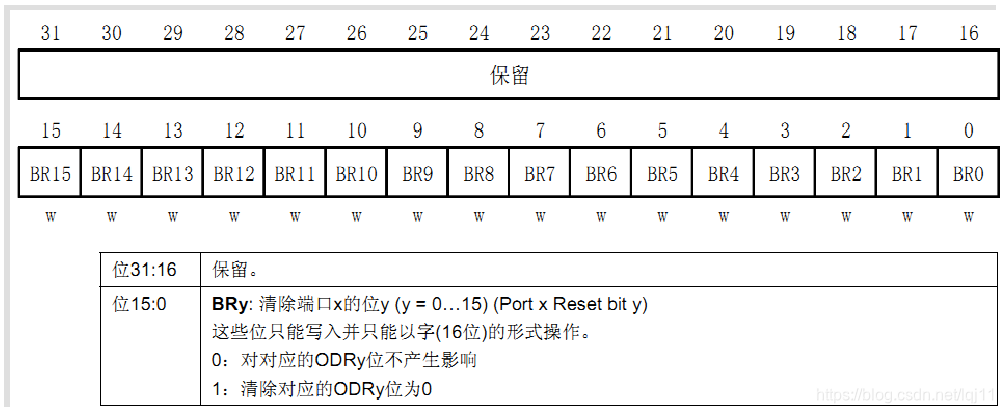

一个16位复位寄存器(GPIOx_BRR)

一个32位锁定寄存器(GPIOx_LCKR)

GPIOx_CRL :端口配置低寄存器

GPIOx_CRH:端口配置高寄存器

GPIOx_IDR:端口输入寄存器

GPIOx_ODR:端口输出寄存器

GPIOx_BSRR:端口位设置/清除寄存器

GPIOx_BRR :端口位清除寄存器