《FPGA并行编程》读书笔记(第一期)01_HLS简介

注:虽然大家都知道一些基础内容,但为了照顾小白,我还是按照步骤都简要介绍一遍,供需要的人查阅。

1. HLS是什么

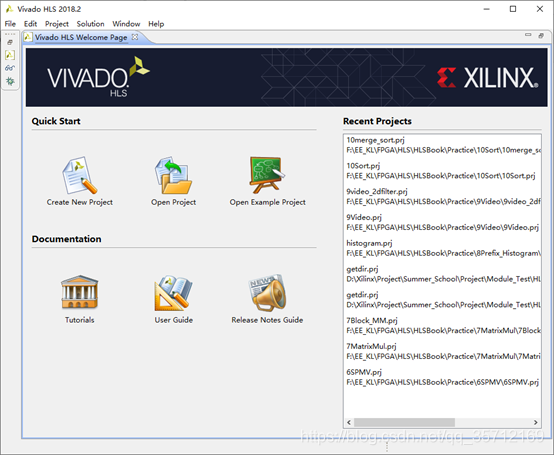

HLS是High-level Synthesis(高层次综合)的缩写,是Xilinx公司Vivado套件的一个组件,可以将优化过的C,C++ 以及 System C转换成RTL代码的软件。下图即是HLS的软件初始界面:

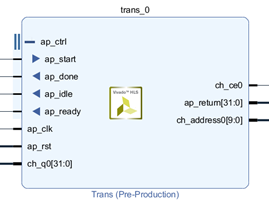

在Vivado中通常以IP的形式被调用:

关于HLS的具体内容,还是见《FPGA并行编程》中的第一章绪论吧,我就不在这里班门弄斧了。

2. HLS入门Demo扫疑

2.1 HLS入门Demo简介

为了使大家对HLS各个优化策略有个概念性的认识,推荐大家把我下面链接中的4个Lab练习下(该Lab应该是来源于官方的大学计划培训内容)

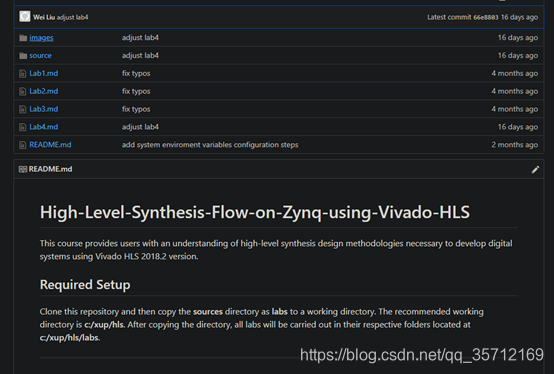

High-Level-Synthesis-Flow-on-Zynq-using-Vivado-HLS

小编曾在2019Xilinx国际暑期学校做过,质量上乘,通过4个Demo大家就可以对HLS有个浅显的认识,为大家打下全局观,方便后面《FPGA并行编程》的理解。

这里给大家分享个我参加的2019XIlinx暑期学校全记录,对FPGA开发感兴趣的童鞋可以看下,每年都会举办

下面是部分记录截图

看下面的教程截图是不是非常高大上,我只是教程的搬运工,大家好好享受这专业的教程吧。大家按情况做实验,如果没有PYNQ板子可以仅做(Lab1、Lab2、Lab3),让大家看这个教程的目的是对HLS有个初步的了解,看不懂没关系。下面来具体说明该实验几个要注意的地方。(提醒下大家,如果后期该教程修改的话,可能不会出现下面的Bug,所以仅供参考)4个Lab大约花费4个小时完成,要想有比较深的理解,需要花费额外4个小时。

2.2 .md文件阅读器

Typora下载链接 提取码:6k80

Typora用于读取.md文件。大家也可自行Google查找下载自己喜欢的阅读器。

2.3 Lab1-Vivado HLS Design Flow Lab

完成本Lab后,您将能够:

- 在GUI模式下使用Vivado HLS创建新项目

- 仿真设计-Simulate a design

- 综合设计-Synthesize a design

- 实现设计-Implement a design

- 使用Vivado HLS的分析功能执行设计分析

- 使用Vivado和XSim仿真器分析仿真结果输出

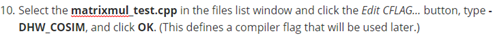

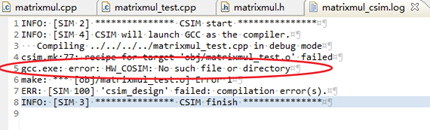

第一个大坑——CFlAGS

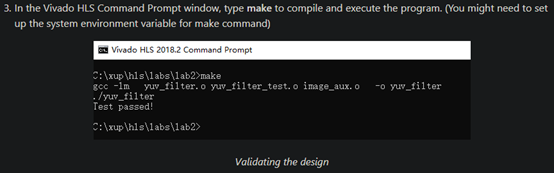

下图是该坑的来源截图

不要执行这项操作,否则会报错,报错截图为

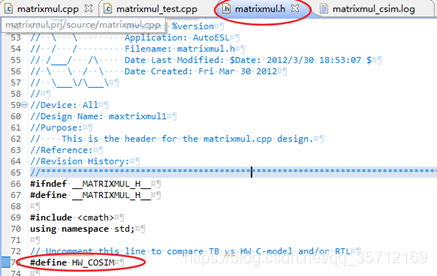

修改方案为执行下图操作,直接在.h文件加入HW_COSIM

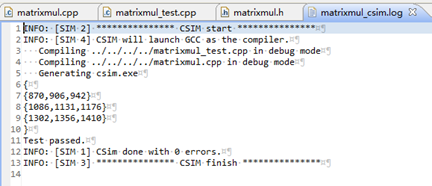

成功完成Run C Simulation,执行结果为

这个错误不清楚是啥导致的,Google后也没有找到合适的解决方案,如果大家有思路,欢迎在评论区留言。

2.4 Lab2-Improving Performance Lab

完成本实验后,您将能够:

- 在设计中添加指令-Add directives in your design

- 了解INLINE指令的效果

- 使用PIPELINE指令提高性能

- 区分DATAFLOW指令和配置命令功能

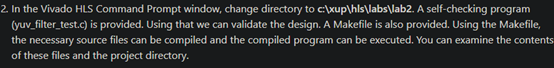

第二个大坑——改变目录

拿小编的例子来说明一下这个误人子弟的神操作,首先说该错误源自下图

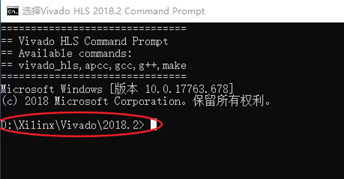

按照第一步骤打开命令行如下图所示

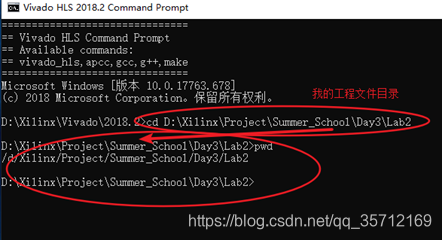

此时要注意了,我的Vivado HLS安装目录为D盘 ,可以从上面命令行的初始路径可以看出,这里建议工程文件夹也放在D盘这样进行如下操作即可进入工程文件所在目录。

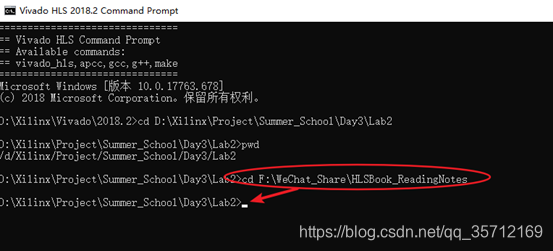

假如你的工程文件目录在F盘,那么仍然执行上面的操作,将会出现如下的问题——没有转到正确的目录!

具体原因详见这个博主的博客:Windows 命令行切换目录

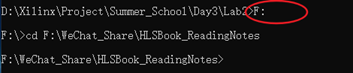

如果你一定要将工程目录与软件初始路径不在一个分区内,此时只要先执行下面的操作就要可以完成目标了。

还有如果这一步执行不成功还有其他原因:中文路径、路径中有空格等因素。在这里强调下,文件夹命名最好不要有中文、特殊字符、空格。

一个小坑——执行结果不一样

教程中的结果如下图,可是你的结果出现一堆不知所以的字符,在这里说明下,这个并不影响结果,只要出现Test passed即可,具体出现上述异常的原因,我这里也不便说明,因为我也不是很明白。

2.5 Lab3-Improving Area and Resource Utilization Lab

完成本实验后,您将能够:

- 在设计中添加directives

- 使用PIPELINE指令提高性能

- 区分DATAFLOW指令和配置命令功能

- 应用memory partitions以提高资源利用率

- 本实验没有坑,有坑也是在前面已经说明了。

3. 小试牛刀

大家经过第2节4个Lab的洗礼,再去阅读《FPGA并行编程》是不是就非常简单了。现在来进行小小的实战吧!

第一章节HLS简介的练习代码:PP4FPGAS_Study_Notes_S1C01_HLS_Introduction

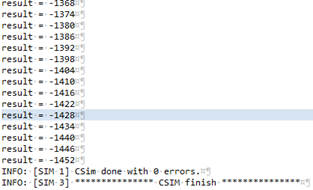

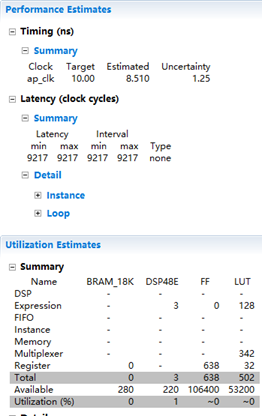

像前面几个Lab一样新建工程,观察输出结果是否是如下截图。

C仿真结果:

C综合结果:

如果大家执行出如上结果,说明已经掌握了HLS的基本操作了。

统一一下,大家芯片选择xc7z020clg400-1,这是PYNQ板卡的板载ZYNQ芯片。

注:该代码是在英文原版书籍给出代码的基础上修改而来的,原版代码可能因为版本的迭代,不能正常执行。

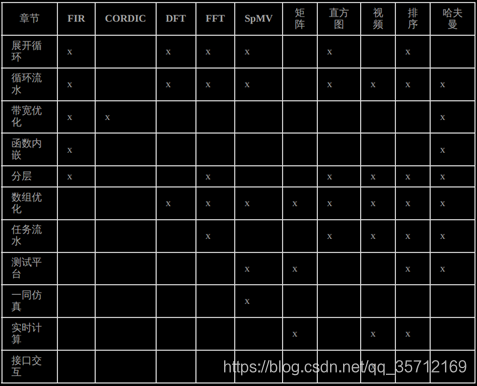

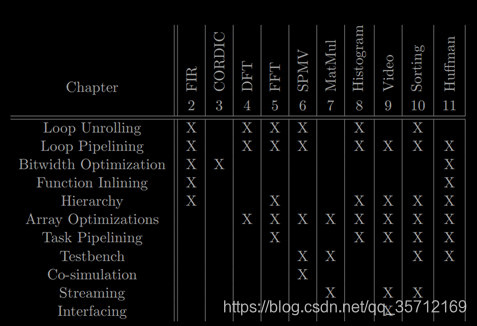

4. 各章节内容知识点

5. 章节总结

这个章节的内容还是比较多的,在不出意外的情况下完成我给大家推荐的4个Lab,再阅读完《FPGA并行编程》第一章HLS简介,预估需要6个小时的时间,要想有更深的理解,需要花费更多时间来消化。

另外大家对前面发布的两个推送有什么建议,内容安排、语言组织、排版润色等方面,因为我是第一次以博客文章来分享自己的读书笔记,诸多不足还望见谅。

最后再强调下,本文不是专业人士所写,仅仅是一个在FPGA道路上慢慢探索的小白,分享出来自己在阅读中遇到的困难以及其解决方案,如有错误还望批评指正。

欢迎大家关注我刚创建的微信公众号——小白仓库

原创经验资料分享:包含但不仅限于FPGA、ARM、Linux、LabVIEW等软硬件开发。目的是建立一个平台记录学习过的知识,并分享出来自认为有用的与感兴趣的道友相互交流进步。

最后要提的是,本文很多资料都是Xilinx大学计划提供,该公众号提供很多的权威信息、开源项目、开发板租借,强烈推荐对FPGA感兴趣的道友关注——XIlinx学术合作。

注:个人精力能力有限,欢迎批评指正!