第十章 I2C接口

)

第十章 I2C接口

I2C 接口简介

I2C模块提供了一个在DSP芯片和I2C总线器件之间的接口,具有下列性能:

- 支持字节格式的传输

- 7位和10位的寻址模式

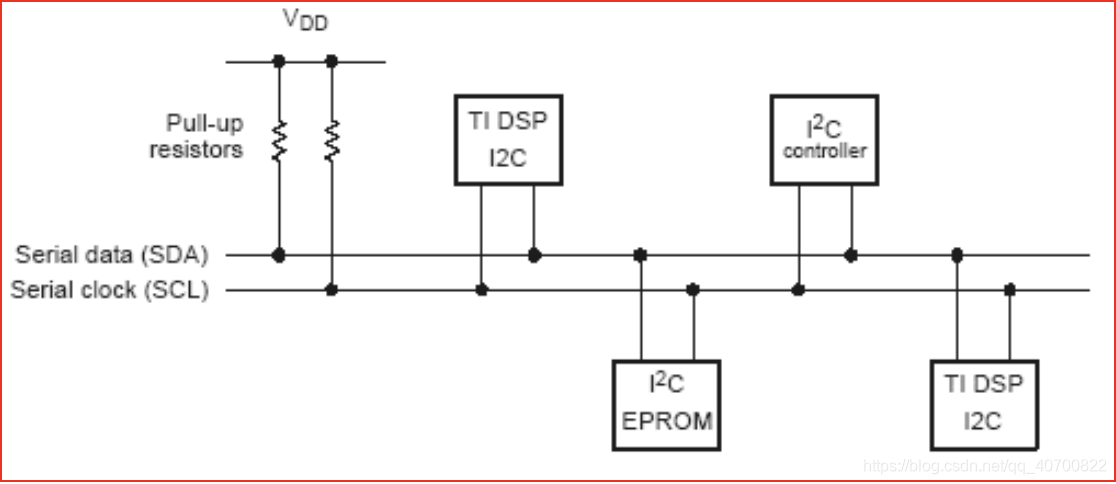

- 支持多个主-发送器和从-接收器

- 支持多个从-发送器和主-接收器

- 组合的主发送/接收和接收/发送模式(仅在7位寻址模式中)

- 数据传输速率从10 kbps一直到400 kbps (Philips快速模式速率)

I2C 模块结构

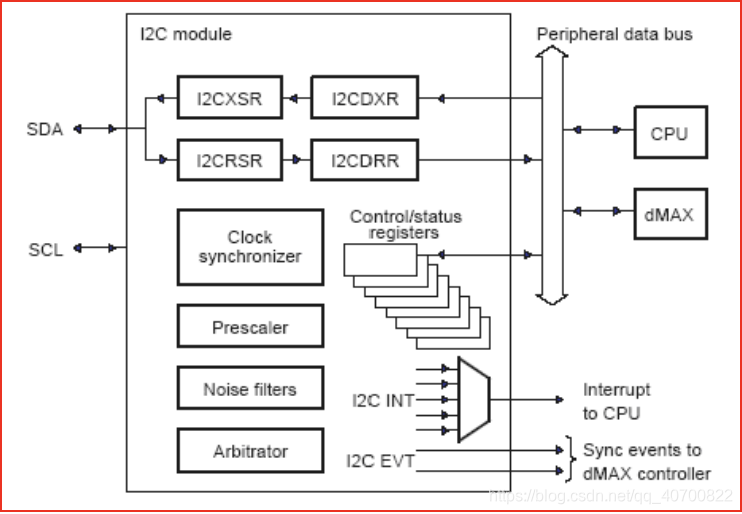

2C模块包括下列的基本部分:

- 串行接口:一个数据引脚(SDA)和一个时钟引脚(SCL)

- 数据寄存器:用来临时保存在SDA引脚和CPU或DMA控制器之间流通的接收数据和发送数据

控制和状态寄存器:

- 一个外围数据总线接口:用来使能CPU和dMAX控制器来访问I2C模块寄存器

- 一个时钟同步器:用来将I2C输入时钟(来自DSP时钟产生器的SYSCLK2)和SCL引脚上的时钟同步,以及用来将数据传输跟具有不同时钟速度的主机同步

- 一个预定标器:用来将驱动到I2C模块的输入时钟(SYSCLK2)分频

- 一个仲裁器:用来处理I2C 模块(在它是主机时)和其他主机之间的仲裁的

- 中断产生逻辑:向CPU发送中断

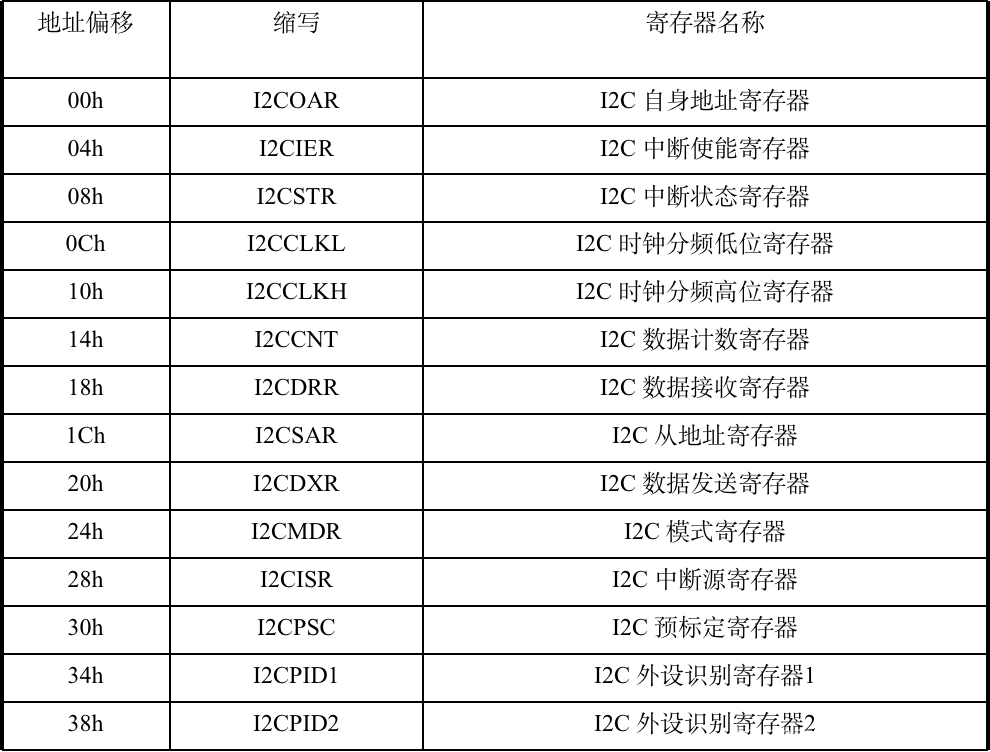

I2C寄存器

I2C模块寄存器

I2C 操作模式

- 若I2C模块为主模块,那么开始它一般作为主发送器向某一从模块发送一个地址。在将数据发给从模块时,I2C模块必须保持为一个主发送器。为了从一个从模块接收数据,必须将I2C模块变换成主接收器模式。

- 若I2C模块为从模块,那么开始它一般作为从接收器,并且在它识别出主模块发来的从地址时发出确认信息。如果主模块要向I2C模块发送数据,这时I2C模块必须保持为一个从接收器。如果主发送器向I2C模块发出数据请求,I2C模块必须要变换成从发送器模式。

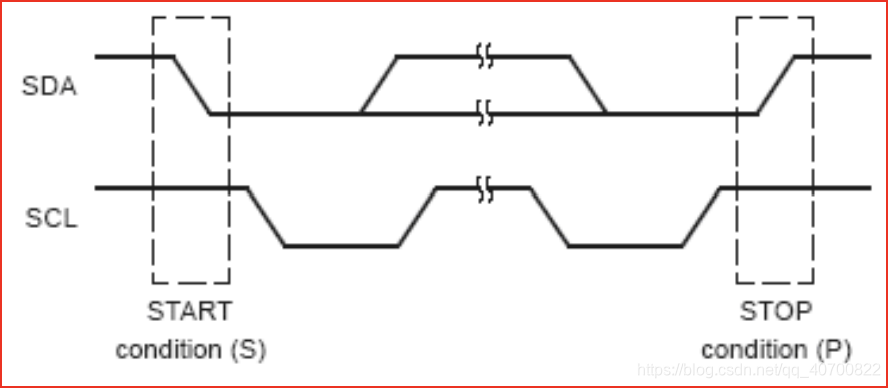

I2C 开始和停止状态

- START状态定义为当SCL为高时,SDA线上从高到低的转变。主模块驱动这一状态是用来指示出数据传输的开始。

- STOP状态定义为当SCL为高时,SDA线上从低到高的转变。主模块驱动这一状态是用来指示出数据传输的结束。

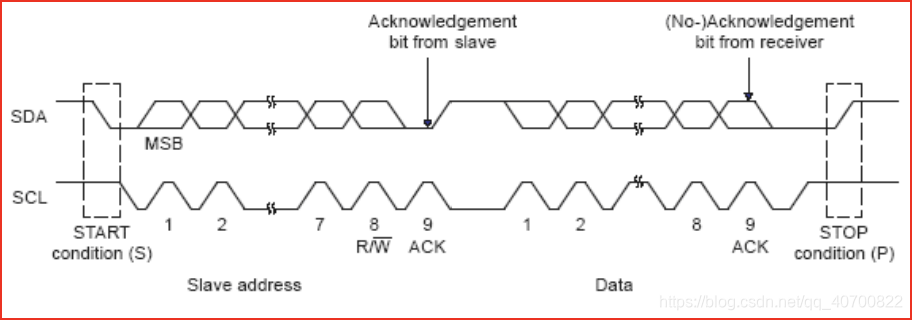

I2C 串行数据格式

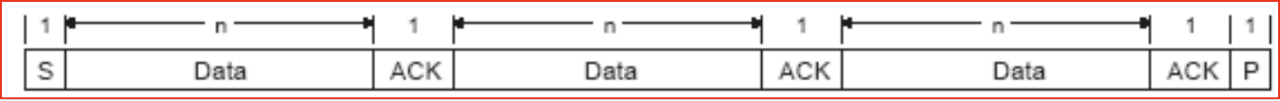

I2C模块支持1到8位的数据长度。下图中给出的是8位数据格式。SDA线上的每一位等同于SCL线上的一个脉冲,并且数据传输时一般是以最高有效位(MSB)开始。可以发送或接收的数据长度是没有限制的,但是发送器和接收器传输的数据长度必须一致。

I2C模块支持下列数据格式:

- 7位寻址模式

- 10位寻址模式

- 自由数据格式模式

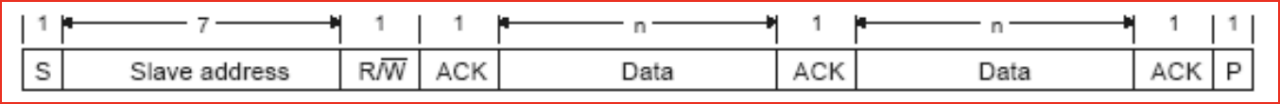

I2C 7位寻址格式

- 在7位寻址格式中,开始状态后的第一个字节由一个7位的从地址和紧跟着的一个R/W位组成,R/W位决定着数据的方向:

- R/W = 0:主模块向寻址的从模块写(发送)数据

- R/W = 1:主模块从从模块读(接收)数据

- 在R/W后面插入了一个专门用来确认的(ACK)附加时钟周期。如果是从模块插入ACK位,后面紧跟着来自发送机(主或从,由R/W位决定)的n位数据。n是一个2到8之间的数,接收机是在传输的数据位后面插入一个ACK位。

I2C 10位寻址格式

- 10位寻址格式跟7位寻址格式类似,只是主模块通过两个字节的传输来发送从地址。

- 第一个字节包括11110b,10位从地址的两个MSBs以及R/W = 0 (写)。第二个字节为10位从地址中的剩余的8位。

- 在传输完每个字节后,从模块必须要发送确认(ACK)。

- 在主模块向从模块写入第二个字节后,主模块可以继续写数据,也可以使用一个重复的开始状态来改变数据方向。

I2C 自由数据格式

- 开始状态后紧跟一个数据字。

- 在每个字后面都要插入一个ACK位,字的位数可以是2到8之间的任意数。不发送地址和数据方向位。

- 发送机和接收机必须都支持自由数据格式,而且在传输过程中数据方向必须恒定。

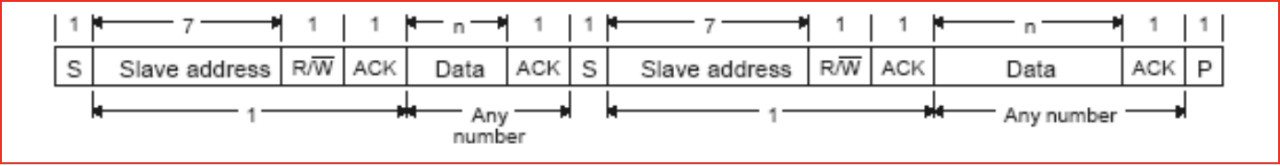

I2C 使用一个重复的开始状态

-

在7位寻址,10位寻址和自由数据格式中,可以使用重复的开始状态。

-

在每个数据字的末尾主模块都可以驱动另一个开始状态。

-

在结束状态之前,主模块可以发送/接收任意数目的数据字。

-

数据字的长度可以是2到8之间的任意值。

-

使用重复开始状态的7位寻址格式如下图所示。

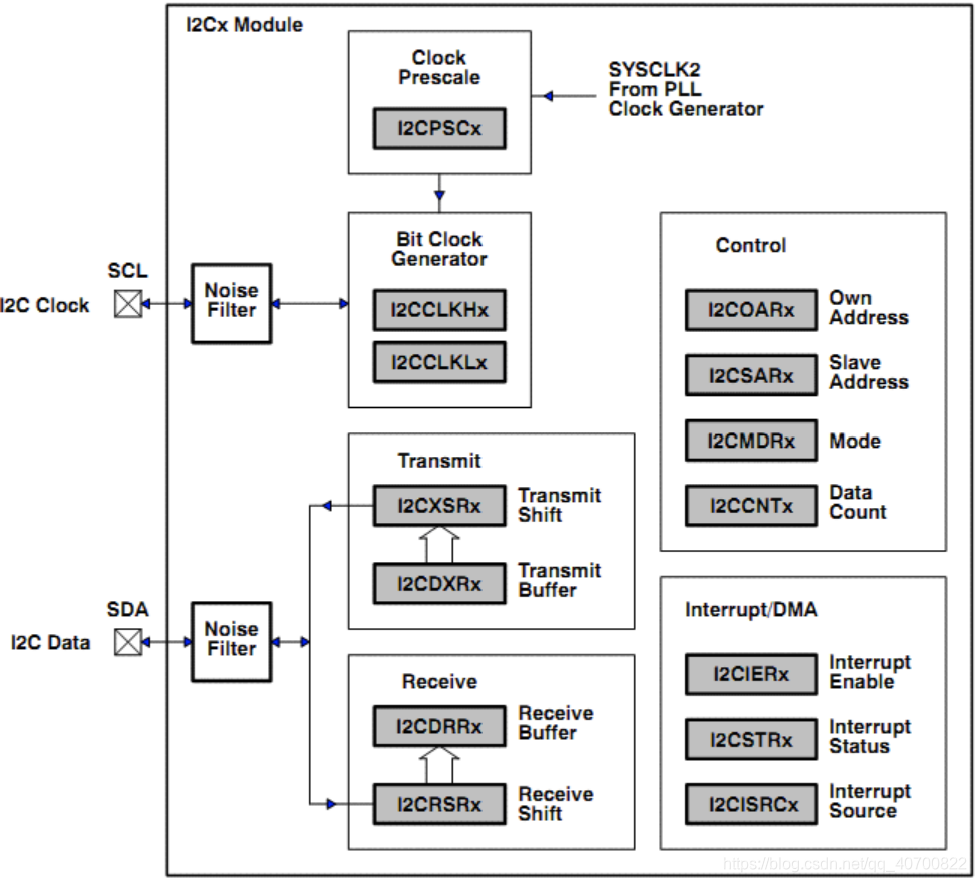

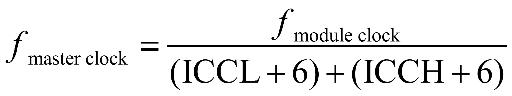

I2C 时钟产生

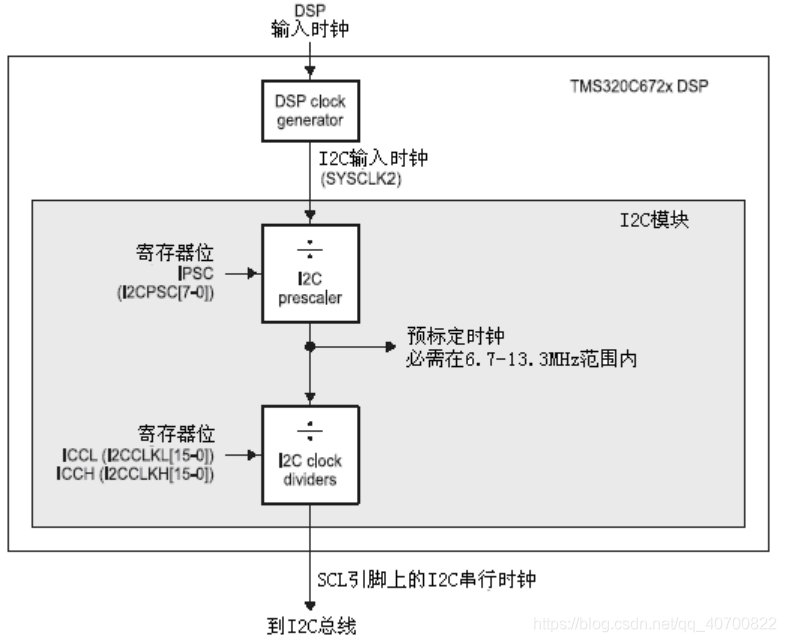

- DSP时钟发生器从外部时钟源接收一个信号,产生一个I2C输入时钟。

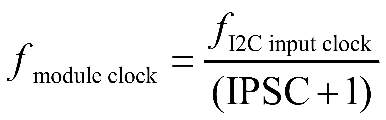

- I2C模块中的可编程预标定器(prescaler)将I2C的输入时钟分频产生预标定时钟,此时钟必须在6.7-13.3 MHz范围内。

- I2C模块的时钟分频器将预标定的时钟信号再分频,得到I2C串行时钟。

- 当将I2C模块配置为I2C总线上的一个主模块时,这一串行时钟就会由SCL引脚引出。

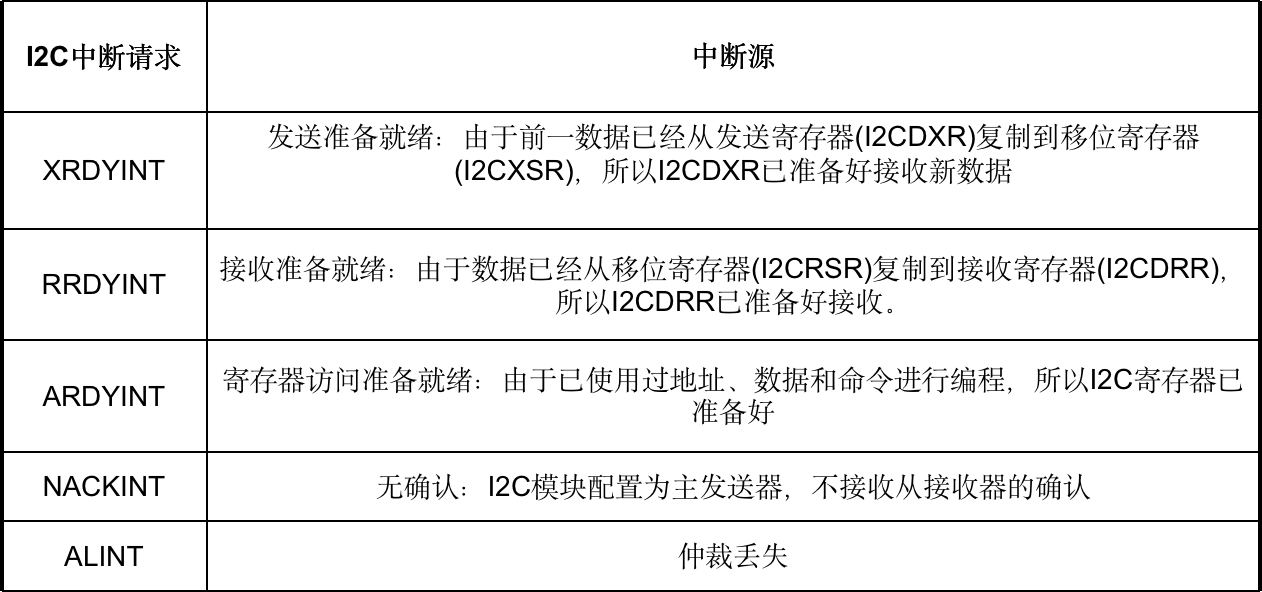

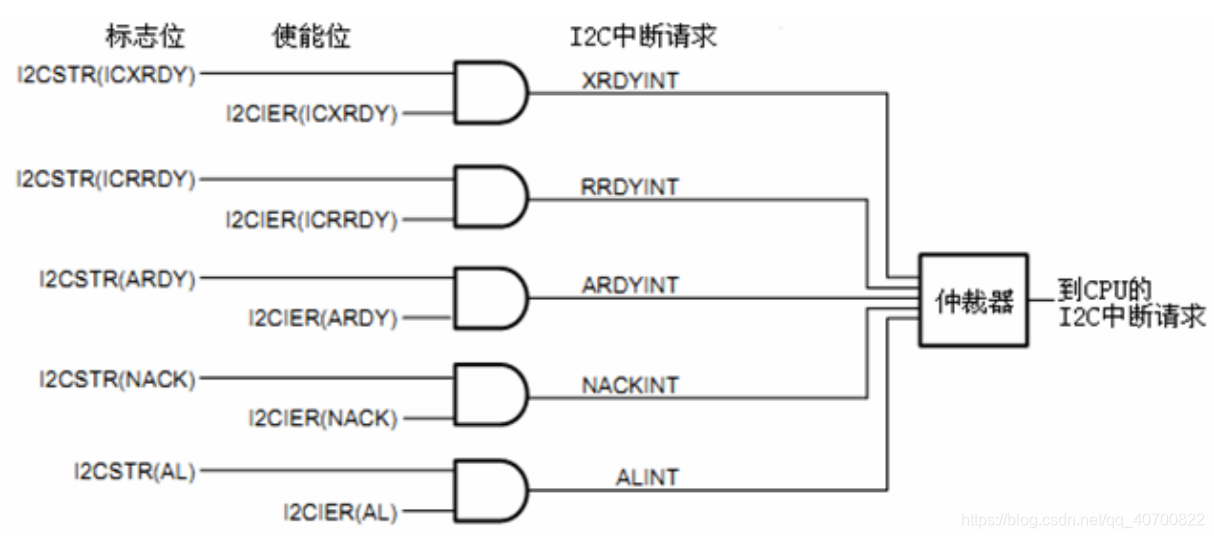

I2C中断请求

I2C中断请求:

I2C中断请求使能路径:

I2C—EDMA事件

- EDMA控制器在处理发送和接收数据时,I2C模块会产生下列两个EDMA事件。

- 接收事件(REVT):当接收的数据从接收移位寄存器(I2CRSR)复制到数据接收寄存器(I2CDRR)时,I2C模块就会将一个REVT信号发送给EDMA控制器,EDMA控制器可以从I2CDRR中读取数据。

- 发送事件(XEVT):当发送的数据从数据发送寄存器(I2CDXR)复制到发送移位寄存器(I2CXSR)时,I2C模块就会将一个XEVT信号发送给EDMA控制器。作为回应,EDMA控制器可以将下一个发送数据写入I2CDXR。

I2C模块的复位/禁止

可以通过两种方式来复位/禁止I2C模块:

- 向I2C模式寄存器(I2CMDR)中的I2C复位位(IRS)写入一个0。所有的状态位(在I2CSTR中)被强制置为它们的默认值,并且I2C模块一直保持禁止直到IRS变为1。SDA和SCL引脚处于高阻状态。

- 通过将RESET引脚驱动为低电平使DSP复位。在将RESET释放后,所有的I2C模块寄存器全部被复位成它们的默认值。IRS位被强制置为0,这会使I2C模块复位。I2C模块一直处于复位状态,直到向IRS写入1。

I2C模块的编程指南

按照下面所列事项对I2C模块进行编程:

- 1.对I2C预定标寄存器(I2CPSC)编程,得到需要的模块时钟;

- 2.使I2C模块退出复位状态(IRS = 1):如果使用发送/接收数据的中断,就在I2CIER中使能相应的中断;如果使用EDMA发送/接收数据,就使能EDMA并对EDMA控制器编程

- 3.初始化,配置I2C模式寄存器(I2CMDR);

- 4.对I2C时钟分频器(I2CCLKL和I2CCLKH)进行编程,得到SCL主时钟

- 5.配置地址寄存器:配置自身地址寄存器(I2COAR)和配置从地址寄存器(I2CSAR)

- 6.对发送数据寄存器(I2CDXR)编程

- 7.配置状态和模式寄存器(I2CSTR)

- 8.轮询接收数据

- 9.轮询发送数据

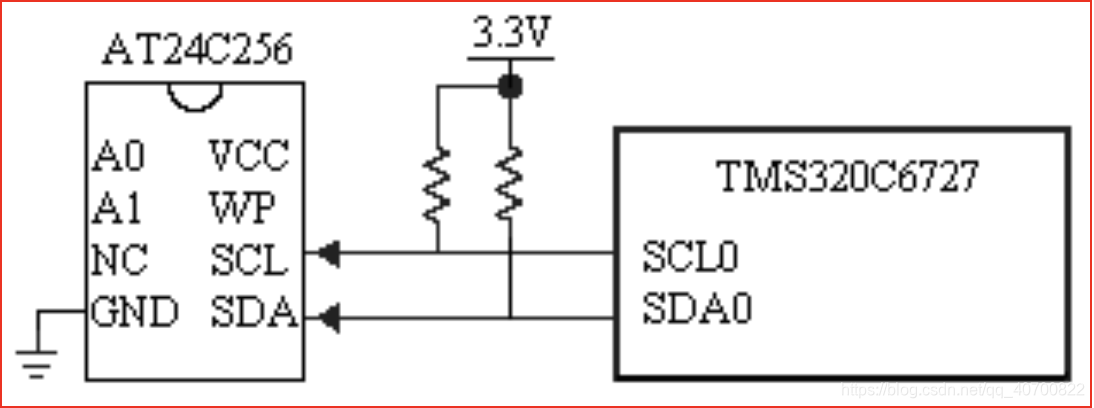

I2C 模块应用示例

AT24C256 是ATMEL 公司生产的256k位串行可擦除只读存储器(EEPROM),具有I2C总线接口,采用8 引脚双排直插式封装,具有结构紧凑、存储容量大等特点。由STA、SCL两线构成的I2C总线可接4 片AT24C256,特别适用于具有大容量数据储存要求的数据采集系统。