第十二章 通用输入输出端口

第十二章 通用输入输出端口

GPIO接口

- 通用输入/输出端口提供可配置为输入或输出的通用引脚。

- 设置为输出时,用户可通过向内部寄存器写数据来控制由输出引脚驱动的状态。

- 设置为输入时,用户可通过读取内部寄存器的数据来检查输入状态。

- 另外,在不同的中断或事件产生模式下,GPIO能够产生CPU中断和EDMA事件。

GPIO寄存器

GPIO使能寄存器(GPEN)

GPIO方向寄存器(GPDIR)

GPIO数值寄存器(GPVAL)

GPIO Delta寄存器(GPDH,GPDL)

GPIO屏蔽寄存器(GPHM,GPLM)

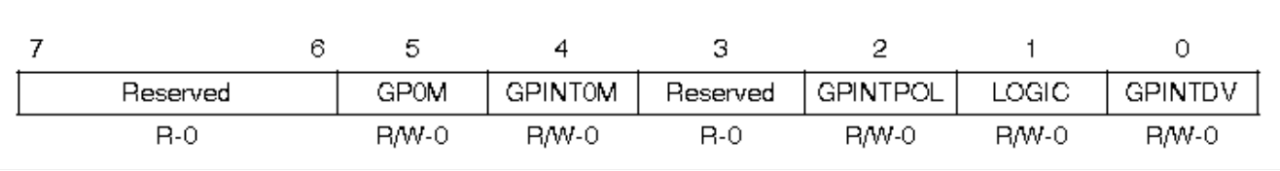

GPIO全局控制寄存器(GPGC)

GPIO中断极性寄存器(GPPOL)

通用输入/输出端口功能

- GPIO引脚一旦在GPIO使能寄存器内被激活,就可作为通用I/O口运行。

- 可通过GPDIR寄存器独立地把每个GPIO引脚设置为输入或输出。

- 当设置为输出时,GPVAL寄存器中GPxVAL位内的数值将受到相应的GPx引脚的驱动;当设置为输入时,输入的状态能从GPxVAL位读取。

- 对于通用I/O口的功能,通用I/O口内的边沿检测逻辑反映了一个给定的GPIO输入信号上是否发生一个跃变。

- 把GP0设置为通用输出口,除了设定GP0DIR=1外,还要将GPIO全局控制寄存器内的GP0M位设置为0。

中断和事件产生

在以下两种模式中,GPIO口能对CPU产生中断,并对EDMA

产生同步事件。

扫描二维码关注公众号,回复:

11187763 查看本文章

- 直通模式

- 逻辑模式

直通模式

直通模式适用于所有的GPIO信号。在该模式下,CPx输入引脚上的一个跃变使能CPU产生一次中断事件,使EDMA产生一次同步事件。

逻辑模式

- 该模式下,中断/事件是由基于GPIO输入的一种逻辑组合产生的。

- 逻辑功能的输出GPINT是依据任一GPIO输入信号特定边沿(上升、下降或两者)或特定数值的检测产生的。

- 禁用的GPIO信号或使能GPIO输出不能够被用作中断/事件的产生。

- 逻辑模式输出GPINT和直通模式输出GPINT0_int多路选择来产生一次CPU中断和一件EDMA事件。

- 为了能使用逻辑模式来产生一次中断,GPGC寄存器的GPINT0M必须设定为1。GPINT信号也能驱动GP0引脚输出。

GPINT信号的产生能以3种模式之一操作,3种模式为:Delta“或”模式、 Delta“与”模式和数值“与”模式。

Delta“或”模式

Delta“与”模式

数值“与”模式

GPINT与GP0和/或GPINT0的复用

GPIO中断/事件

- 通过内部的GPINTx信号,通用I/O外设分别对CPU和EDMA产生中断事件。

- GPINT1~GPINT15仅能在直通模式下使用,而GPINT0既能在直通模式下也可在逻辑模式下使用。

- 所有的GPINTx都可用作对EDMA的同步事件,只有GPINT0和GPINT[4:7]可用作对CPU的中断源。