更多内容关注微信公众号“FPGA科技室”

ZYNQ是一款SOC芯片,其最突出的功能就是其内部包含了一个双核的Cortex_A9内核。进行ZYNQ的SOC学习。这次,讲解最基础但可以让大家熟悉zynq开发的基本流程,完全操作。

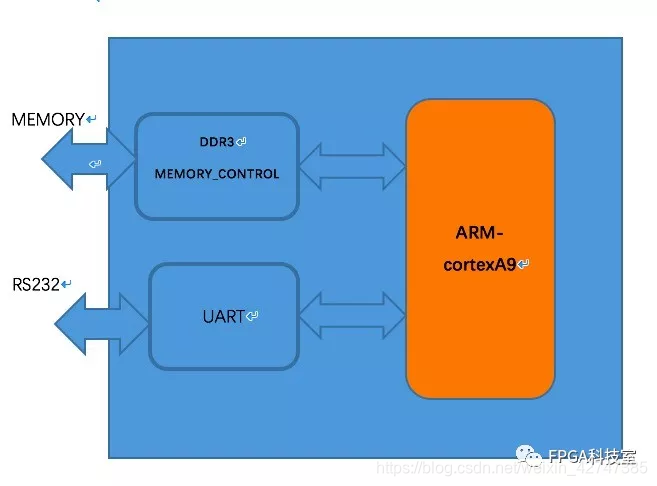

最小系统分析

下面这张图展示了我们需要构建的最小系统。并且本节的嵌入式实验会基于这个最小系统进行添加外设。

**实验综述:**只会使用到PS部分资源,包括ARM Cortex—A9、DDR3内存、一个UART串口。这就是我们的最小系统。首先我们程序会加载到DDR内存中,然后CPU一条一条执行,程序的执行情况可以通过串口打印进行观察。

开始操作:

创建一个VIVADO工程

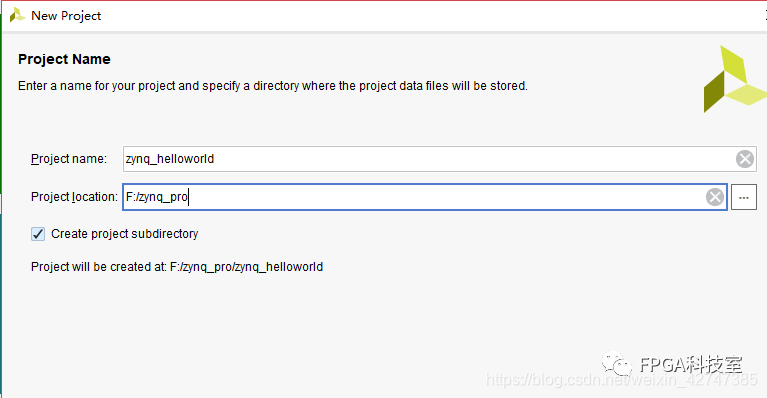

step1: 在打开的VIVADO软件界面,单击Create New Project

单击 Next,在弹出的窗口中输入工程名和保存路径,然后单击Next

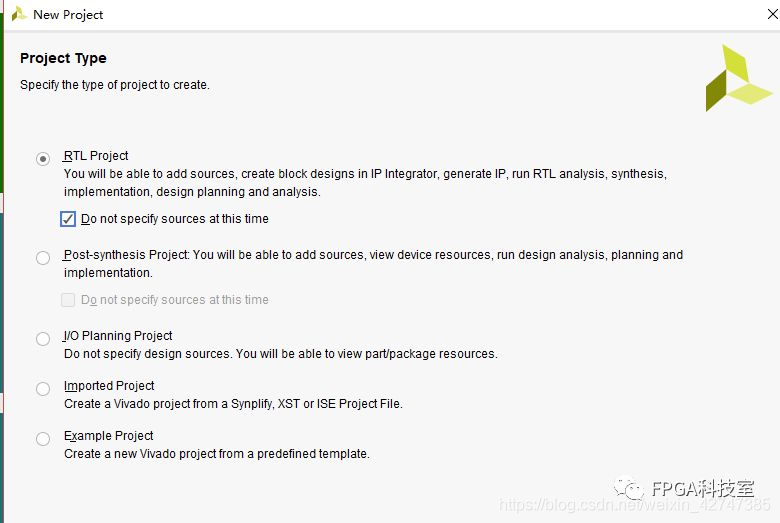

按下图进行设置

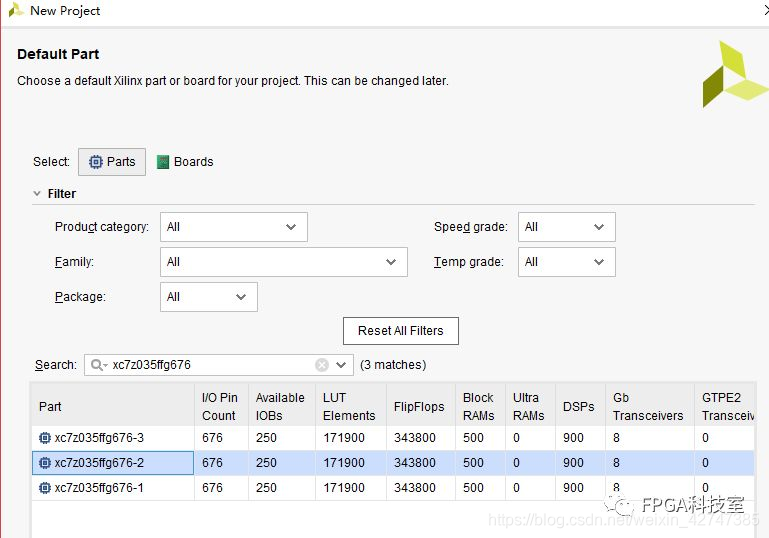

选择芯片型号

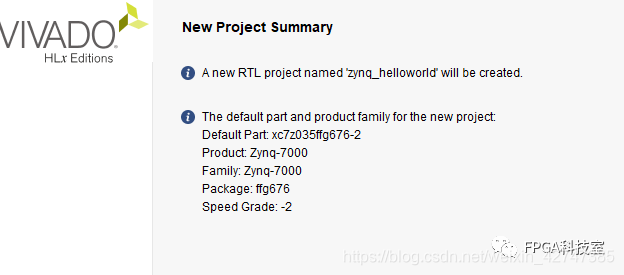

单击Finish完成工程的创建

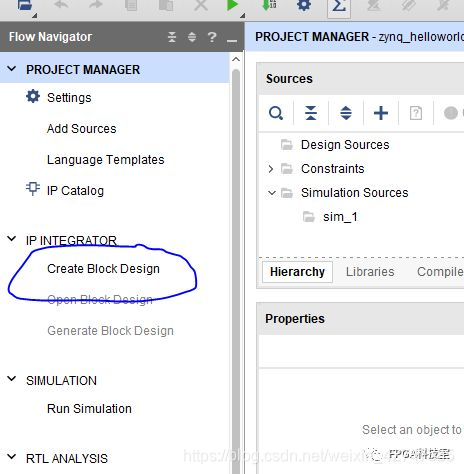

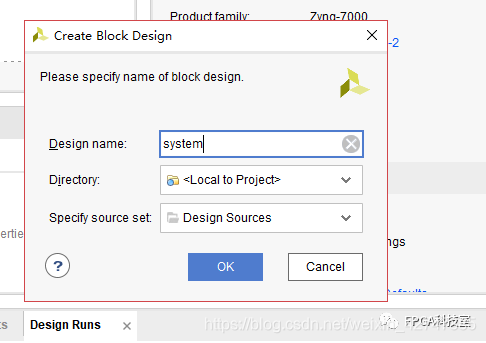

单击Create Block Design,输入名称system

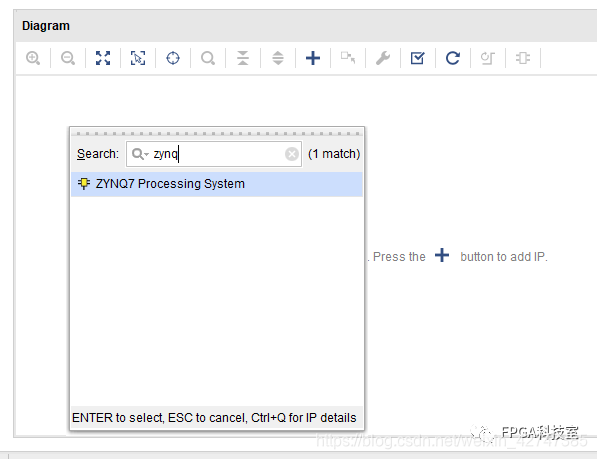

单击“+” 号,添加IP

搜索“ZYNQ”,然后双击

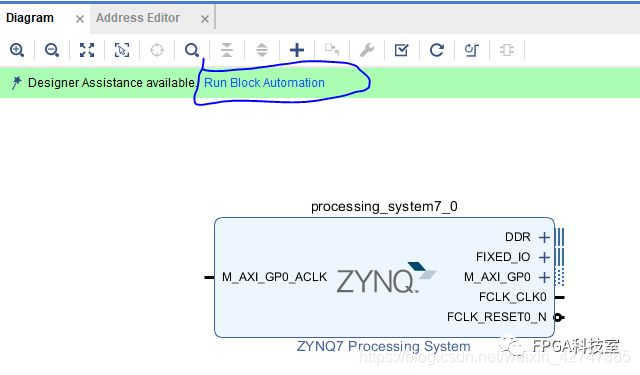

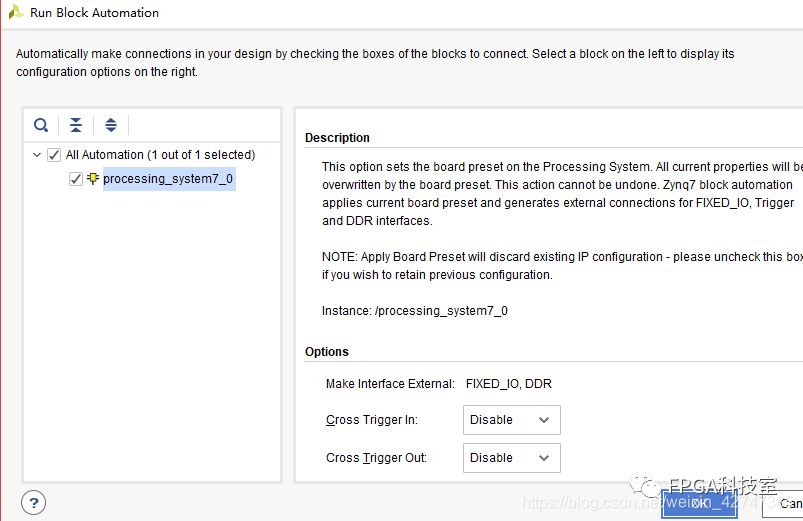

添加进来zynq cpu IP,然后单击 Run Block Automation,直接单击 ok

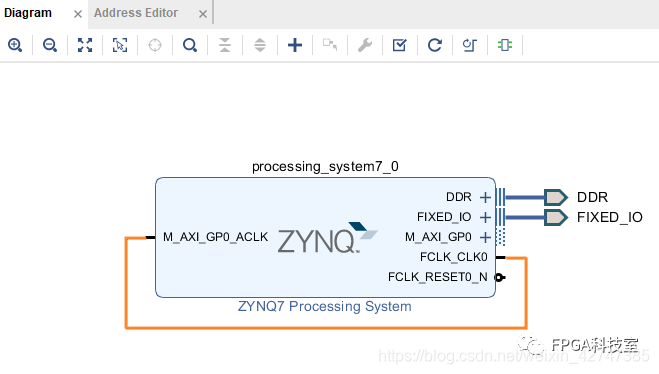

在Block 文件中,我们进行连线,将鼠标放在引脚处,鼠标变成铅笔状后进行拖拽,连线如下图所示。连线的作用就是把PS的时钟介入PL,当然我们这里暂时还用不到PL部分的资源。

双击 ZYNQ CPU IP ,对其进行设置,使其对应硬件设置。在此部分,我们需要做的就是修改时钟频率,内存类型和接口输出。需要注意的是如果时钟频率、内存类型与我们的硬件不一致时,SDK中的程序会崩溃,运行不下来。这在后续的调试中是一个小技巧。正确的配置是成功的必要条件。

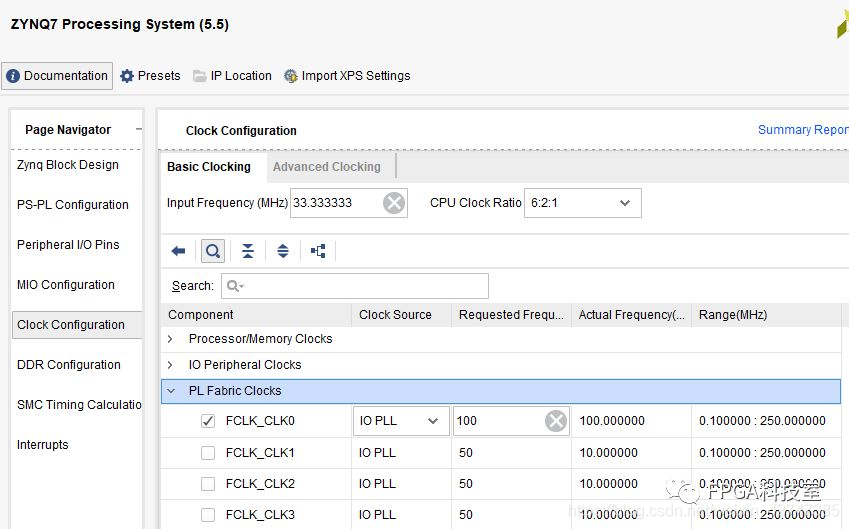

PS时钟配置:

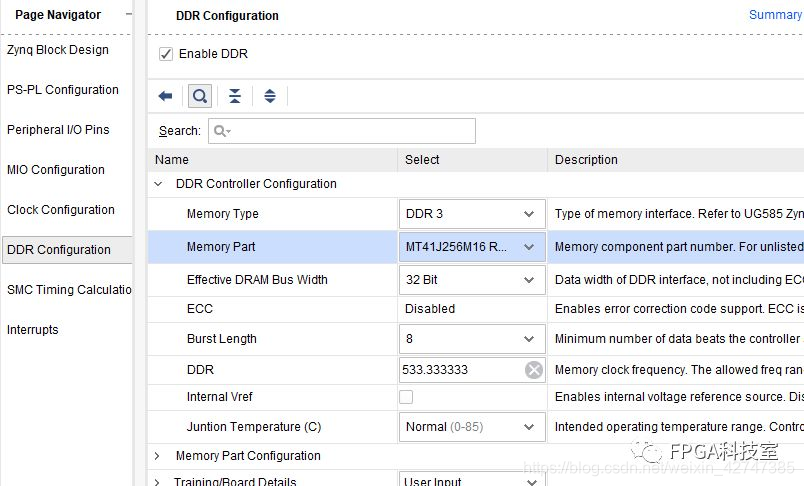

内存配置:(MTKM16 RE-125)

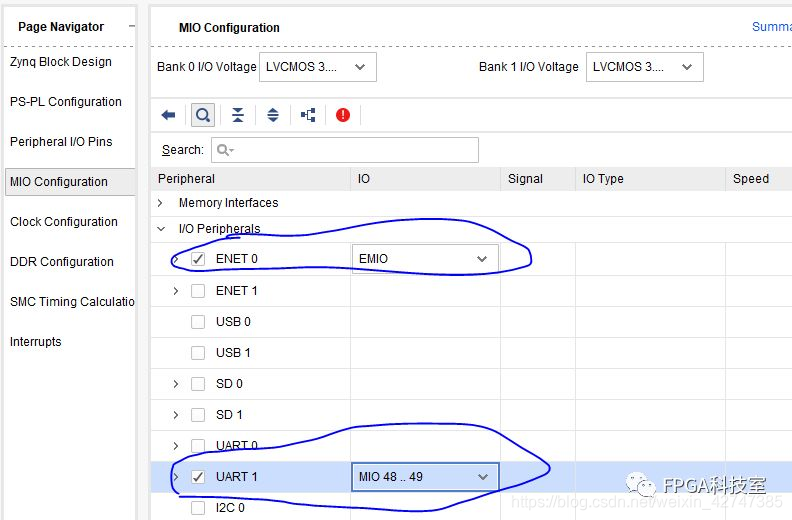

设置外扩接口,之后点击OK

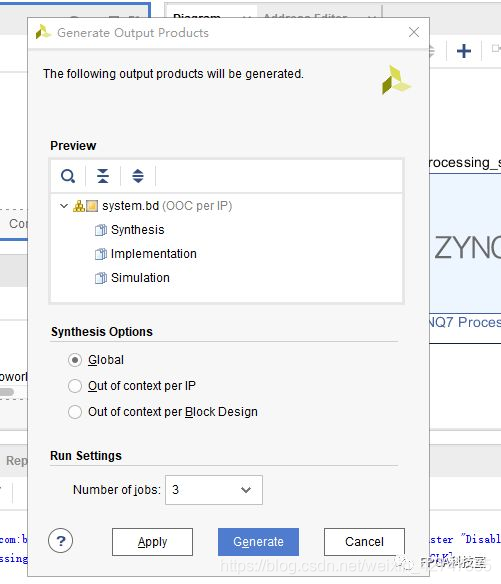

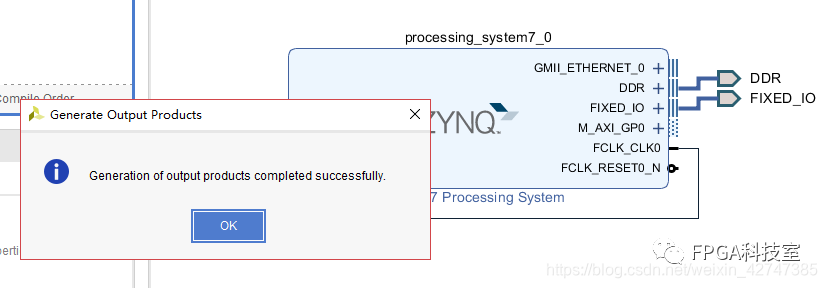

右击 system.bd ,单击Generate Output Products

此步操作会产生执行、仿真和综合文件

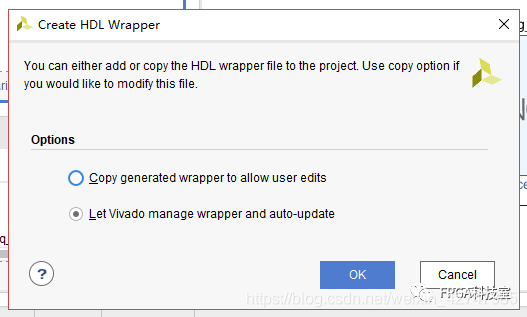

右击system.bd 选择Create HDL Wrapper 者不得作用是产生顶层HDL文件,选择让vivado自动管理

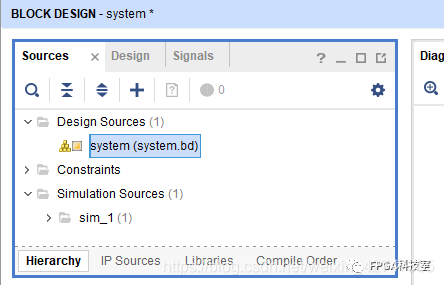

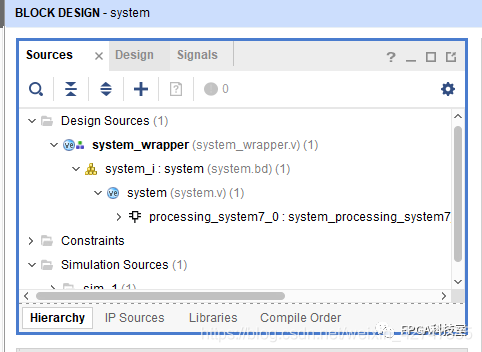

源码的层次结构,可以看到system_wrapper.v就是顶层文件

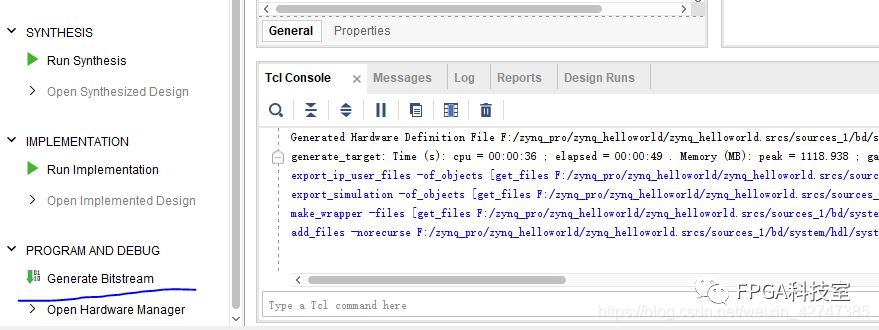

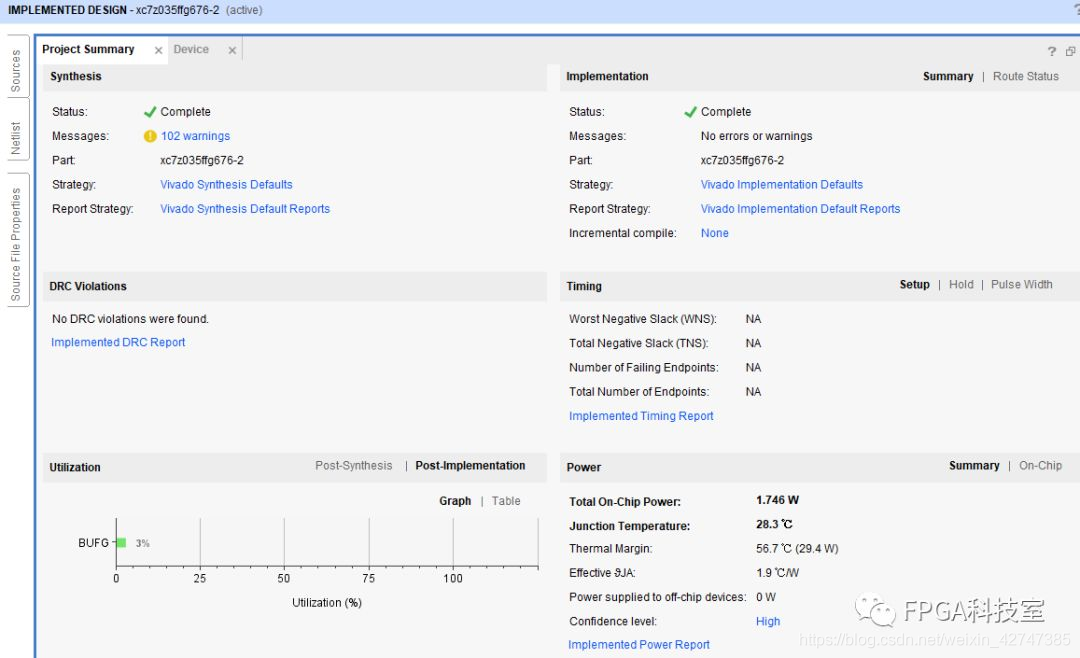

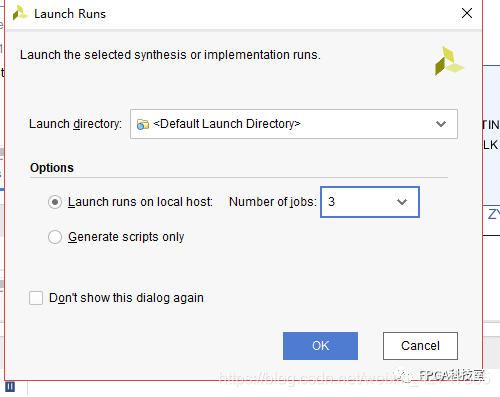

最后综合

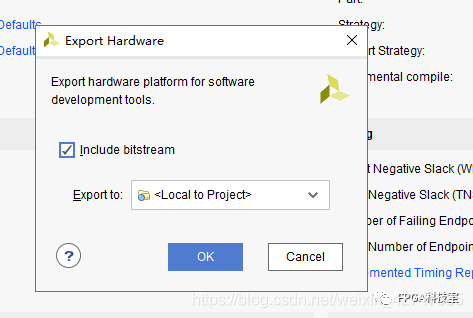

导出SOC硬件到SDK

File-> Export-> Export Hardware,包含比特流

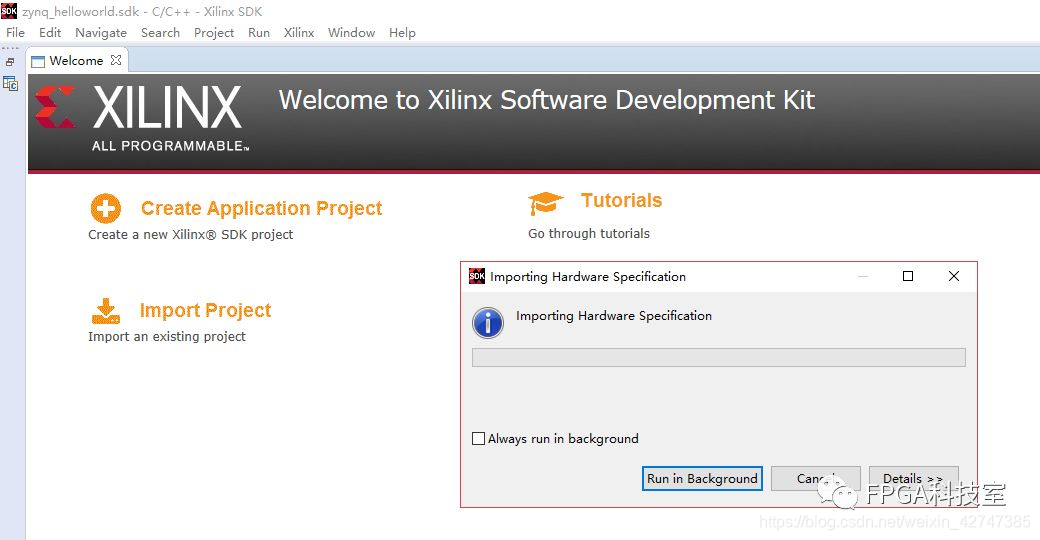

File->launch SDK,启动SDK

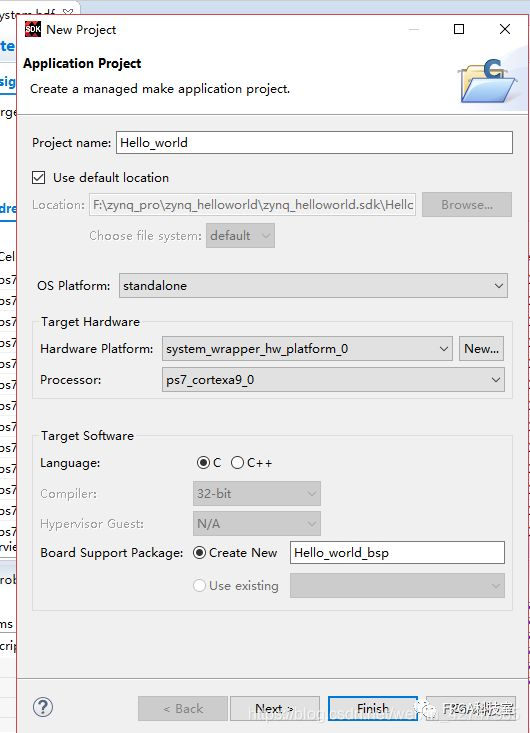

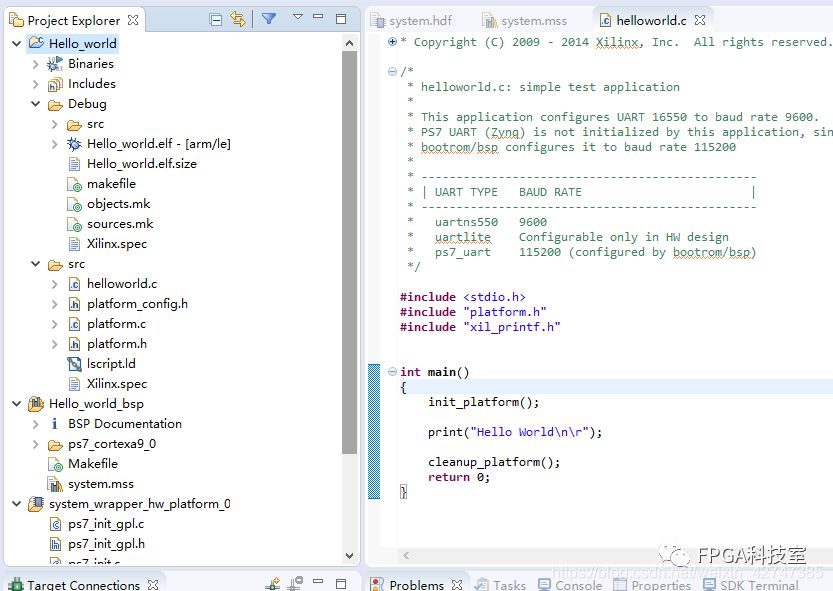

在SDK开发环境下,File-> New -> Application Project

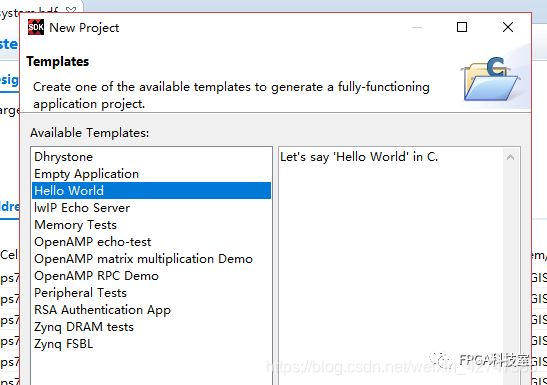

系统里面有很多的自带程序,本次就用自带的Helloworld程序做测试,单击Finish

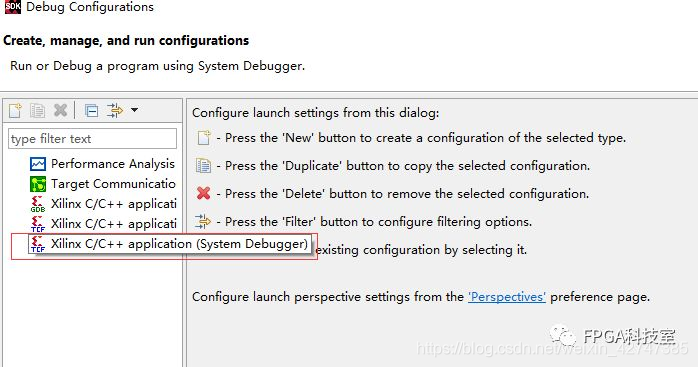

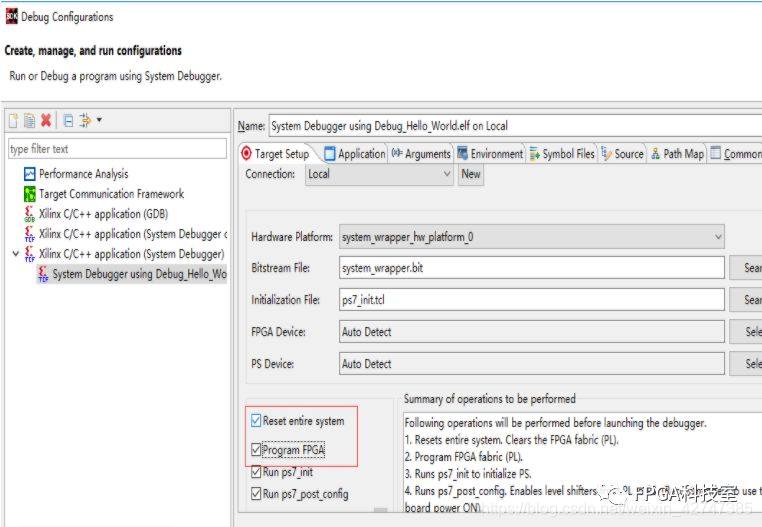

连接开发板,上电。右击 Helloworld ->Debug as

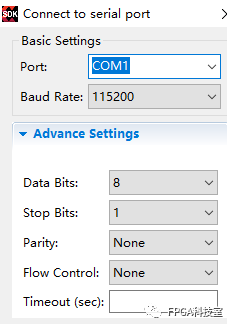

用系统自带的串口调试助手,进行相关设置

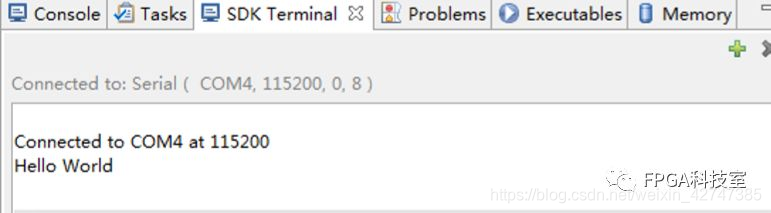

单击运行输出结果