翻译的资料是公开的,在这里下载https://www.nxp.com/products/microcontrollers-and-processors/additional-processors-and-mcus/8-16-bit-mcus/16-bit-s12-and-s12x-mcus/ultra-reliable-s12xe-high-performance-automotive-and-industrial-microcontrollers:S12XE?tab=Documentation_Tab,我想应该不会有什么版权问题,如涉及版权问题,请联系我删除文章。另感谢NXP提供的学习资料。

An Introduction to the External Bus Interface on the HCS12X

By:Daniel Malik

Microcontroller Division

East Kilbride, Scotland

译者注:译者博客(http://blog.csdn.net/lin_strong),转载请保留这条。此为官方文档AN2708,仅供学习交流使用,请勿用于商业用途。

介绍

这篇应用笔记描述了HCS12X微控制器家族上的外部总线接口(External Bus Interface,EBI),还特别讨论了HCS12和HCS12X接口上的区别。这篇应用笔记的内容不适用于0L40V掩码组(S12XDP512的试生产版本)。

外部总线的作用

大部分嵌入式应用都使用单芯片配置,也就是没用到那些需要连接到微控制器总线上的外部组件(所以称为 “单芯片” 模式)。当应用中需要实现以下功能时,需使用外部总线接口:

- 扩展内部总线以连接外部 存储器/外设。

- 仿真支持。

仿真支持主要由在电路仿真器(in-circuit emulators,ICE)利用,这是一个非常特殊的应用领域。在这个罕见(但是重要)的应用中,芯片会运行在被称为“仿真”的模式下。

大部分应用使用外部总线接口是为了连接额外的系统组件,可能是微控制器芯片本身没有的组件,也可能是想扩展芯片上已有的资源(比如增加额外的CAN接口或者额外的存储器)。在这些情况中,芯片运行在叫做 “一般扩展”的模式下。

外部总线接口在“仿真”模式下的行为与在 “一般扩展”模式下的不一样。这篇文档描述了外部总线接口在 “一般扩展”模式下的行为。如果想要了解 “仿真”模式下的行为细节,请查阅外部总线接口的文档(见 参考文献)。

外部总线接口的信号引脚

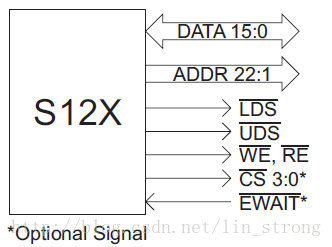

图1中的框图展示的是与外部总线接口相关的信号引脚。而表1中则给出了每个信号引脚的简短的功能描述。

图 1.S12X信号引脚框图

带有星号的信号引脚是可选的。意思就是用户可以根据应用的需求来决定用不用它们。当某个信号引脚被禁用了,它就变成了另一个功能(比如,通用I/O)。

- 注意:

- 不是所有的设备型号或封装都有所有的信号引脚的。详见设备的用户手册。

表 1.S12X信号引脚描述

| 信号引脚 | 描述 |

|---|---|

| DATA15-DATA0 | 写操作时的输出信号,读操作时的输入信号。 |

| ADDR22–ADDR1 | 外部总线操作时的输出地址。 |

|

高位数据选通信号;它表明数据行DATA15-DATA8包含了S12X提供的有效信息(写)或者被驱动来获得外设的有效状态(读)。 |

|

低位数据选通信号;它表明数据行DATA7-DATA0包含了S12X提供的有效信息(写)或者被驱动来获得外设的有效状态(读)。 |

|

芯片选择3-0;在总线访问地址400000h–7FFFFFh ( )、200000h–3FFFFFh ( )、200000h–3FFFFFh ( )、100000h–1FFFFFh ( )、100000h–1FFFFFh ( )和000800h–0FFFFFh( )和000800h–0FFFFFh( )时低电平有效;需要在MMCCTL0寄存器中使能它。 )时低电平有效;需要在MMCCTL0寄存器中使能它。 |

|

读使能;在外部总线读访问时低电平有效。 |

|

写使能;在外部总线写访问时低电平有效。 |

|

外部等待信号;当被外设断言时,微控制器会停机并等待外设结束操作;需要在EBICTL1寄存器中使能它。 |

- 注意:

-

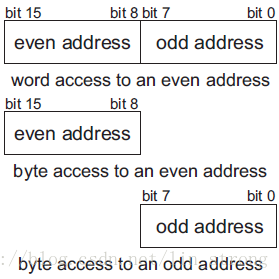

高位数据选通

是用于授权数据总线的高位部分(DATA15-DATA8),而低位数据选通

是用于授权数据总线的低位部分(DATA7-DATA0);这也就是说偶数地址上的数据是通过DATA15-DATA8来访问的,而奇数地址上的数据则是通过DATA7-DATA0来访问的。这是由于MCU的大端特性。图2中描绘了这个问题。在大端MCU中,多字节数据元素的最高有效字节(MSB)被存储在较低的地址,而最低有效字节(LSB)则被存储在较高的地址。对于字(两个字节的元素)来说,数据位15-8放在偶数(较低)地址,7-0放在奇数(较高)地址。因此,数据总线的较低的那半部分对应较高地址,较高的那半则对应较低的地址。对于奇数地址的字访问不受外部总线接口的支持;这是种特殊情况,表2中进行了描述。

图 2.数据位与地址的关系

外部总线操作

前面说过,外部总线上可以进行两种操作:读和写。在一次写操作中,数据被从S12X微控制器传输到连接在外部总线上的外设中。在一次读操作中,则相反,即从外设传输到S12X微控制器中。

写操作

在写操作中,微控制器会进行以下步骤。

- 驱动ADDR、

&

引脚到对应的电平。

断言信号引脚(如果使能了它)。

- 驱动DATA引脚到对应的电平以在写入数据之前给出数据。

- 断言

引脚。

- 如果

信号引脚被使能,并且被外设断言,那就等到它取消断言。

- 等待要求的总线周期数(根据EBICTL1寄存器的内容)。

- 取消断言

引脚。

- 取消断言

信号引脚(如果前面断言了,并且没有连续的写;如果有连续的写入,可能会保持断言)。

停止驱动DATA引脚。

取消断言&

引脚。*

读操作

在写操作中,微控制器会进行以下步骤。

- 驱动ADDR、

&

引脚到对应的电平。

断言信号引脚(如果使能了它)。

- 断言

引脚。

- 如果

信号引脚被使能,并且被外设断言,那就等到它取消断言。

- 等待要求的总线周期数(根据EBICTL1寄存器的内容)。

- 从DATA引脚读取数据。

- 取消断言

引脚。

取消断言信号引脚(如果前面断言了,并且没有连续的读;如果有连续的读取,可能会保持断言)。

取消断言&

引脚。*

- *注意:

-

即使没有进行外部总线访问,ADDR引脚也总是会被外部总线接口驱动。在没有访问外部总线时(即,当

、

、

&

都在高电平时),ADDR引脚的状态是未定义的。如果在没进行外部访问时需要执行特殊的行为的话,软件可以使用EBICTL0寄存器的ASIZ字段来切换ADDR引脚为GPIO功能。详见后面。

不同类型的操作下,总线信号引脚的活动

表2详述了在 奇/偶 和 字节/字 访问期间,外部总线接口的

表2.S12X EBI信号引脚的活动性

| 操作 |  |

|

DATA 15-8 | DATA 7-0 |  |

|

|---|---|---|---|---|---|---|

| 向偶地址写入字节 | 不活跃 | 活跃 | 数据字节 | 未驱动 | 活跃 | 不活跃 |

| 从偶地址读取字节 | 活跃 | 不活跃 | 数据字节 | 被MCU忽视 | 活跃 | 不活跃 |

| 向奇地址写入字节 | 不活跃 | 活跃 | 未驱动 | 数据字节 | 不活跃 | 活跃 |

| 从奇地址读取字节 | 活跃 | 不活跃 | 被MCU忽视 | 数据字节 | 不活跃 | 活跃 |

| 向偶地址写入字 | 不活跃 | 活跃 | 较高字节 | 较低字节 | 活跃 | 活跃 |

| 从偶地址读取字 | 活跃 | 不活跃 | 较高字节 | 较低字节 | 活跃 | 活跃 |

| 向奇地址写入字(第一步) | 不活跃 | 活跃 | 未驱动 | 较高字节 | 不活跃 | 活跃 |

| 向奇地址写入字(第二步) | 不活跃 | 活跃 | 较低字节 | 未驱动 | 活跃 | 不活跃 |

| 从奇地址读取字(第一步) | 活跃 | 不活跃 | 被MCU忽视 | 较高字节 | 不活跃 | 活跃 |

| 从奇地址读取字(第二步) | 活跃 | 不活跃 | 较低字节 | 被MCU忽视 | 活跃 | 不活跃 |

- 注意:

- 片上RAM支持在单个周期内对奇地址的字宽访问。但是,在外部总线上,这类访问会被拆分为两个相继的字节宽访问。内核会在为了进行外部访问而要求的插入周期间停机。

总线延伸周期

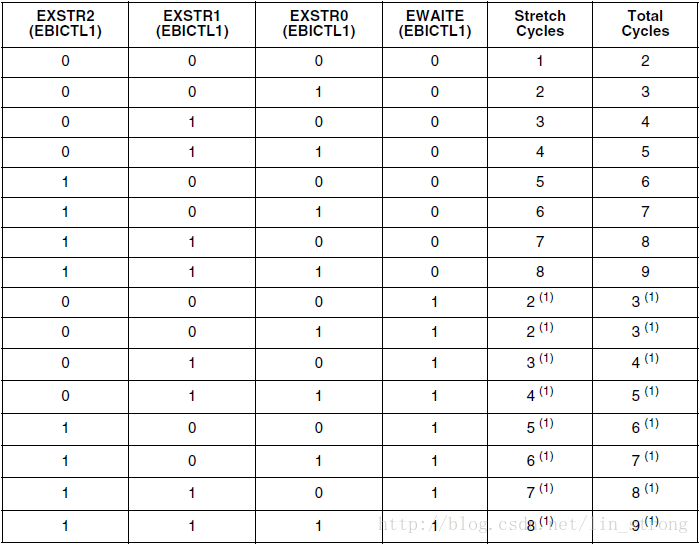

当访问片上外设和内存时,设备会在一个总线时钟周期内完成不管是8位还是16位的内核访问。但是,当在扩展模式下访问外部总线上的地址时,访问是“延伸的(stretched)”,要花费不止一个总线时钟周期。最少会延伸一个额外的总线时钟周期。延伸周期的数量,以及用于外部访问的总周期数,可以由用户使用EBICTL1寄存器的EXSTRx位设置。这使得用户能够基于连接到外部总线上的设备的时序需求来调整总线信号的时序。表3详述了不同配置下的周期数。

表 3.不同配置下的延伸周期数

- 注意:

-

1.如果使能了EWAIT特性,表中写的就是最小周期数。如果

还在被断言,则会增加额外的延伸周期。

外部等待

外部总线接口提供了一个新特性,这个特性使得外部外设能通过断言

I/O配置选项

上面描述了怎么在EBICTL1寄存器中配置延伸周期数以及使能/禁用

地址总线的大小

用户可以自由地根据具体的应用选择需要的地址总线宽度。通过限制地址线(address line)的数量(也就是限制可由外部总线寻址的目标地址的大小),就可以解放一些地址线并将其用作通用I/O。这个选择是通过赋值对应的值到EBICTL0寄存器的ASIZ[4:0]位来实现的。赋值给ASIZ的值越小,被外部总线接口使用的地址线数就越少。在极端的情况下,也就是ASIZ位被赋值位0时,外部总线不使用任何地址线,这样它们就都被用作通用I/O引脚。外部总线接口余下的引脚的功能不受影响。

数据总线的大小

外部总线接口默认支持16条数据线(data line)。但是,当与一个8位外设交互时只需要一半的数据线。这种情况下,可以使用EBICTL0寄存器的HDBE位来关闭总线接口的高位字节(DATA[15:8])。这样它们就可以被用作额外的通用I/O引脚,也就不需要断开未使用的数据线,也因此降低了设计的整体成本。如果只使用了一半的数据线进行外部总线访问的话,那么

阈值级别

可以使用EBICTL0的ITHRS位来降低外部总线接口输入信号引脚的输入阈值。这使得用户能够在设备由5V供电的情况下连接一个3.3V外设到外部总线上。但是,外部总线接口的输出线仍然会产生5V的信号,要注意确保外部3.3V外设能够接受5V的输入信号。

限制与接口选项

外设带来的限制

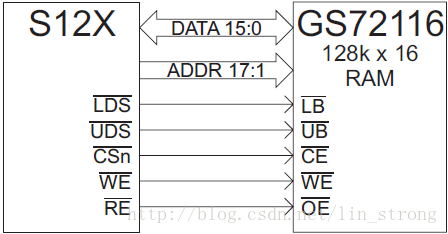

外部总线接口这个设计实现了在外部地址空间上读写单个字节。图3中展示了一个使用了这个特性的示例应用。

图3.使用外部总线来提供额外的256K字节的RAM。

但是,不是所有的16位外设设备都支持访问它们地址空间的单个字节的。读操作典型地没有这个问题,因为在这个事件中,MCU直接简单地忽略了一半的总线。但是,在写操作中,设备可能需要全部16位数据,而MCU可能只驱动一半的总线(根据写字节操作是在奇地址还是偶地址上进行的)。这会导致外设内无法避免的数据损坏。解决这个问题的最简单方案是,如果外部外设不支持访问它地址空间内的单个字节,那就不要执行写字节操作。

接入8位外设

外部总线接口主要是设计来接入16位外设的。但是,通过一定的限制,它也可以接入一个8位外设(比如,一个LCD驱动器)。在这种情况下,EBICTL0寄存器中的HDBE位被清零,只有较低一半的数据总线会被使用,

- 让数组变为两倍大,寻址时跳着访问数组。

- 创建数组为字数组,而不是字节数组,并且忽略数组中每个元素的较高字节。

两种方案都会带来轻微的额外软件开销,但是这是相对很小的,通常可以忍受。

总线访问时序图 — 操作的示例

下面的图表基于现实世界中的测量;但是,它们仅仅用于例证目的。用户应该总是参考设备规范来获取精确的时序值。

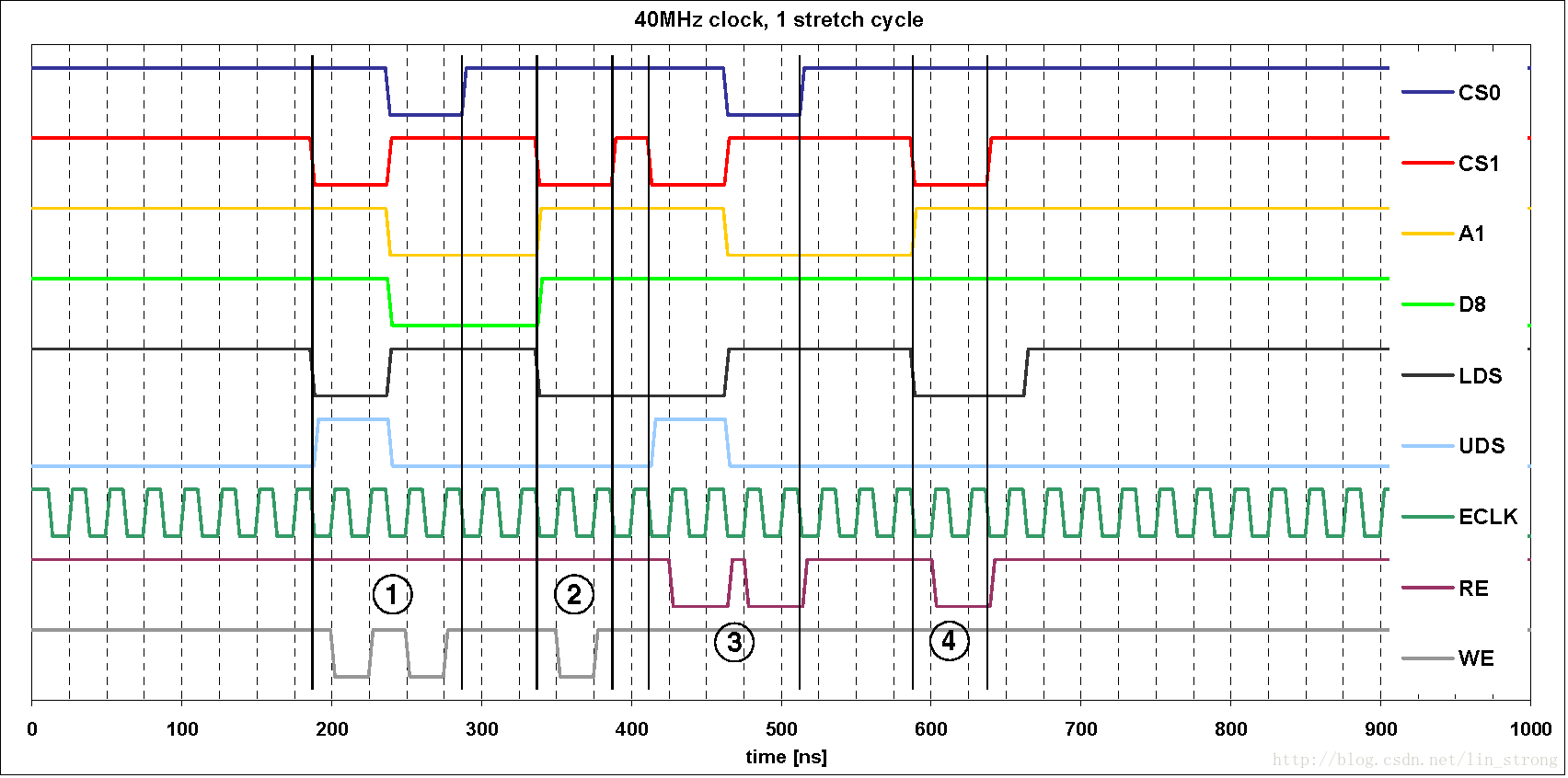

图4展示的是在40MHz总线时钟下、EBICTL1寄存器中选择了一个延伸时钟周期并且禁用了EWAIT特性时,不同外部总线信号引脚间的关系。图中进行了以下的外部总线访问:

- 在地址0x3F_FFFF处写入0xFF7E

- 在地址0x3F_FF7E处写入0xFFFF

- 从地址0x3F_FFFF处读取一个字

- 从地址0x3F_FF7E处读取一个字

图 4.一个延伸时钟周期时的外部总线访问时序图

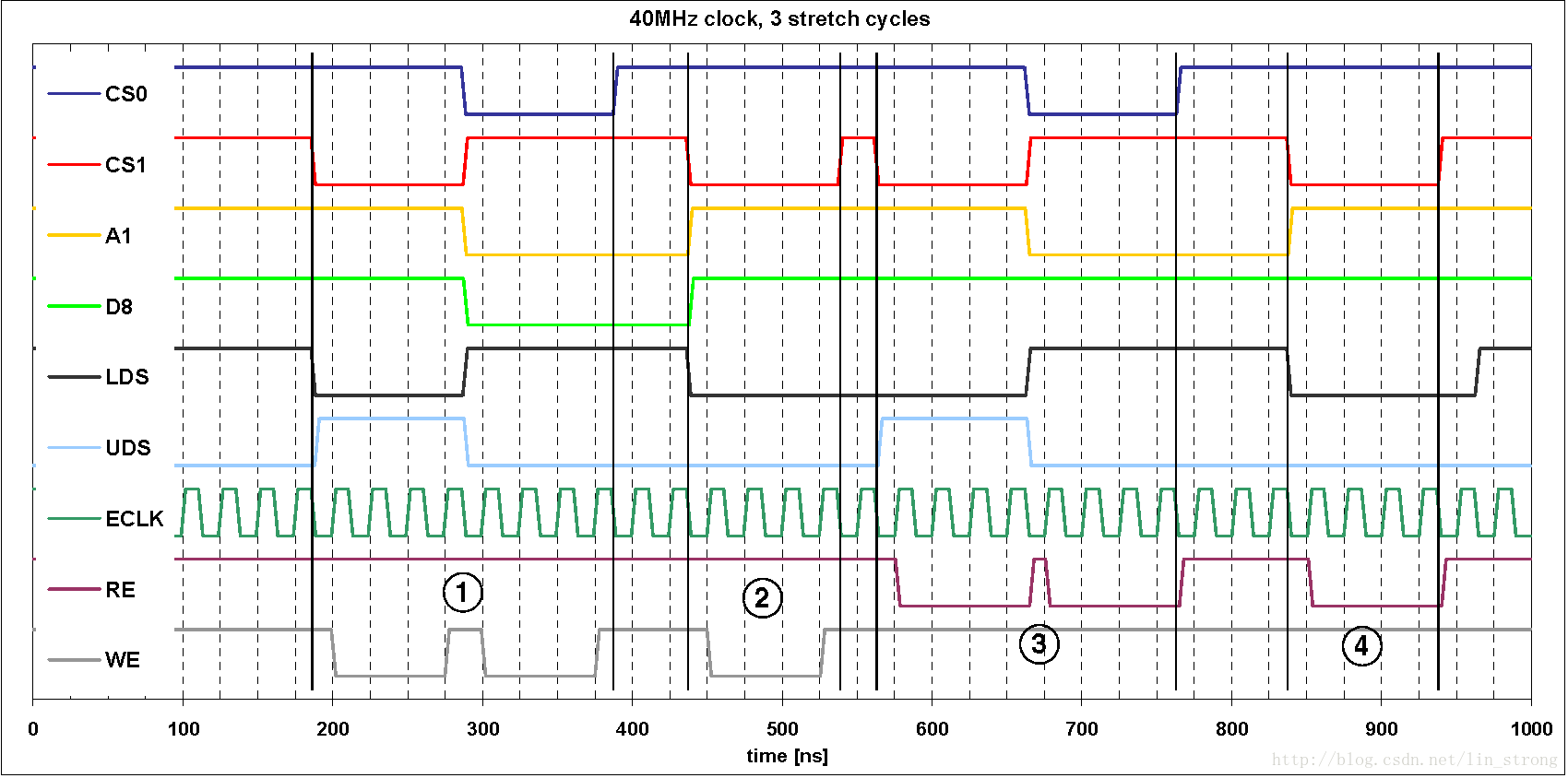

图5展示的是在40MHz总线时钟下、EBICTL1寄存器中选择了三个延伸时钟周期并且禁用了EWAIT特性时,不同外部总线信号引脚间的关系。图中进行了以下的外部总线访问:

- 在地址0x3F_FFFF处写入0xFF7E

- 在地址0x3F_FF7E处写入0xFFFF

- 从地址0x3F_FFFF处读取一个字

- 从地址0x3F_FF7E处读取一个字

图 5.三个延伸时钟周期时的外部总线访问时序图

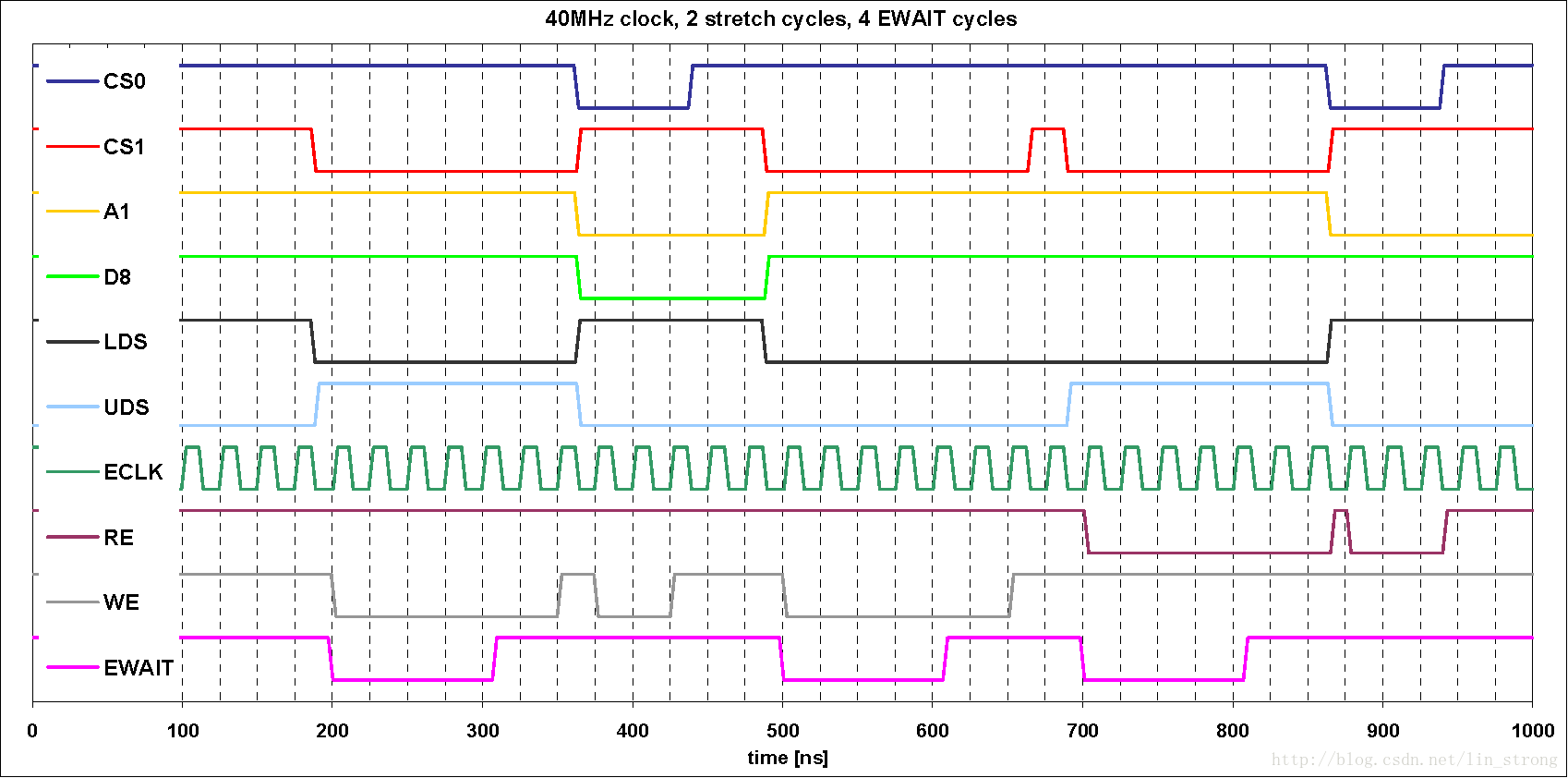

图6展示的是在40MHz总线时钟下、EBICTL1寄存器中选择了两个延伸时钟周期并且使能了EWAIT特性时,不同外部总线信号引脚间的关系。

图 6.两个延伸时钟周期并使能EWAIT特性时的外部总线访问时序图

参考文献

[1]External Bus Interface specification, Freescale Semiconductor, S12XEBIV2

[2]Module Mapping Control specification, Freescale Semiconductor, S12XMMCV2

[3]Data sheet to GS72116, GSI Technology, Rev: 1.04a