#来自学渣的问候~

上一个Robei的博客是利用 单个 的模块来进行仿真,没有自己创建模块,所以这个博客就讲,多个模块拼接成一个新模块的仿真。

之前还不太会用这个EDA 的时候,我有一种很草(一种植物)的想法,我00就算饿死,就算用纯Verilog来写代码,我也不用这个Robei EDA。现在,真香!(万物皆可真香定律)

不过关于Robei EDA 的妙处,下次再讲(滑稽保命)

硬件模块的搭建

-

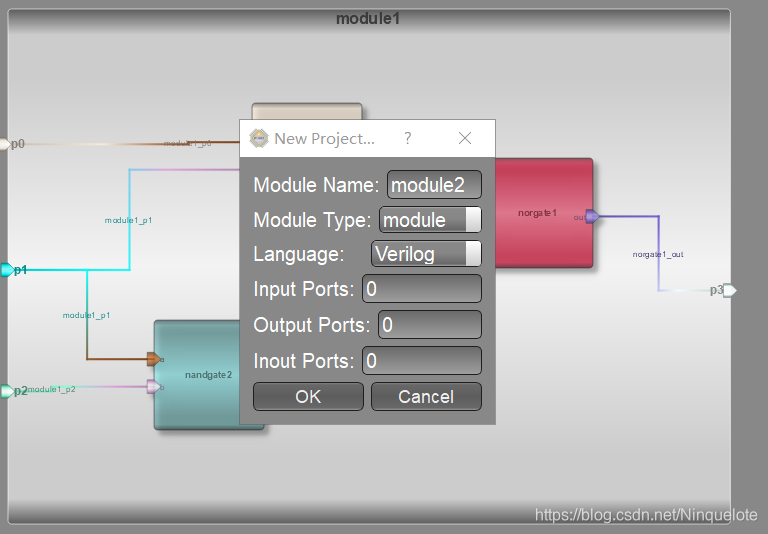

新建文件,设置 module Type 为

module,端口数可不写。

-

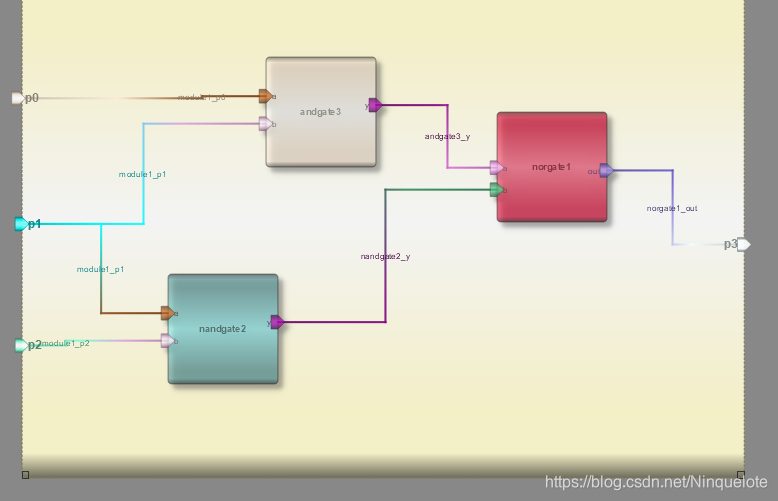

选择需要模块来搭电路

搭建电路样式如下,模块可以任意选择,不需要写代码。

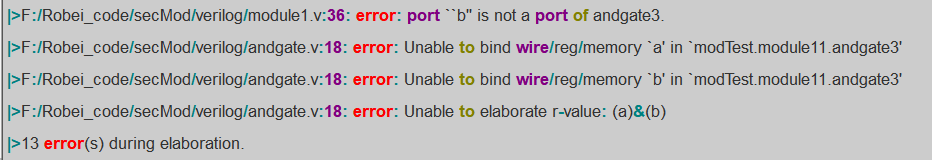

补个小贴士: 我刚开始搭建模块的时候,发现每个模块都有相同的引脚名称,比如图中的a、b、y,我想当然的认为变量名重复应该直接定义。于是,我直接修改了模块的变量名称。在编译的时候它出现了一下错误:

所以在这里,不要修改变量的名称,每个模块只和它本身的代码相关! -

保存为model后缀的类型文件。

这个时候,在界面的Current 一栏上,就会出现这个名称的模块。

-

进行编译,点击下载箭头(Compile & Generate code)

这个就是初步成功了

生成激励文件

-

创建激励文件

具体看前一个博客,这个链接 -

连接电路图,INPUT都选为reg类型

-

编写代码

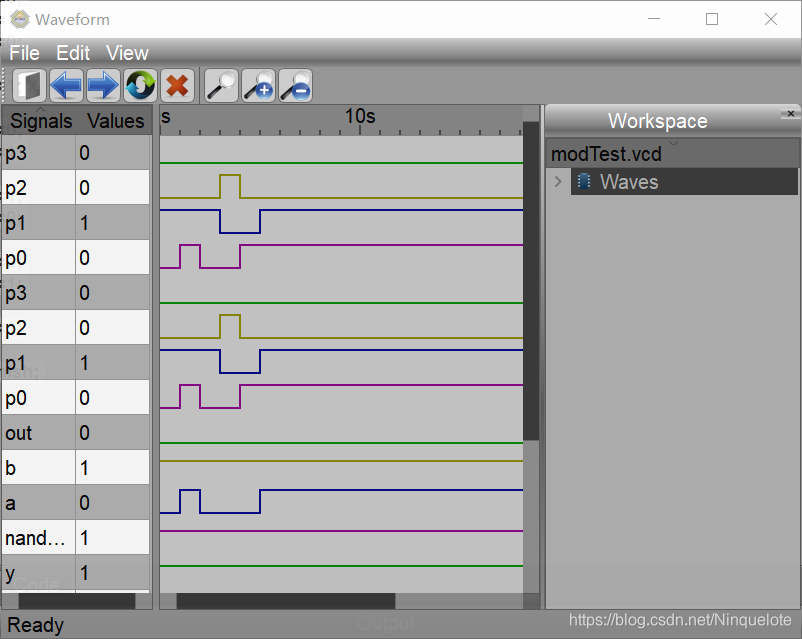

initial begin

p0=0;

p1=1;

p2=0;

#1

p0=1;

#1

p0=0;

p1=1;

#1

p2=1;

p1=0;

#1

p2=0;

p0=1;

#1

p1=1;

$finish;

end- 保存,编译,仿真

- 查看波形

这是一条成功的分割线

不过这个目前还是属于组合逻辑,没有时钟信号,并且还没有开始自主编程,还是以Robei EDA 提供的现成模块为主。

所以下一次,试试时序逻辑吧~冲鸭!