定义:

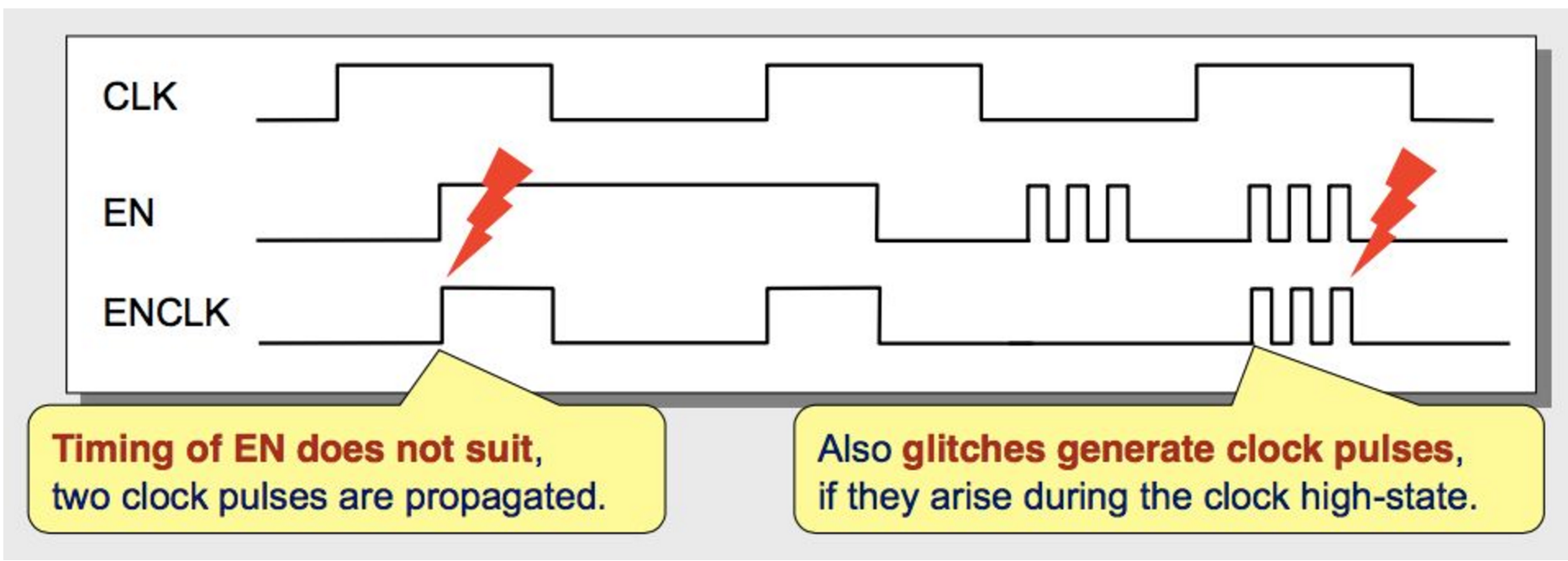

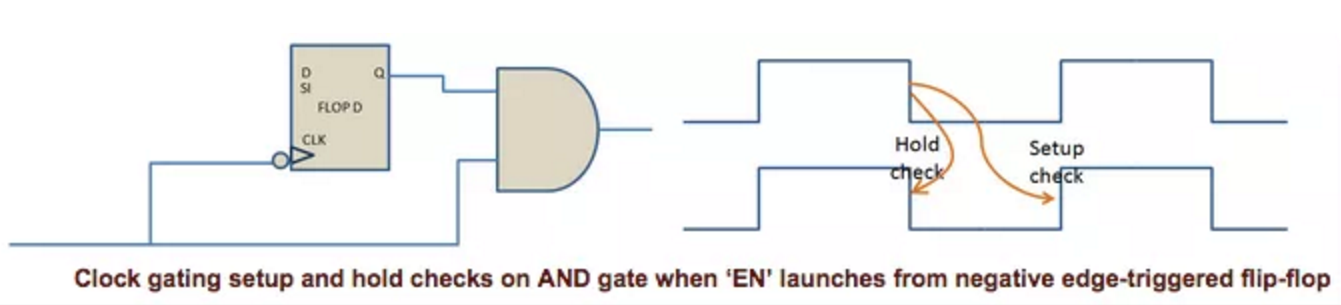

clock gating check是约束的一种,可以用户显示设置,也可由工具推断,目的是保证穿过clock gating cell的clock 没有glitch 且波形不被削切。下面是一个【反例】左侧clock波形被削切,右侧有glitch 穿过。由clock gating的结构可知,大部分clock gating check 都可以归类到AND type clock gating check 或 OR type clock gating check.另类的由XOR跟MUX。

AND type clock gating check:

即高电平有效clock gating check, 当enable 信号为"1" 时,门控打开,clock 『流过』gating cell. 当enable 信号为"0" 时,门控关闭,任由输入clock 呼天喊地,输出都是一片死寂。

对于AND type clock gating cell, enable 信号必须在clock 为低时翻转,才能保证输出clock 没有glitch 且波形不被削切。

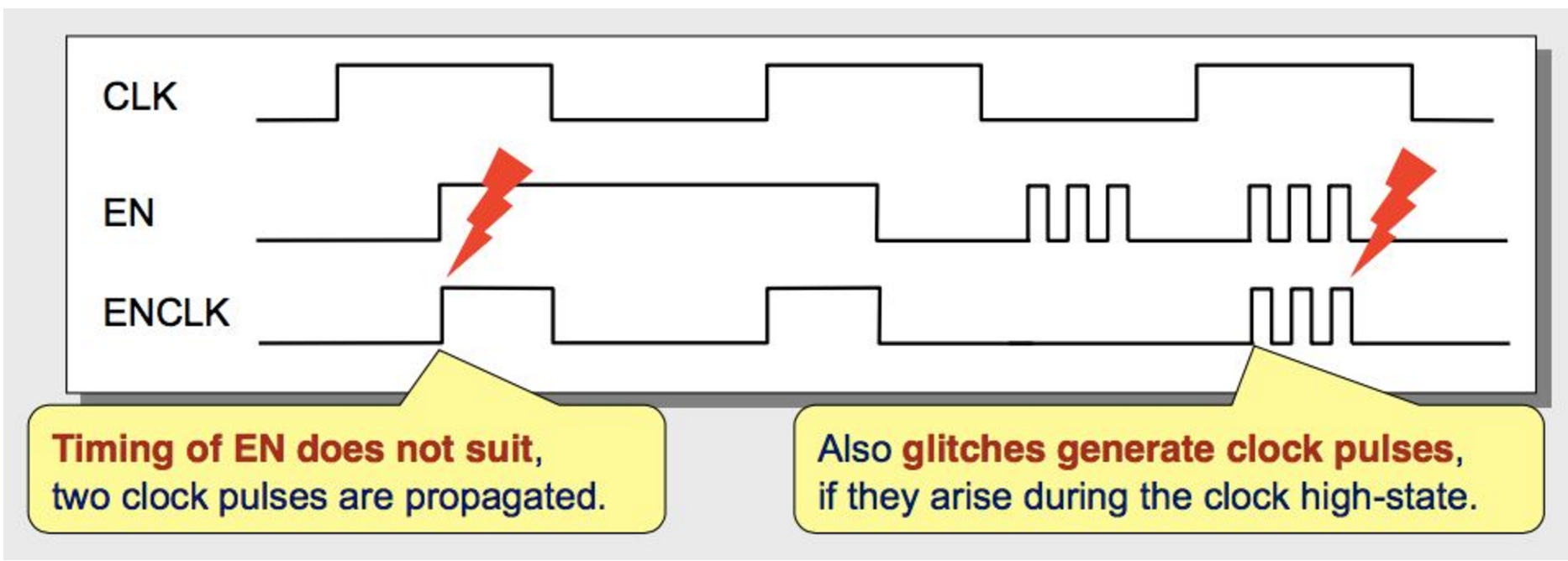

理论上讲,enable 信号即可来自上沿触发的寄存器也可来自下沿触发的寄存器,但如果是来自上沿触发的寄存器,那么hold 将会是半cycle check, 会比较难meet.

而如果enable 信号来自下沿触发的寄存器,那么hold 是0-cycle check, setup 成了半cycle check。这也是为什么AND type ICG cell 内部通常是一个下沿触发的寄存器/低电平有效的latch + 一个与门/与非门的原因。

OR type clock gating check:

与AND type clock gating 相对,即低电平有效clock gating check, 当enable 信号为"0" 时,门控打开,clock 『流过』gating cell. 当enable 信号为"1" 时,门控关闭。

对于OR type clock gating cell, enable 信号必须在clock 为高时翻转,才能保证输出clock 没有glitch 且波形不被削切。

理论上讲,enable 信号即可来自上沿触发的寄存器也可来自下沿触发的寄存器,但如果是来自下沿触发的寄存器,那么hold 将会是半cycle check, 会比较难meet.

而如果enable 信号来自上沿触发的寄存器,那么hold 是0-cycle check, setup 成了半cycle check。这也是为什么OR type ICG cell 内部通常是一个上沿触发的寄存器/高电平有效的latch + 一个或门/或非门的原因。

Inferring Clock gating check:

在做STA 分析时,除了到ICG cell 的clock gating check, 通常都会有很多到组合逻辑cell 的clock gating check, 这些clock gating check 大都是工具自己推断所得。只有搞清楚工具是根据什么原则推断clock gating check, 再结合实际电路,才能确定哪些clock gating check 是真实的哪些又是多余的。

clock gating check 是以clock 为参考来约束enable 信号,所以clock 跟enable 信号是工具推断clock gating check 的基本对象。通常,一个cell 如果满足如下条件,工具便会对该cell 做clock gating check.

Clock pin:

-

有clock 传播到该pin 上;

-

这个clock 必须是有效clock,所谓有效clock 指clock 穿过这个gating cell 后会传到寄存器的CK pin 或会驱动ouput/inout port 或做为某个generated clock 的master clock. 除此之外都不算有效clock, 如某个clock 传过gating cell 后传播到寄存器的数据端,则该clock 不算有效clock.

-

跟gating pin 都会达到该cell 的同一个output, 即clock pin 跟 gating pin 都有到该cell 同一个output pin 的timing arc.

Gating pin:

-

跟clock pin 都会达到该cell 的同一个output, 即gating pin 跟 clock pin 都有到该cell 同一个output pin 的timing arc.

-

必须没有有效clock 传播到该pin 上。

Other:

-

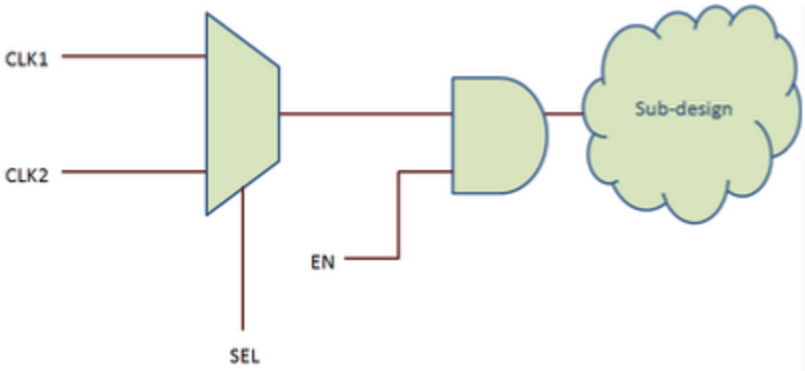

目前大部分工具都不能自动推断出复杂cell 的clock gating check, 如MUX 或XOR.

-

对于复杂cell 如果要做clock gating check, 用户可以用命令set_clock_gating_check 设置。

-

如果用户用set_clock_gating_check 设置的clock gating check 跟工具推断出的clock gating check 的类型不一致,工具通常会报警告,并且以用户的设置做check.

-

用set_clock_gating_check 设置的setup/hold 值要比library 中定义的值优先级高。

-

用命令set_disable_clock_gating_check 可以disable 掉某些不需要做的clock gating check.