此篇文章中涉及的新指令如下:

数量 助记符 说明 字节数 执行时间 指令代码

93,SUBB A,Rn 累加器内容减去寄存器内容(带借位) 1 1 98H-9FH

94,SUBB A,@Ri 累加器内容减去间接寻址RAM中的内容(带借位) 1 1 96H-97H

95,SUBB A,#data 累加器内容减去立即数(带借位) 2 1 84H,data

96,INC A 累加器内容增1 1 1 04H

97,INC @Ri 间接寻址RAM中的内容增1 1 1 06H-07H

98,DEC A 累加器的内容减1 1 1 14H

99,DEC driect 直接寻址字节中的内容减1 2 1 15H,driect

100,DEC @Ri 间接寻址RAM中的内容减1 1 1 16H-17H

101,CJNE A,direct,rel 直接寻址中的内容和累加器中的内容进行比较,不等则跳转 3 2 B5H,direct,rel

102,JBC bit,rel 直接寻址位为1则转移然后将其清零 3 2 10H,rel

103,ANL direct,A 累加器内容逻辑与到直接寻址字节中 2 1 52H,direct

104,ANL direct,#data 立即数逻辑与到直接寻址字节中 3 1 53H,direct,data

105,ORL A,direct 直接寻址字节逻辑或到累加器A中 2 1 45H,direct

106,ORL A,@Ri 间接寻址RAM中的内容逻辑或到累加器A中 1 1 46H-47H

107,ORL direct,A 累加器中的内容逻辑或到直接寻址字节中 2 2 42H,direct

108,XRL A,direct 直接寻址字节逻辑异或到累加器A中 2 1 65H,direct

109,XRL A,#data 立即数逻辑异或到累加器A中 2 1 74H,data

110,XRL direct,A 累加器中的内容逻辑异或到直接寻址字节中 2 1 62H,direct

111,XRL direct,#data 立即数逻辑异或到直接寻址字节中 3 2 63H,direct,data

题28

编写双字节减法,要求:被减数放在内部RAM的60H(高字节),61H单元中,减数放在内部RAM的62H(高字节),63H中,运算结果存放在60H,61H中,借位放在位寻址区的00H位。

程序源码:

CYBIT BIT 00H

ORG 0000H

LJMP START

ORG 0030H

START:

MOV 60H,#17H

MOV 61H,#25H

MOV 62H,#25H

MOV 63H,#25H;FOR TESTING

MOV R7,#00H

MOV R0,#60H

MOV R1,#62H

CLR C

MOV A,@R0

SUBB A,@R1

MOV @R0,A

JC L1

INC R0

AJMP L2

L1:

INC R0

MOV A,@R0

SUBB A,R7

MOV @R0,A

L2:

INC R1

MOV A,61H

SUBB A,@R1

MOV @R0,A

JC L3

AJMP HALT

L3:

MOV CYBIT,C

HALT:

SJMP HALT

END

题29

编写程序算法,要求:内部60H中的数据屏蔽其高四位,内部61H中的数据屏蔽其低四位,内部62H中的第一位数据取反,内部63H中的数据取反,内部64H中的数据加2。

程序源码:

ORG 0000H

LJMP START

ORG 0030H

START:

MOV 60H,#17H

MOV 61H,#25H

MOV 62H,#29H

MOV 63H,#31H

MOV 64H,#51H

MOV R0,#63H

CLR A

PUSH ACC

MOV A,#0F0H

ANL 60H,#0FH

ANL 61H,A

POP ACC

INC A

INC A

PUSH ACC

ADD A,64H

XCH A,64H

POP ACC

DEC A

XRL A,62H

XCH A,62H

XRL 63H,#0FFH

HALT:

SJMP HALT

END

题30

设A中内容不为0,内部RAM中地址为60H中存有一个数,试编程将60H中的内容逻辑或到A中,再判断其1的个数,若A中的个数为奇数个,则内部RAM地址为61H中的内容减1,若为偶数个,将A中内容减2存放在其61H中。

程序源码:

RESULT EQU 61H

ORG 0000H

LJMP START

ORG 0030H

START:

MOV 60H,#29H

MOV A,#53H

MOV 61H,#10H

;FOR TESTING

MOV R1,#RESULT

MOV R0,#60H

ORL A,@R0

JB P,L1

CLR C

SUBB A,#02H

MOV RESULT,A

AJMP HALT

L1:

DEC @R1

HALT:

SJMP HALT

END

扩展:

试编程将60H,61H中的内容进行逻辑异或后送61H中再判,断其1的个数,若其中的个数为偶数个,则内部RAM地址为61H中的内容减1,若为奇数个,将60H中内容与0FH异或后存放在外部RAM的0100H中。

程序源码:

RESULT EQU 0100H

ORG 0000H

MOV 60H,#29H

MOV 61H,#11H

;FOR TESTING

MOV DPTR,#RESULT

MOV R0,#60H

MOV A,@R0

XRL 61H,A

MOV A,61H

JNB P,L1

XRL A,#0FH

MOVX @DPTR,A

AJMP HALT

L1:

DEC 61H

HALT:

SJMP HALT

END

题31

编写双字节加法,要求:被加数放在外部RAM的60H(低字节)、61H单元中,加数放在内部RAM的62H(高字节)、63H中,运算结果存放在内部RAM的62H(高字节)、63H中,进位放在R1中的内容指向的地址中。

程序源码:

ADD1 EQU 0060H

ADD2 EQU 63H

ORG 0000H

MOV SP,#25H

MOV R1,#2AH

LCALL ADDProgram

SJMP $

ORG 0030H

ADDProgram:

MOV 62H,#9AH

MOV 63H,#41H

MOV DPTR,#ADD1

MOV A,#0E8H

MOVX @DPTR,A

INC DPTR

INC A

MOVX @DPTR,A

;FOR TESTING

MOV R0,#ADD2

MOV DPTR,#ADD1

CLR C

CLR A

MOV @R1,#00H

MOVX A,@DPTR

ADDC A,@R0

MOV @R0,A

DEC R0

INC DPTR

MOVX A,@DPTR

ADDC A,@R0

MOV @R0,A

JNC HALT

INC @R1

HALT:

RET

END

扩展:

编写双字节加法,要求:被加数放在内部RAM的60H(低字节)、61H单元中,加数放在内部RAM的62H(低字节)、63H中,运算结果存放在内部RAM的64H(高字节),65H中,进位存放在内部RAM地址66H的单元中且累加器A中的内容赋值为1。

程序源码:

ORG 0000H

MOV SP,#25H

LCALL ADDProgram

SJMP $

ORG 0030H

ADDProgram:

MOV 60H,#9AH

MOV 61H,#41H

MOV 62H,#9BH

MOV 63H,#48H

;FOR TESTING

MOV R0,#60H

MOV R1,#62H

MOV 66H,#00H

MOV 64H,66H

MOV 65H,64H

CLR C

CLR A

MOV A,@R0

ADDC A,@R1

ORL 65H,A

INC R0

INC R1

MOV A,@R1

ADDC A,@R0

ORL 64H,A

MOV A,#01H

JNC HALT

ORL 66H,A

HALT:

RET

END

题32条件赋值程序

在内部RAM地址为24H中存有一个数,试编写程序根据24H中的第零位进行赋值程序,赋值规则如下:

若(24H.0)=1,则给内部RAM地址为60H开始的连续10个字节单元递增(增量为1)赋值(赋值的内容存放在5FH中),然后清除24H中的第零位数据,(24H.0)=0,则不做任何操作。

程序源码:

IFBIT BIT 24H.0

ORG 0000H

MOV 5FH,#10H

SETB IFBIT

;FOR TESTING

MOV SP,#70H

MOV R7,#10

MOV R0,#60H

CLR A

JBC IFBIT,L1

SJMP HALT

L1:

MOV A,5FH

LOOP:

MOV @R0,A

INC R0

INC A

DJNZ R7,LOOP

HALT:

SJMP HALT

END

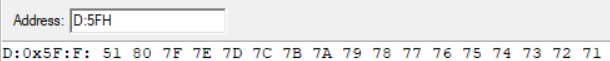

仿真图:

扩展:

比较外部RAM地址为100H和内部RAM地址为5FH中的内容:

若相等,则给内部RAM地址为60H开始的连续10H个字节单元递减(每次赋值数据减1)赋值(赋值的内容存放在5DH中),

若不等,则不做任何操作。

程序源码:

IFBYTE BIT 0100H

ORG 0000H

MOV DPTR,#IFBYTE

MOV A,#51H

MOV 5DH,#80H

MOVX @DPTR,A

MOV 5FH,A

;FOR TESTING

MOV DPTR,#IFBYTE

MOV SP,#70H

MOV R7,#10H

MOV R0,#60H

CLR A

MOVX A,@DPTR

CJNE A,5FH,HALT

MOV A,5DH

LOOP:

MOV @R0,A

INC R0

DEC A

DJNZ R7,LOOP

HALT:

SJMP HALT

END

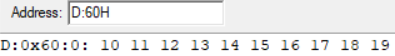

仿真图: