文章目录

1.项目要求

功能要求:

- 串口发送 数据和写指令给 FPGA 来控制 SDRAM 写操作。

- 串口发送 读指令给 FPGA 来控制 SDRAM 读操作,并将数据返回到FPGA。

2外设选取

- PC与FPGA通信需要哪种方式:原理:主要看速率比较,看他是否属于高速。uart、以太网…

串口

SDRAM

3外设如何实现功能(数据手册)

- 通过数据手册看如何实现需要的功能。

- 如果有多个操作可能 起冲突:可以引入仲裁模块:来判断优先执行那个操作、

- 看时钟选取多大,相位:是否引入PLL 差分时钟

- 看接口通信速率:是否速率不匹配 引入rdy、fifo

串口:实现发送、接收数据

功能分析

通过串口的协议分析:

FPGA根据协议,建立以上时序图,从串口助手连续接收 1字节数据。

串口助手根据,FPGA建立的时序,和协议比对,连续接收 1字节数据。

就可以实现串口发送接收数据功能。

时钟分析

可以选取50M 100M 。。。

通信速率分析

5208个时钟

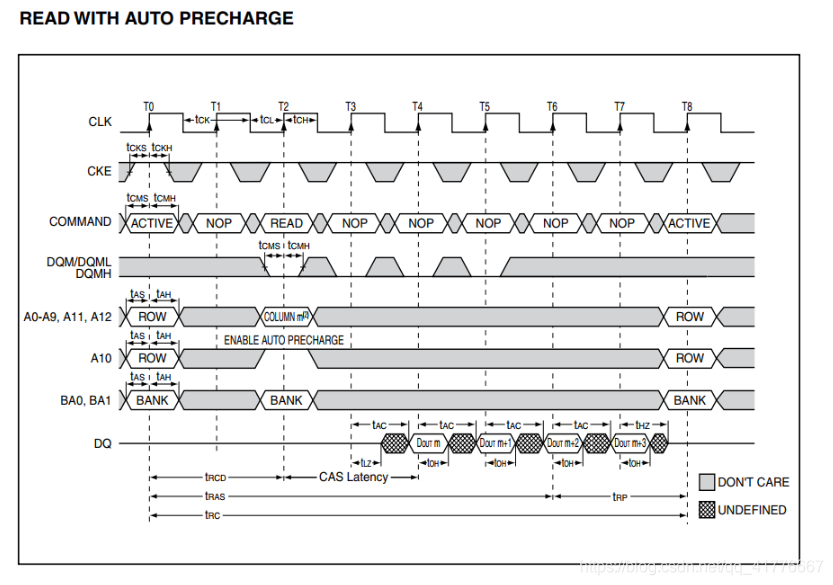

SDRAM:读写数据功能

功能分析

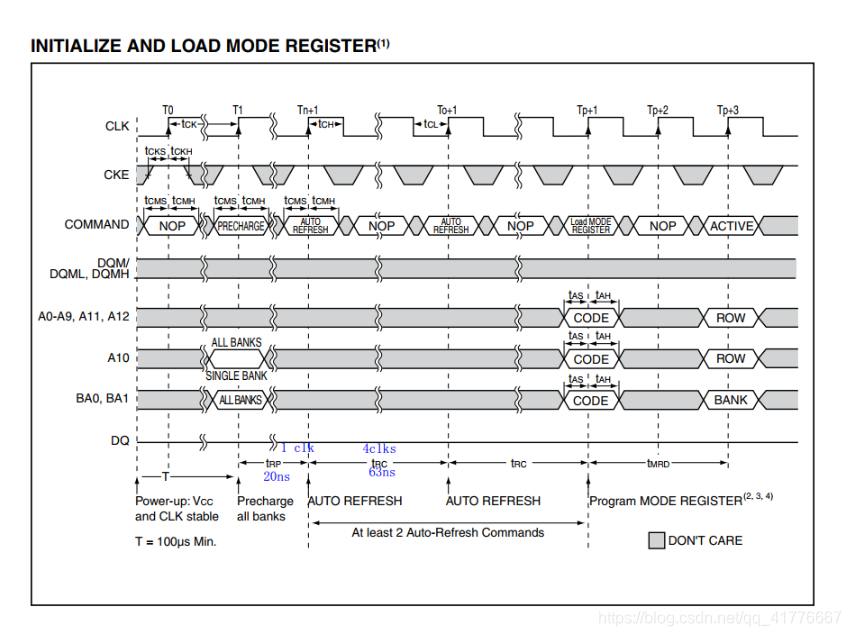

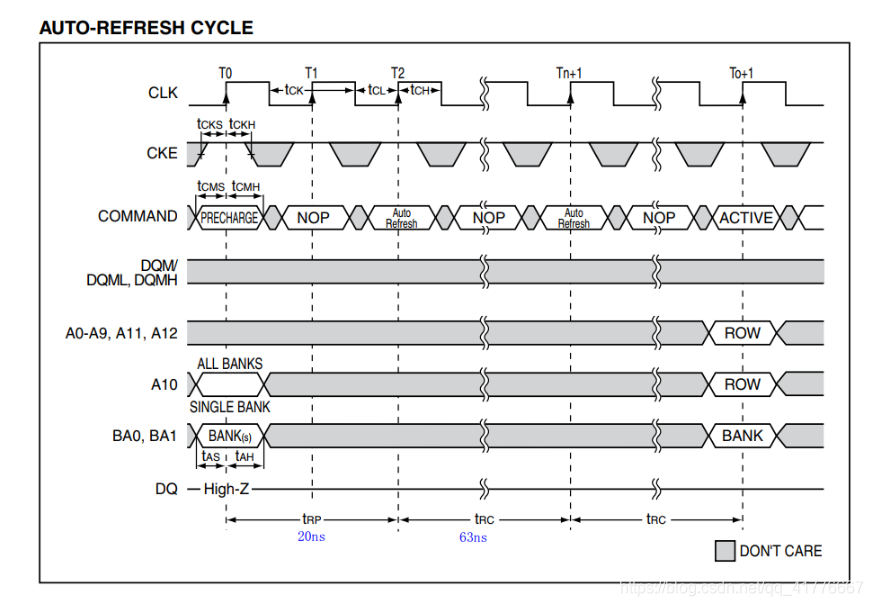

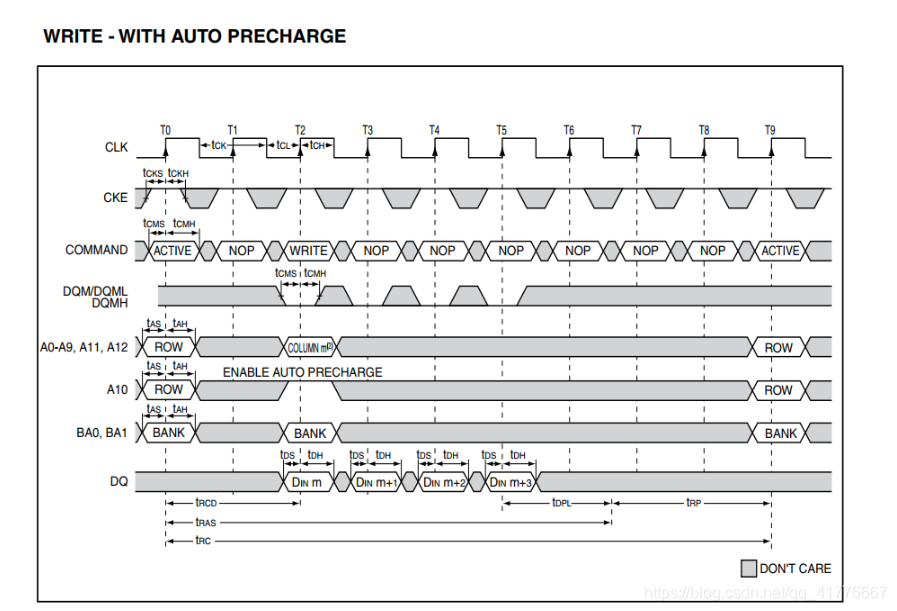

通过SDRAM接口协议:需要完成 初始化操作、自刷新操作、写操作、读操作功能。才能通过SDRAM实现读写数据。

多时序冲突(引入仲裁模块)

每15.625us需要进行自刷新。由于2个时序操作可能有冲突所以我们需要引入仲裁模块:让不同时序操作不起冲突。

时钟选取

采取差分时钟 100M 100M相位180度,所以引入PLL模块

通信速率

100M,所以引入fifo后续讨论

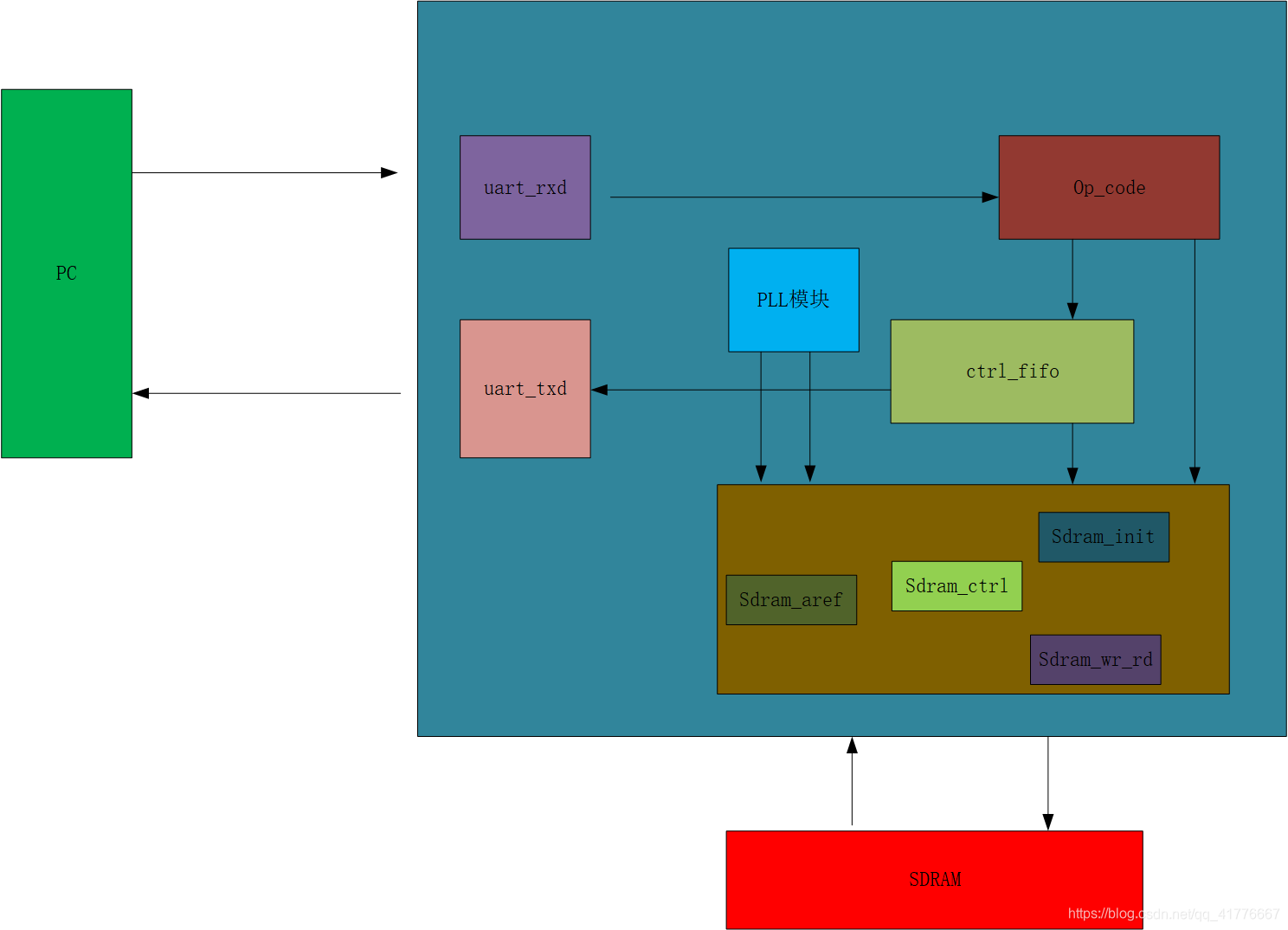

4.接口模块设计

接口模块根据功能是否需要继续划分

-

uart模块:由于需要完成发送和接收模块所以分成

串口发送模块:uart_rxd din:bit ; dout:byte

串口接收模块:uart_txd din:byte ; dout:bit

-

SDRAM模块:需要完成初始化操作、自刷新操作、写操作、读操作功能、仲裁模块。

初始化模块:sdram_init din:byte ; dout:byte

自刷新模块 :sdram_arf din:byte ; dout:byte

写操作模块:sdram_write din:byte ; dout:byte

读操作模块:sdram_read din:byte ; dout:byte

仲裁模块:sdram_ctrl din:byte ; dout:byte

接口是否涉及寄存器配置

- 项目中有某些外设,上电工作前需要进行配置才能按要求工作。因此需要对外设内部寄存器进行读写,这一流程是通过FPGA来进行配置。

- 使用MDY推荐的模块寄存器配置结构:寄存器配置表模块**+**寄存器读写模块+时序接口模块

SDRAM不需要进行配置

5.内部模块的划分步骤

译码模块(指令系统:操作码+数据格式)

- 上位机,例如PC,ARM,DSP或者其他的器件,只涉及到一个接口,但是却有很多指令或者命令功能要发送,因此就需要一个指令系统。

- 指令系统一定会涉及到命令、地址和数据。这种情况,肯定会有一个“寄存器解析模块”,根据命令、地址和数据,改变相应的寄存器的值。

因为需要对指令进行译码所以要添加

译码模块:op_code 产生读、写触发信号,输出数据

添加功能模块

功能基本都实现了

根据模块匹配原则添加模块

- 模块与模块之间数据位宽是否匹配。一般添加 bit_byte衔接模块

- 模块与模块之间通信速率是否匹配。要加上RDY信号或者FIFO,一般都是数据多次重复发送需要考虑rdy和FIFO

- 考虑是否涉及多路进一路出,要用FIFO

- 选择何种fifo:同步fifo (noraml 模式 show ahead模式) 异步fifo(noraml 模式 show ahead模式)输入、输出时钟

根据通信速率原则发现:

串口接收速率明显小于SDRAM(100M速率),所以采用

写FIFO模块:wr_fifo

先把数据存储起来,等到SDRAM需要数据再读取出来。

同理串口发射也是,需要

读FIFO模块:rd_fifo ,由于写时钟100M相位差180(后续文档讨论)读时钟(uart:50M),所以用异步fifo。

FIFO先把sdram读出来的数据存起来再通过串口发送过去。

综上

wr_fifo: wr_clk:50M rd_clk:100M

rd_fifo: wr_clk:100M(相位差π) rd_clk:50M

6、模块框架

初始模块框架

模块优化设计

- 架构相同或者类似用一个模块设计

wr_fifo 和 rd_fifo 可以用ctrl_fifo 模块

sdram_write 和 sdram_read 架构设计类似采用 sdram_wr_rd模块

7、项目细分

1.uart串口回环实验:串口发送256个数据给FPGA,存储到FIFO,存满及时返回256个数据 。代码设计、testbench、modelsim仿真

2.SDRAM的四个模块进行代码设计、testbench、modelsim仿真

3.整体项目实现:代码设计、testbench、modelsim仿真

8、自我答疑

代码已经功能实现,后续文档继续撰写。

9、学习总结

学习明德扬架构觉得非常有用,本文采取明德扬模块架构设计,有需要对明德扬开发板和培训课程了解可以加群,一起探讨。或者本人qq:1602453603。

创作不易,认为文章有帮助的同学们可以关注、点赞、转发支持。对文章有什么看法或者需要更近一步交流的同学,可以加入下面的群: