第四章 时序逻辑设计

引言

1.时序逻辑电路

- 输出由 当前时刻的输入 和 之前时刻的输入 共同决定

- 电路内部具有 记忆

- 状态/锁存器与触发器(存状态)/同步时序逻辑电路(组合逻辑➕一组表示电路状态的触发器)

2.时序逻辑电路特征

锁存器与触发器

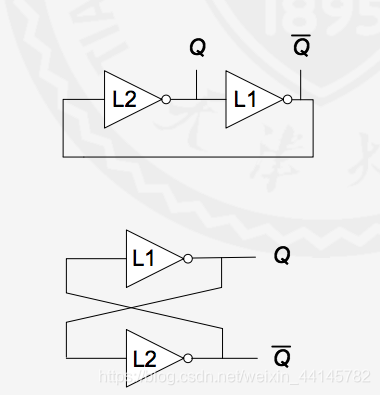

双稳态电路

- 电路存在两种状态(1,0)

- 可存储1比特二进制状态,但是没有输入端,无法控制电路中存储的状态

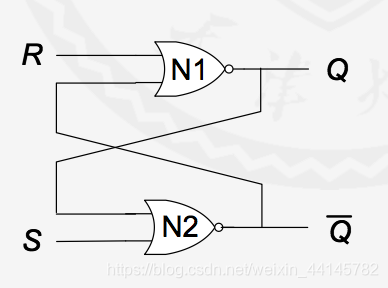

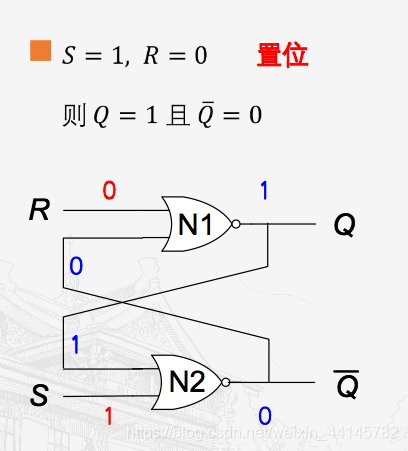

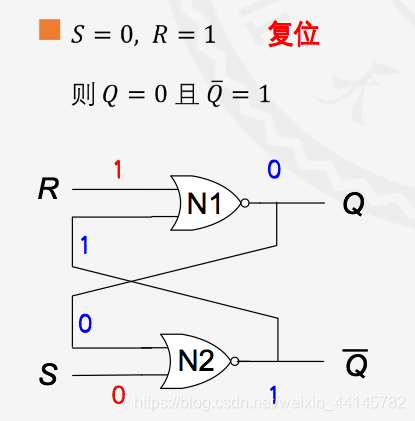

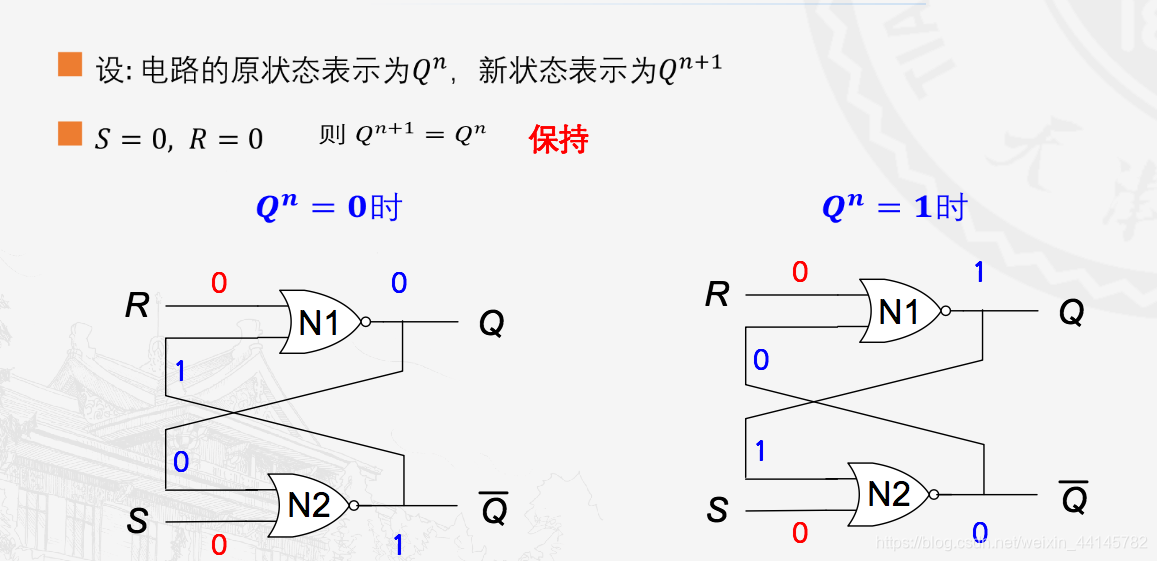

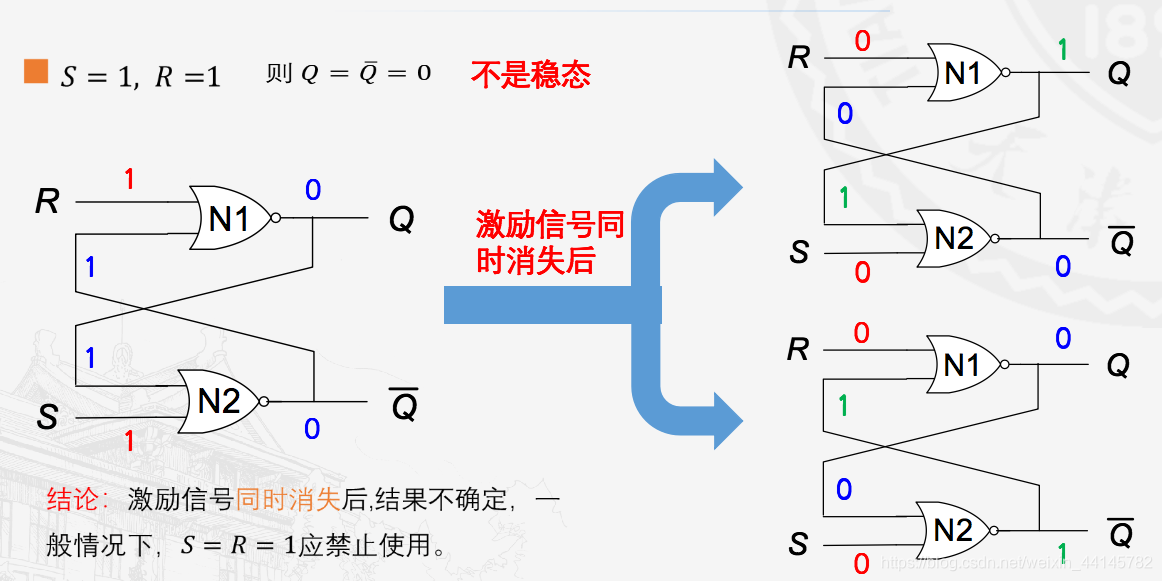

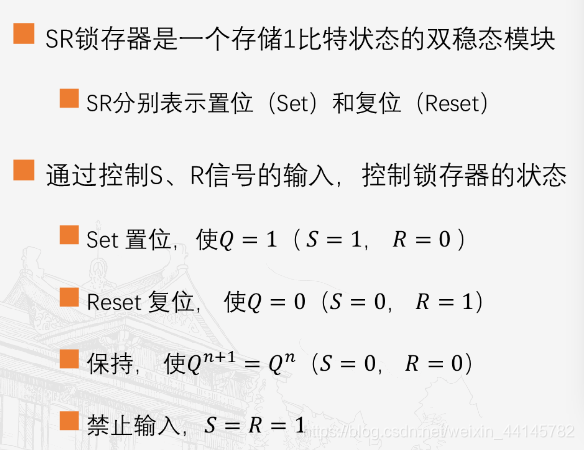

SR锁存器

- 两个输入端(激励信号)

- 两个输出端(状态)

- 四种情况

? SR锁存器总结

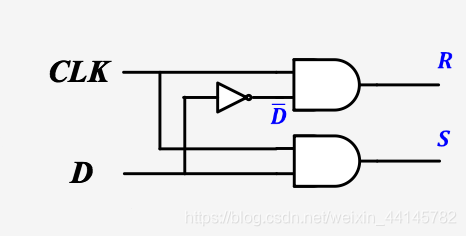

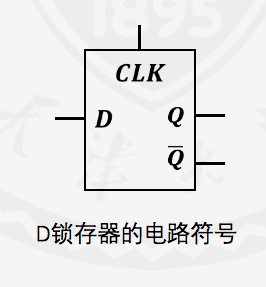

D锁存器

- SR锁存器的基础上升级,修正了SR同时为1时的不稳定状态。

?D锁存器总结

- CLK: 控制锁存器状态发生改变的时间。

- D: 输入数据,控制下一状态的值。

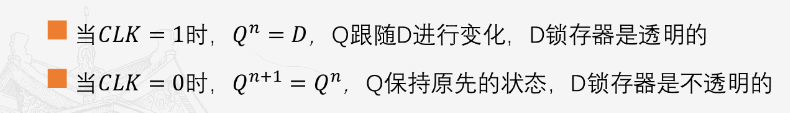

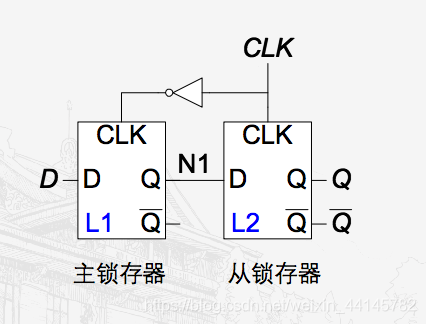

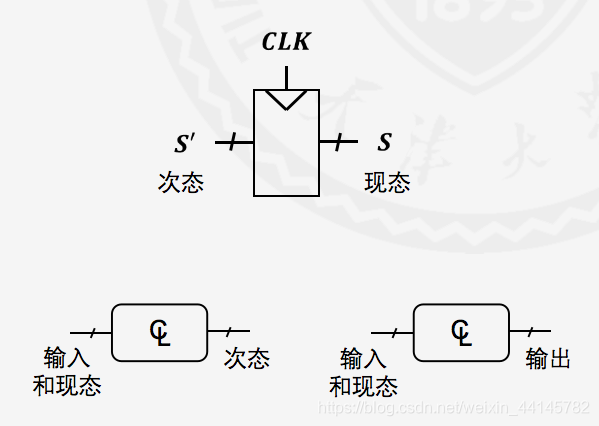

D触发器

-

边沿触发(在CLK的上升沿对D进行采样)

-

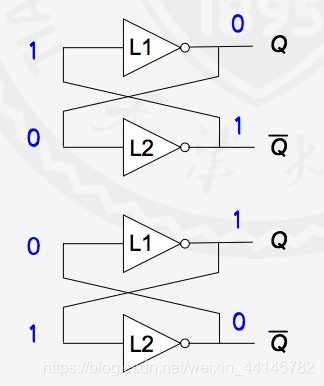

实现(主从式)

- 带使能,置位,复位的D触发器(顾名思义)

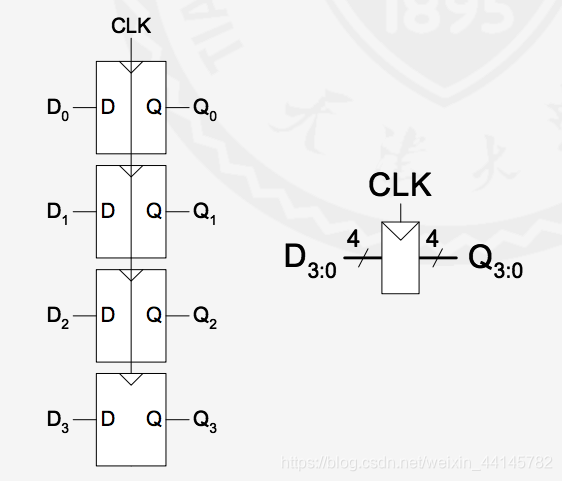

寄存器

- 一个n位寄存器由1个共享CLK的输入和N个D触发器组成

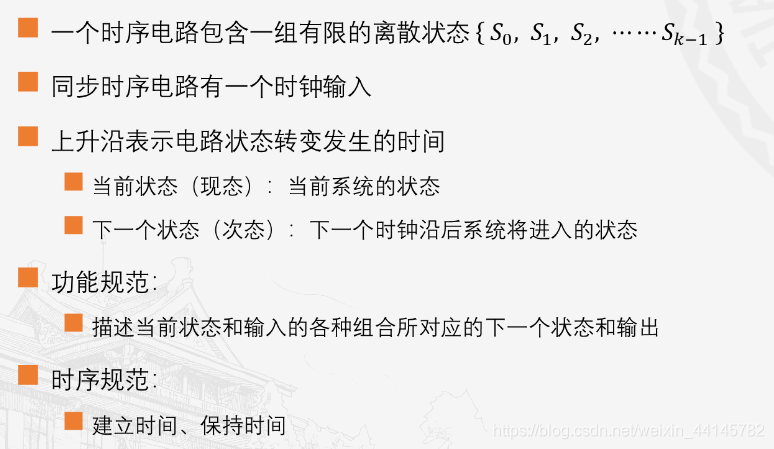

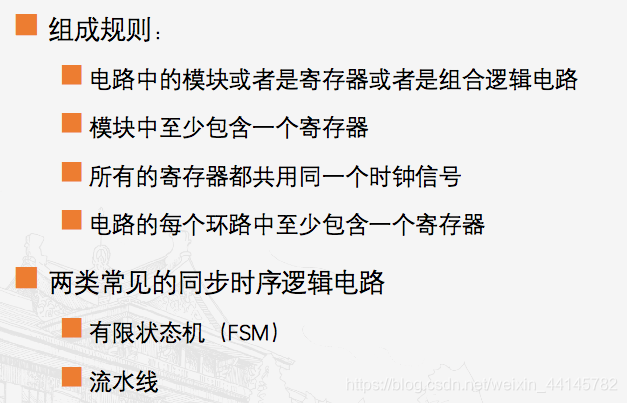

同步逻辑设计

- 所有不是组合逻辑的电路 都称为时序逻辑电路

- 在信号传播路径中插入寄存器,使时序逻辑电路=组合逻辑电路➕寄存器(触发器)

- 状态仅在时钟边缘发生改变 即:状态同步于时钟信号

?同步逻辑设计总结

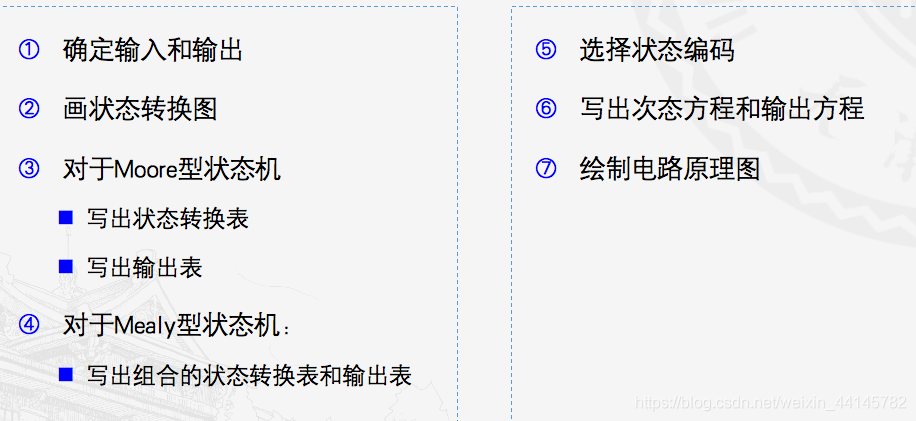

有限状态机

基本概念

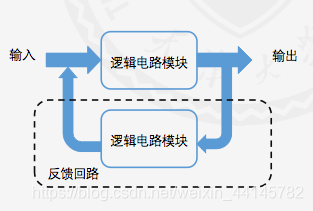

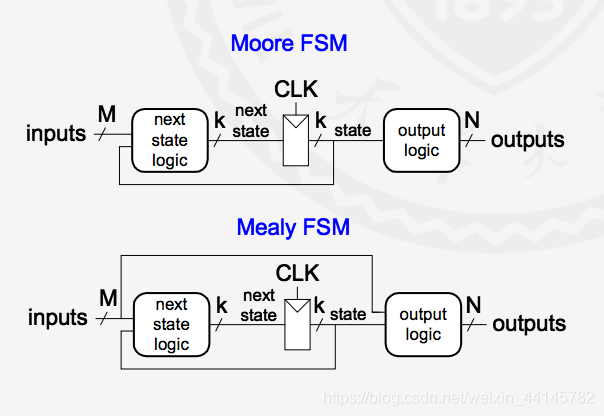

- 由状态寄存器(存储当前状态,状态在时钟沿发成改变)和组合逻辑(计算下一个状态,电路输出)构成

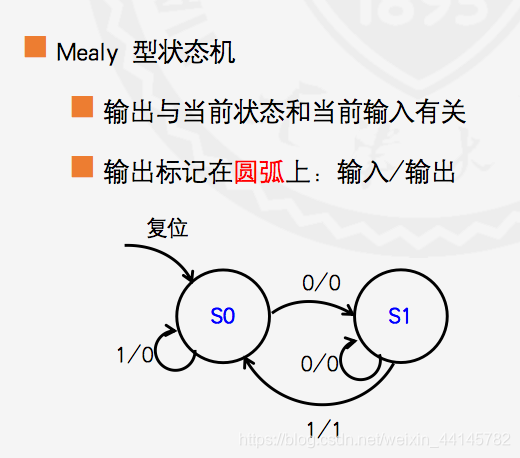

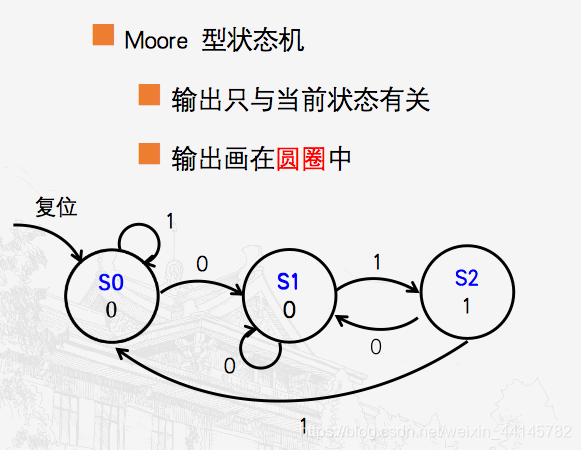

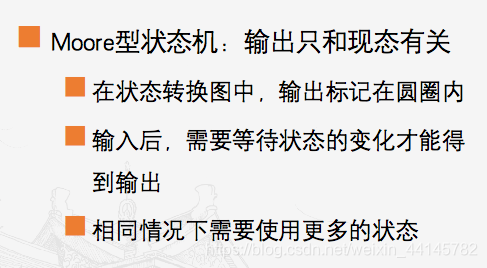

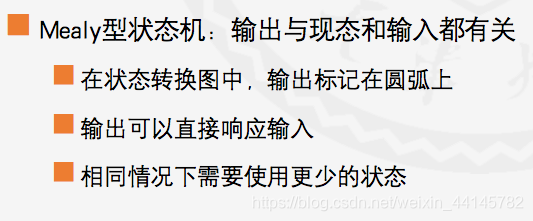

- 两类有限状态机 Moore型(输出仅由当前时刻状态决定) 和 Mealy型 (输出由当前时刻状态和输入共同决定)

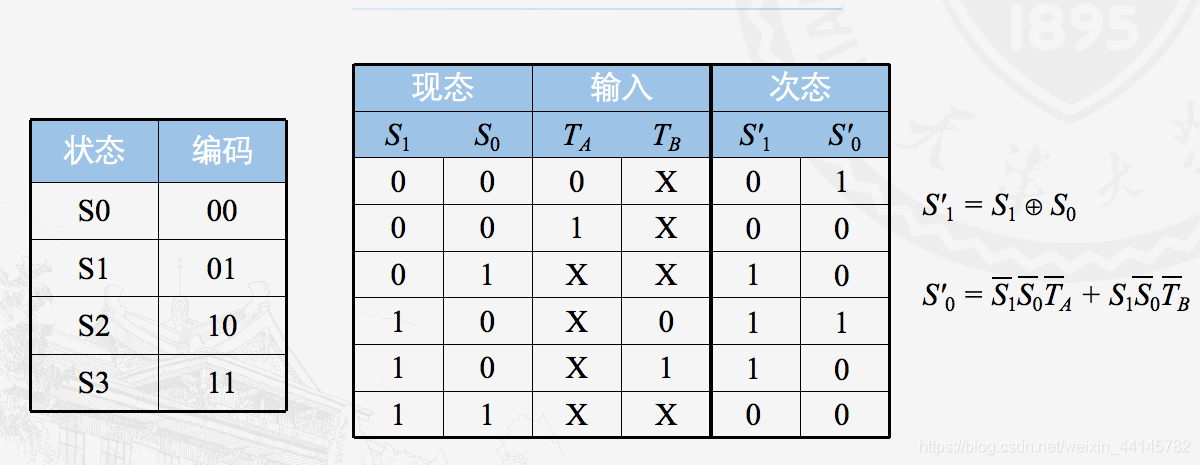

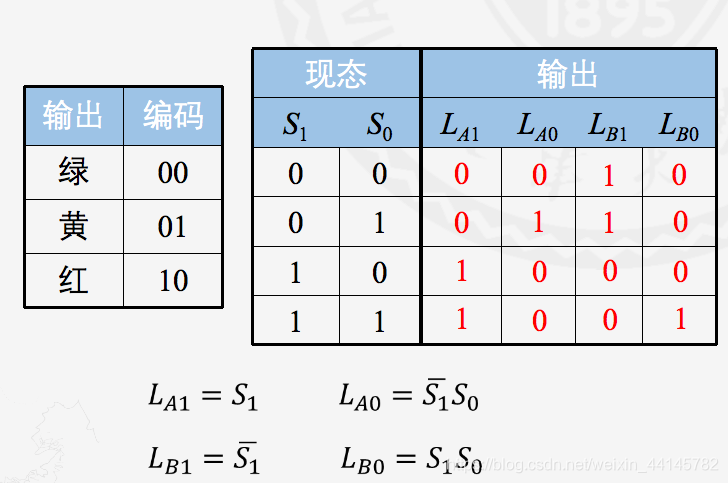

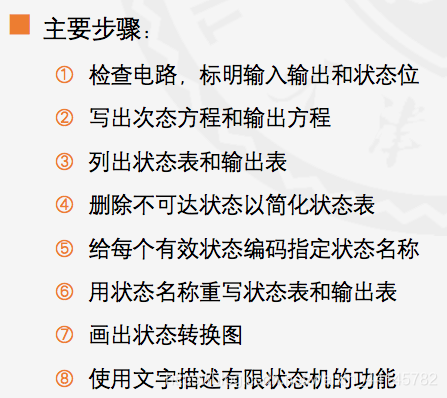

有限状态机设计实例

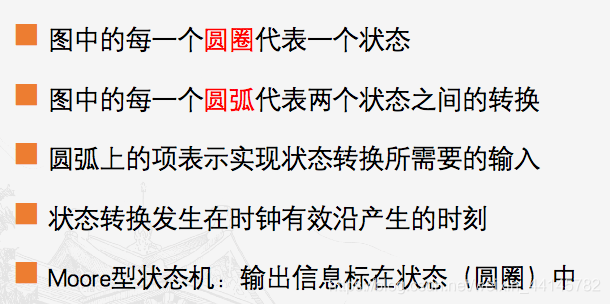

- step1 状态转换图

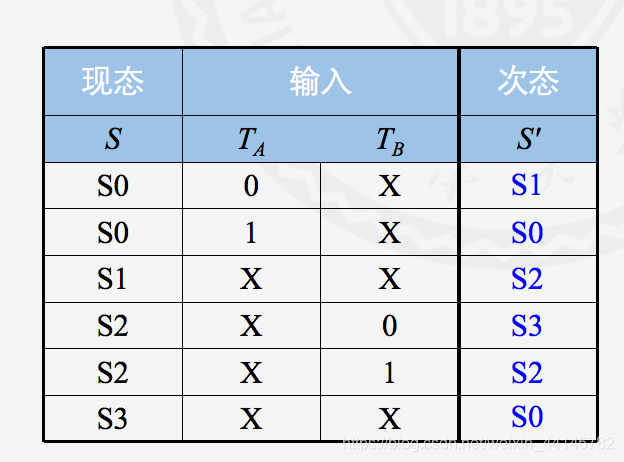

- step2 状态转换表 对状态编码

-

step3 输出表

-

? Moore型有限状态机设计总结

1⃣️根据问题进行抽象,确定输入输出以及对应的逻辑含义

2⃣️画出状态转换图

3⃣️列出状态转换表

4⃣️对状态进行编码,并列出次态方程

5⃣️列出输出表

6⃣️对输出进行编码,并列出输出方程

7⃣️绘制原理图 -

?Mealy 型有限状态机设计总结

1⃣️根据问题进行抽象,确定输入输出以及对应的逻辑含义

2⃣️画出状态转换图

3⃣️列出状态转换表和输出表(可同时列出)

4⃣️对状态和输出进行编码,并列出次态方程和输出方程

5⃣️绘制原理图

状态编码

- 二进制编码(00,01,10,11)

- 独热编码(1000,0100,0010,0001) 需要更多触发器,实现逻辑简单

Moore型状态机和Mealy型状态机

- 例题 ?遇到01就笑(返回1)

- 例题 检测101 (输入为1时电路不复位)

状态机的分解

- 状态机分解,减少复杂度。

由电路图导出状态机

时序逻辑中的时序问题

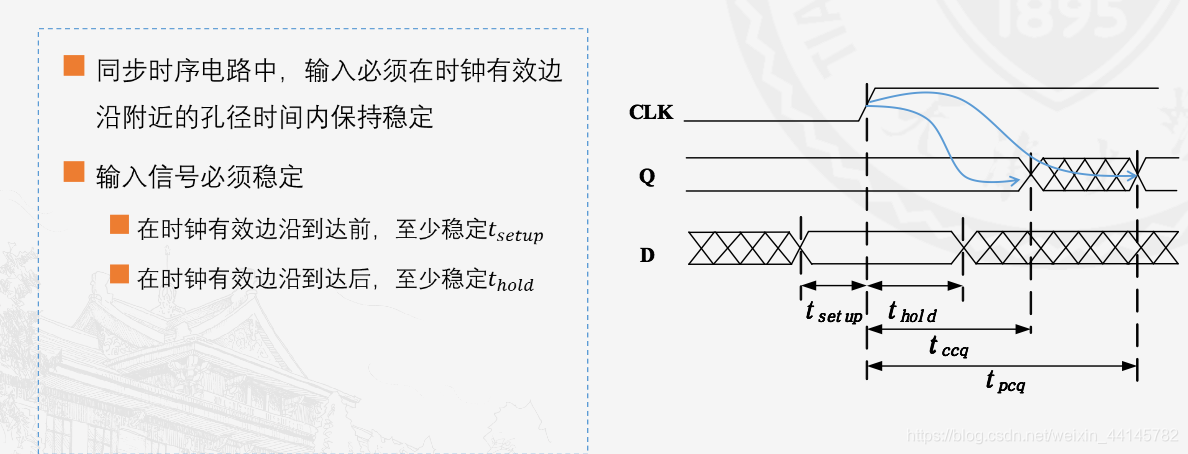

动态约束

- 在时钟有效边沿时对D采样复制给Q,D必须处于一个稳定的状态

- 若采样时D处于未稳定状态,则产生亚稳态

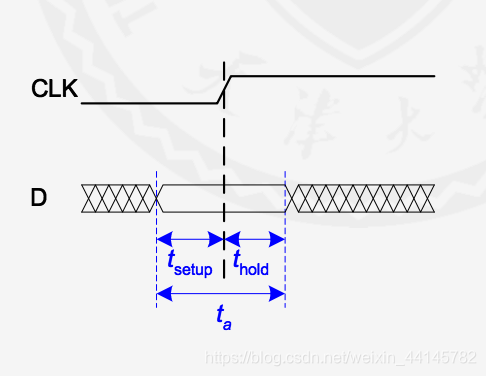

输入时序约束

- 建立时间(setup time) ,保持时间(hold time),孔径时间(aperture time)

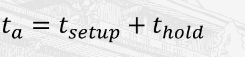

输出时序约束

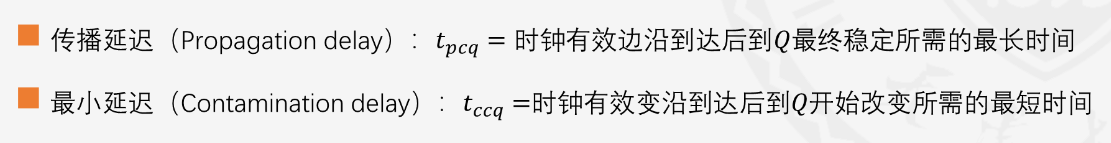

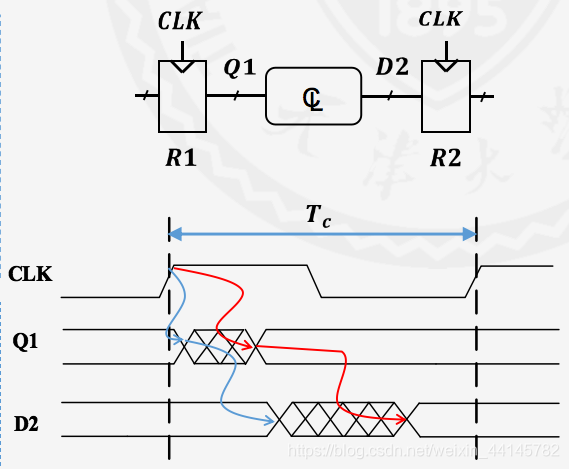

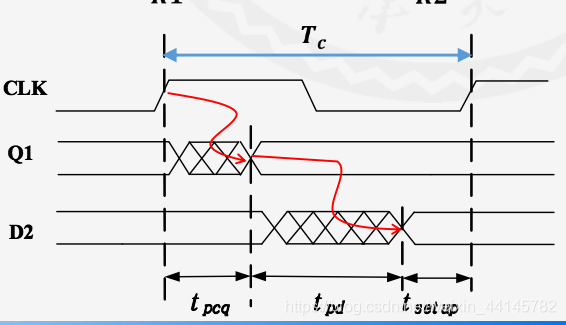

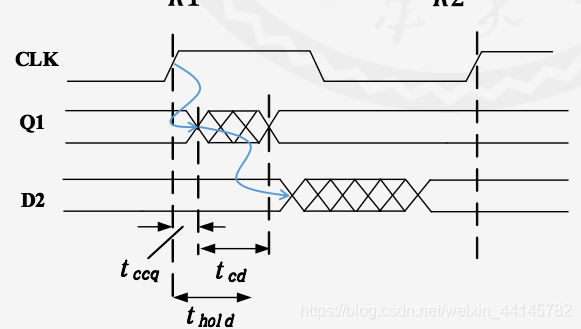

系统时序

-

时钟周期是两个上升沿(下降沿)之间的 间隔

-

时钟频率=1/时钟周期

-

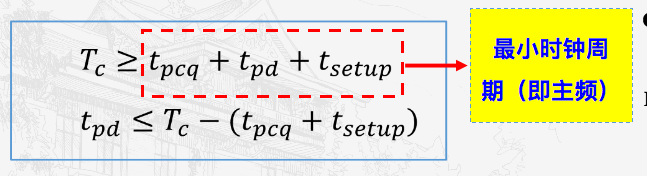

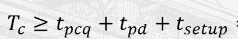

建立时间约束,最大延迟约束

-

只有tpd是人工可以控制的(组合逻辑的传播延迟)

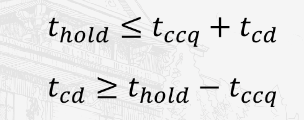

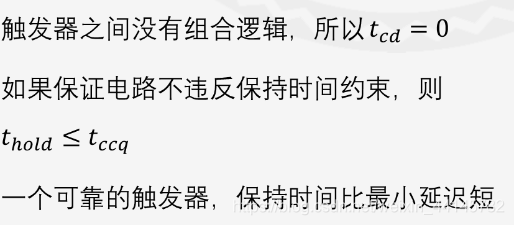

- 保持时间约束,最小延迟约束

总结

- tpcq 触发器的传播延迟 tccq触发器的最小延迟

- 最小延迟cd与最短路径 传播延迟pd与关键路径

时序逻辑模块

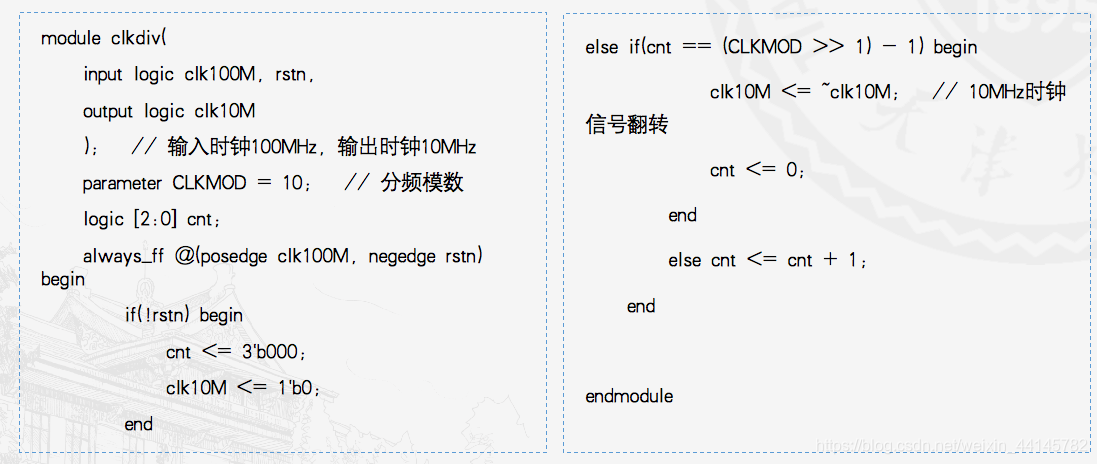

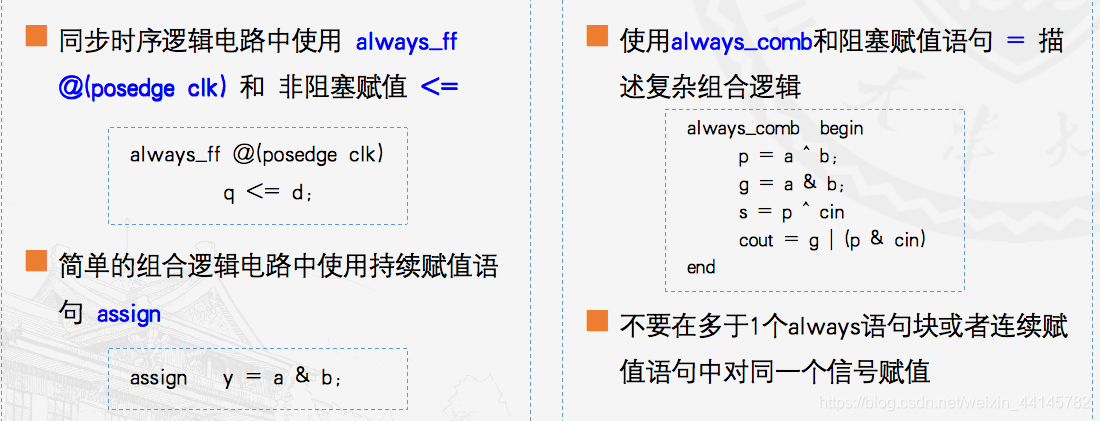

- alway过程块分为三部分: always_comb(组合), always_latch(时序), always_ff(时序)

- 敏感列表:当列表中的事件产生时,过程块中的语句开始工作

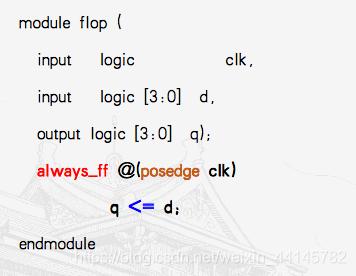

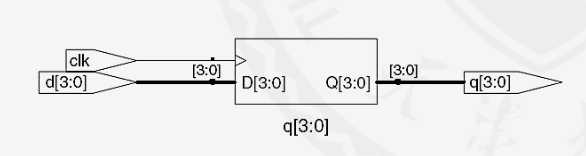

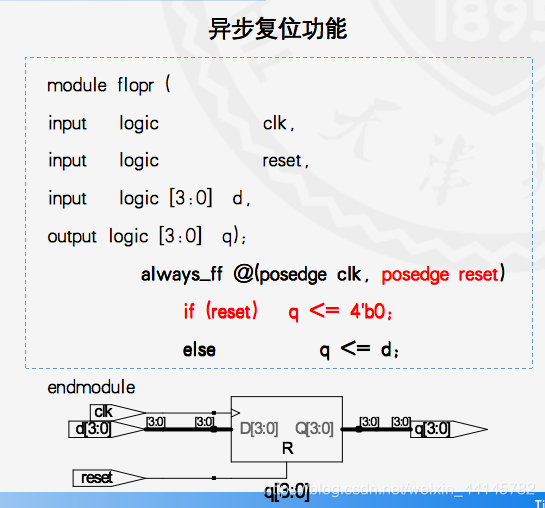

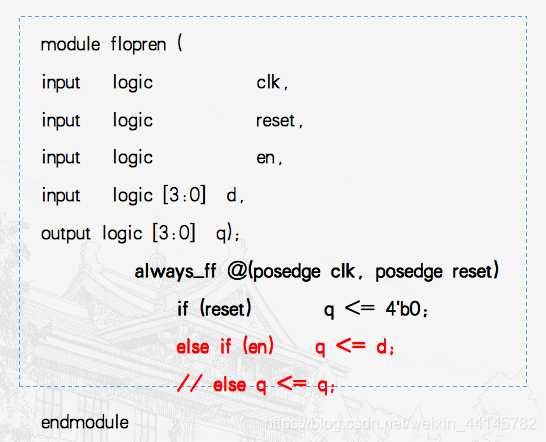

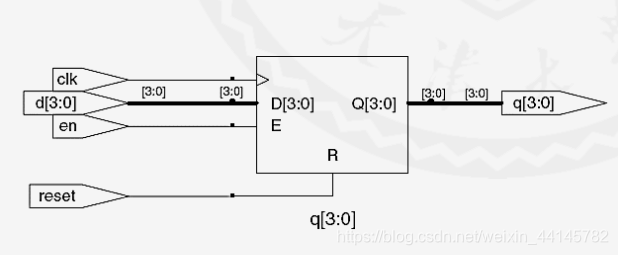

寄存器always_ff

-

寄存器建模

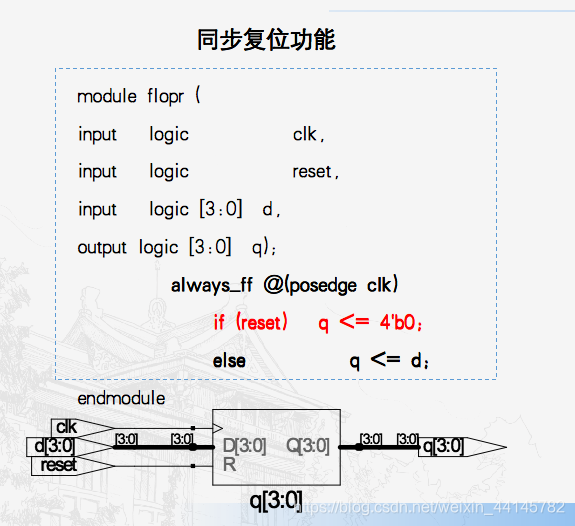

-

带复位的寄存器(推荐使用低电平异步复位寄存器)

- 带使能端的寄存器

锁存器 always_latch

最好别用

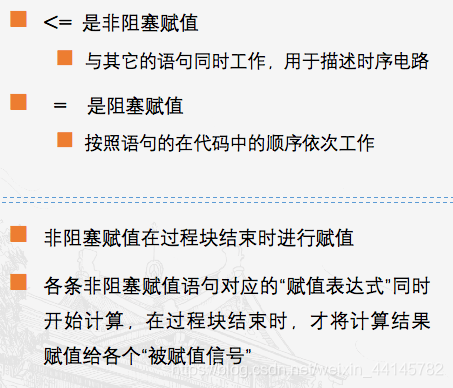

阻塞/非阻塞赋值

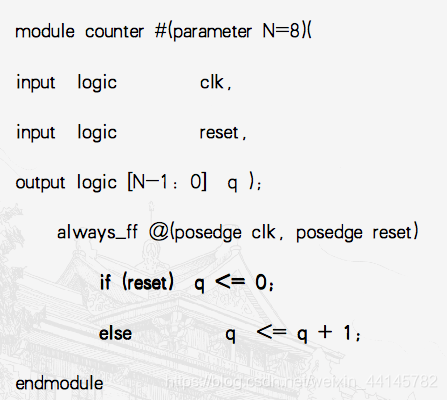

计数器

-

实现循环计数,时钟上升沿到达时结果加一并输出

-

应用 时钟分频器