SPI协议

SPI(Serial Peripheral interface),串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。

是一种高速的,全双工,同步的通信总线,

在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,

正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200.

SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。目前应用中的数据速率可达几Mbps的水平

数据按位传输,高位在前,低位在后(MSB first).

接口

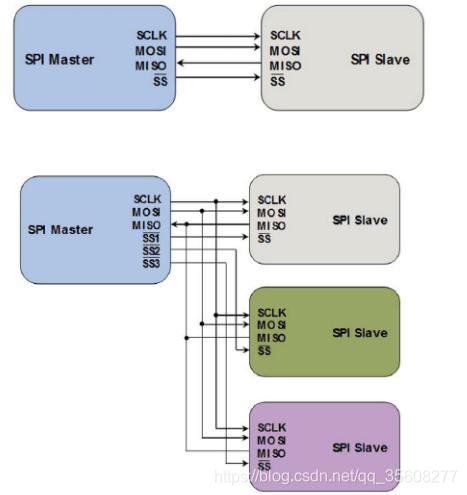

以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

- SDO – 主设备数据输出,从设备数据输入 对应MOSI master output slave input

- SDI – 主设备数据输入,从设备数据输出 对应MISO master input slave output

- SCLK – 时钟信号,由主设备产生

- CS – 从设备使能信号,由主设备控制

SDI/SDO/SCLK: 由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。数据是一位一位的传输的,这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。

当没有时钟跳变时,从设备不采集或传送数据,也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。

SPI接口不需要进行寻址操作,且为全双工通信,因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。

特点

- 主-从模式:两个SPI设备间必须由主机(master)控制从机(slave)。一个主机设备通过提供SCLK信号、选择SS信号(低电平有效)来控制多个从机设备。因此从机设备是无法主动向主机设备发送数据的,因为SPI是一种“时钟驱动”的协议,没有SCLK时无法正常工作。

- 同步传输:主机设备在要交换数据时输出时钟信号,相位CLK_PH和极性CLK_POL的不同配置组成了通常所说的4种SPI模式(具体见第28篇)。只要主机和从机选择同样的配置,即可完成同步传输。

- 数据交换:这里放出28篇中一种模式下的时序图,可以看到每个时钟周期内,MOSI和MISO两根信号上都有数据,即SPI设备会同时“发送”和“接收”1 bit数据,完成数据交换。

数据传输

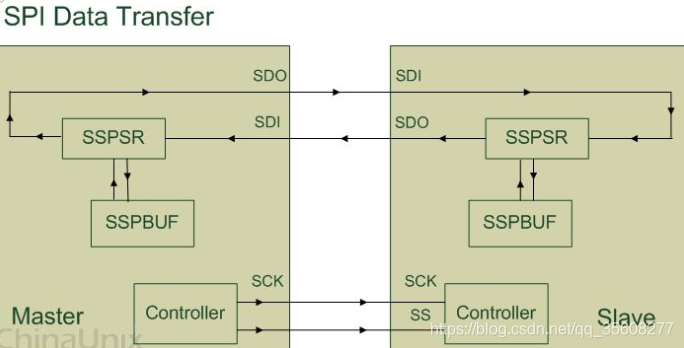

SSPBUF, Synchronous Serial Port Buffer, 泛指 SPI 设备里面的内部缓冲区, 一般在物理上是以 FIFO 的形式, 保存传输过程中的临时数据;

SSPSR, Synchronous Serial Port Register, 泛指 SPI 设备里面的移位寄存器(Shift Regitser), 它的作用是根据设置好的数据位宽(bit-width) 把数据移入或者移出 SSPBUF;

在每个时钟周期内, Master 与 Slave 之间交换的数据其实都是 SPI内部移位寄存器从SSPBUF 里面拷贝的. 我们可以通过往 SSPBUF 对应的寄存器 (Tx-Data / Rx-Data register) 里读写数据, 间接地操控 SPI 设备内部的 SSPBUF.

主机设备在访问从机设备前,必须将SS信号拉低,使能从机设备;当主机要结束本次通信时,再把SS信号拉高即可。

程序中我们都是通过寄存器操纵Tx/Rx FIFO,数据串行化工作由SPI硬件完成(分为手动和自动两种设置)。由于SPI协议“时钟驱动”和“数据交换”的特点,当主机向TxFIFO写数据,进行数据传输时,同时也会把接收到的数据存储到RxFIFO中。下一次传输之前我们应该将RxFIFO中的全部数据都读取出来。

SPI的读、写是同时进行的。如果我们只希望进行写操作,则忽略接收到的字节即可;如果要读取从机中的数据,由于从机无法主动发送数据,因此需要主机向从机发送空字节,来引导从机的传输。

优缺点

-

优点

最大优点是速度快(是UART的几十倍),这也是EEPROM、Flash等芯片采用SPI接口的原因。比如我们将比较大的FPGA bin文件烧写到Flash中,用的便是SPI协议。其支持连续传输模式,无需不断检测帧的起始与结束,同步传输的效率比异步传输也要高。 -

缺点

主要是抗干扰能力比RS422/485要差,不适合远距离传输。另外没有与IIC协议类似的应答机制,以告诉用户是否收到了数据。编程实现上比UART要困难一些,因为我们平时使用的EEPROM、Flash等都提供了现成的命令格式,按照时序图设计即可。当我们自定义主机和从机间的通信时,还要根据设计目的定义一些命令。

eg

环形回路,移位寄存器

在发送数据之前, 我们应该先往 Master 的 Tx-Data 寄存器写入将要发送出去的数据,

这些数据会被 Master-SSPSR 移位寄存器根据 Bus-Width 自动移入 Master-SSPBUF 里,

然后这些数据又会被 Master-SSPSR 根据 Channel-Width 从 Master-SSPBUF 中移出, 通过 Master-SDO 管脚传给 Slave-SDI 管脚,

Slave-SSPSR 则把从 Slave-SDI 接收到的数据移入 Slave-SSPBUF 里.

与此同时, Slave-SSPBUF 里面的数据根据每次接收数据的大小(Channel-Width), 通过 Slave-SDO 发往 Master-SDI,

Master-SSPSR 再把从 Master-SDI 接收的数据移入 Master-SSPBUF.

在单次数据传输完成之后, 用户程序可以通过从 Master 设备的 Rx-Data 寄存器读取 Master 设备数据交换得到的数据.

实例

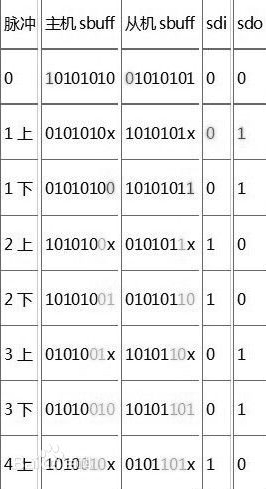

假设下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接收、高位先发送。

主机和从机初始化就绪:并且主机的sbuff=0xaa,从机的sbuff=0x55

那么第一个上升沿来的时候 数据将会是sdo=1,主机寄存器=0101_010x。下降沿到来的时候,sdi上的电平将锁存到寄存器中去,那么这时主机寄存器=0101_0100sdi,从机为1010_1011.

这样在 8个时钟脉冲以后,两个寄存器的内容互相交换一次。这样就完成里一个spi时序。主机的sbuff=0x55 ,从机的sbuff=0xaa

ref

https://blog.csdn.net/weiqifa0/article/details/82765892

工作模式

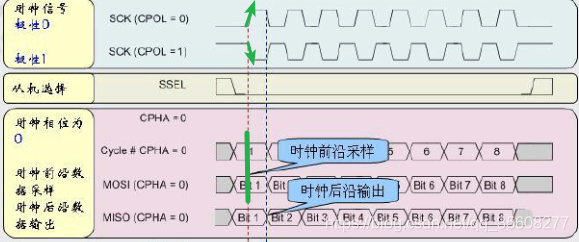

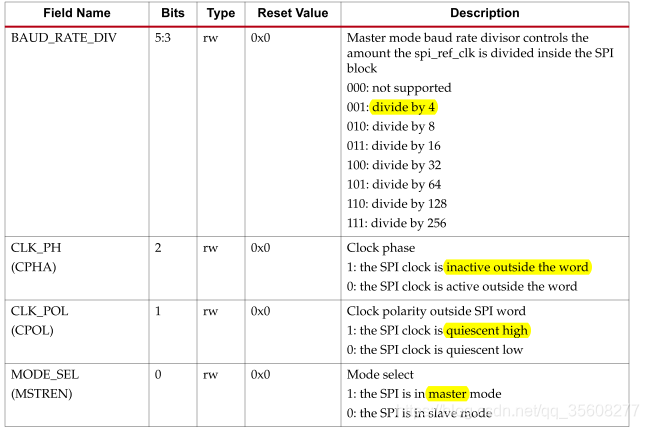

由时钟极和时钟相位决定。

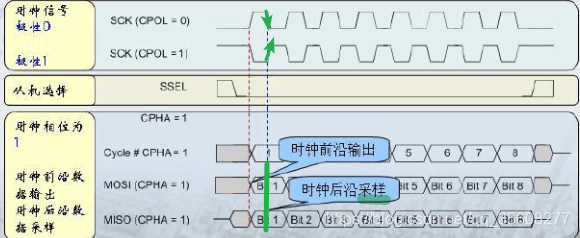

CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,工作电平为高(图中绿色),空闲电平为低电平,CPOL=1时,工作电平为低(图中绿色),空闲电平为高电平。

CPHA是用来决定采样时刻的,采样是在数据中心采样的。

CPHA=0,在每个周期的第一个时钟沿采样,

CPHA=1,在每个周期的第二个时钟沿采样。

简介

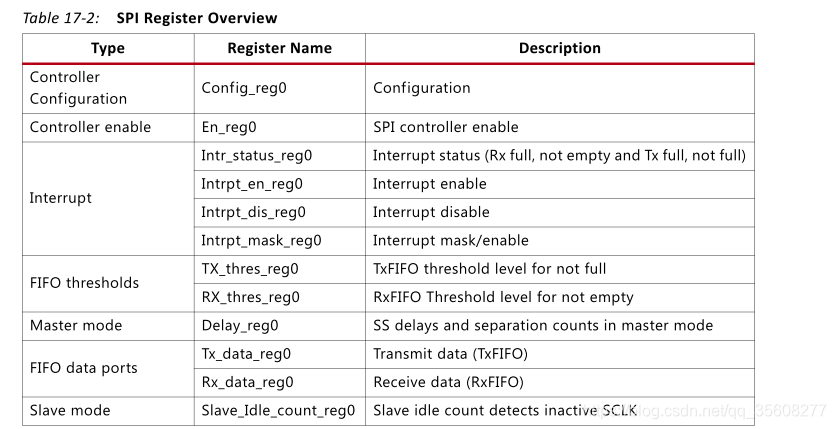

Zynq中的SPI总线控制器能够与各种外设通信,如存储器、温度传感器、压力传感器、模拟转换器、实时时钟、任何支持串行模式的SD卡。SPI控制器可以工作在主机模式、从机模式、舵主模式。Zynq-7000系列包括2个SPI控制器。

-

主机模式:控制器驱动串行时钟(源自PS时钟系统)和从机选择信号。控制器有3个从机选择信号(Slave Select,简称SS),并且可以在外部扩展。控制器通过向32位的读/写数据端口寄存器写入字节,实现读取或写入从机设备。

-

从机模式:控制器接收来自外部设备的串行时钟,并使用SPI_Ref_Clk来同步数据捕获。从机模式包括一个可编程的启动检测机制,当SS信号有效时使能控制器。

-

多主模式:当控制器处于无效状态时,其输出信号是三态的;当控制器使能时,可以检测连接错误。通过复位SPI使能位,控制器输出将立刻转换为三态。

SPI I/O接口和软件之间有读、写FIFO,作为缓存。主机、从机I/O模式下都可使用FIFO。

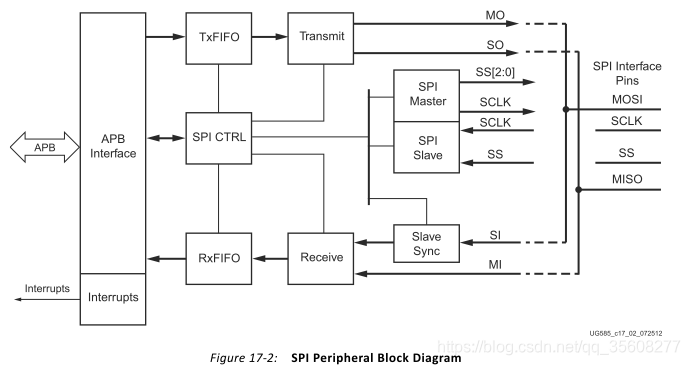

系统框图

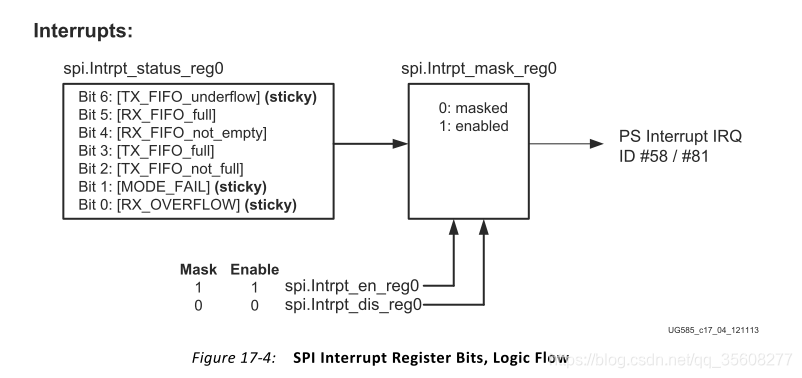

两个独立的SPI接口控制器,每个控制器的I/O信号可以路由(Routing)到MIO管脚或EMIO接口。每个控制器有单独的中断信号(中断ID 58和81)到PS中断控制器,还有单独的复位信号。每个控制器都有自己的一组控制寄存器和状态寄存器。

PS时钟子系统为SPI控制器提供一个参考时钟SPI_Ref_Clk,用于控制器的逻辑功能,再通过波特率发生器产生用于主机模式的SCLK。

功能模块

- APB接口:32位,用于响应寄存器的读、写,处理数据端口和FIFO之间的读写命令和数据。数据端口以字节(即[7:0])为单位。

- SPI主机:此时控制器要驱动SCLK,并输出3个从机选择信号。MOSI信号上的从机选择和传输开始,可以在软件中手动控制,也可以由硬件自动控制。

- SPI从机:此时控制器只使用一个从机选择的输入信号(SS0)。SCLK与控制器的参考时钟(SPI_Ref_Clk)同步。

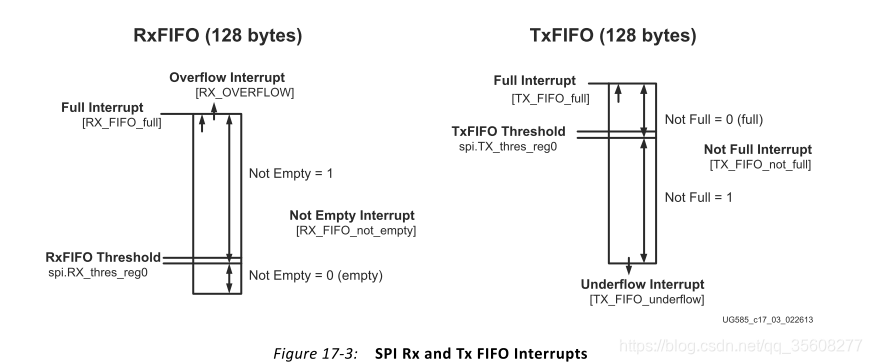

- Tx和Rx FIFO:每个FIFO都是128字节,软件使用寄存器映射后的数据端口寄存器来读、写FIFO。FIFO桥接了两个时钟域:APB接口和控制器的SPI_Ref_Clk。

特性

每个SPI控制器可以独立配置,包括如下特性:

- 四线式总线:MOSI(主机输出-从机输入)、MISO(主机输入-从机输出)、SCLK、SS,主机模式下有3个从机选择信号;

- 全双工工作,支持同时接收和发送;

- 通过APB从接口的32位可编程寄存器;

- 将读/写数据映射到Rx/Tx FIFO,以字节为单位;

- 主机模式下,可选择手动或自动启动数据传输、手动或自动从机选择模式、从机选择信号可以直接与从机设备连接,也可以在外部做扩展(比如3-8译码器)、可编程的SS和MOSI延迟;

- 从机模式下,可编程的启动检测模式;

- 当SPI的I/O信号由MIO引脚引出时,SCLK为50MHz;由EMIO接口引出到PL管脚时,SCLK为25MHz;

- 可编程的时钟相位和极性;

- 可选择中断驱动或轮询状态。

模式

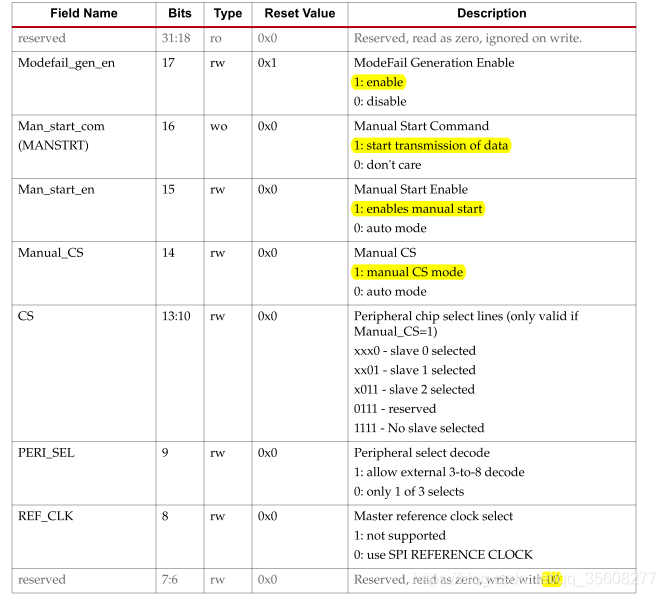

主机模式

SPI I/O接口向从机发送数据,或者接收从机的数据。控制器一次只能选择一个从机设备。如果从机设备超过3个,可以使用3-8译码器,将3个从机选择信号扩展为8路。

1.数据传输

发送

SCLK和MOSI信号由主机控制。软件把要传输的数据写入TxFIFO,由手动或自动的方式启动传输,数据驱动到MOSI(主输出-从输入)管脚上。只要TxFIFO中有数据便会连续传输。

接收

数据从MISO(主输入-从输出)管脚上串行接收数据,一次加载8bit到RxFIFO中,软件读取RxFIFO。每向TxFIFO写n字节数据,也会有n字节数据存储在RxFIFO中,软件必须读取完这些数据后才能开启下一次传输。

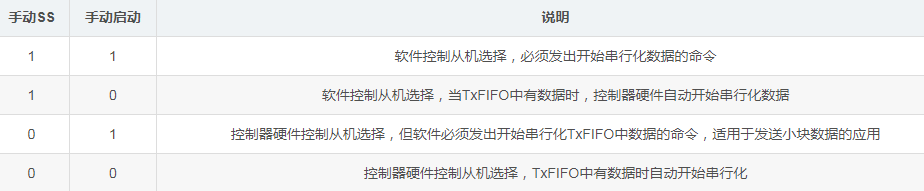

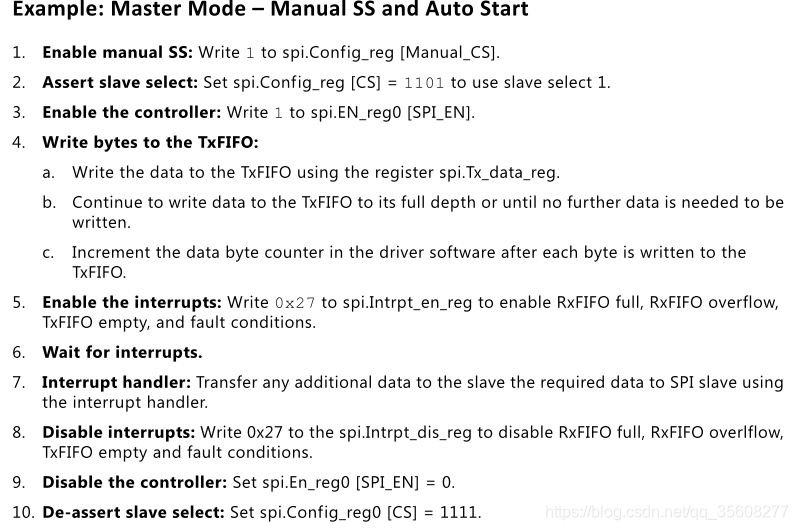

2.自动/手动SS与启动

SPI I/O接口上的数据传输可以通过软件手动启动,也可以由控制器硬件自动启动。从机选择也可以由软件或硬件完成。四种情况总结如下表:

软件中要通过Tx/Rx FIFO的阈值级别来避免FIFO中数据不够或溢出。

当TxFIFO中的字节数小于TxFIFO阈值级别时,标记TxFIFO Not Full状态;

当RxFIFO中的字节数达到128时,标记RxFIFO Full状态。

从机模式

spi.Config_reg0 [MODE_SEL] = 0 and spi.En_reg0 [SPI_EN] = 1

控制器接收来自外部主机的数据,同时输出一个应答。SCLK锁存MOSI(输入)信号上的数据。如果SS(输入)信号为高无效状态,控制器便忽略MOSI上的输入。当SS有效时,在传输期间必须持续保持有效状态。如果传输过程中SS变为无效,控制器会发出中断,以提醒用户。

软件把要发送给主机的数据写入TxFIFO中,然后控制器将其串行化到MISO信号上。当TxFIFO中有数据且SS信号持续低有效时,将保持传输状态。

时钟

SS输入管脚必须由SCLK输入同步驱动。控制器工作在SPI_Ref_Clk时钟域,输入信号也是在SPI_Ref_Clk域中同步并进行分析。

从机模式在SPI_Ref_Clk时钟域中检测一个字(word)的开始,有两种情况:

- 启用控制器时检测:如果在SS无效时使能了控制器,控制器将忽略数据,等待SCLK变为非活跃状态,然后捕获数据。SCLK不活跃时,控制器在SPI_Ref_Clk域中计数,达到设定值(可编程)时,便假定有一个新字(word)。

- SS有效时检测:启用控制器且SS被检测为无效时,当SS转为有效后,下一个SCLK的活跃边沿便被控制器认为是一个字的开始。

一个“开始”必须在至少4个SPI_Ref_Clk周期内保持有效状态。

在外部主机“马上”开始数据传输的时候,才使能从机模式,这样会有概率(很小)发生同步错误的情况。可以采用如下措施避免这个问题:

- 在使能从机模式后,确保至少10个SPI_Ref_Clk周期后外部主机才开始数据传输;

- 确保在使能了外部的主机模式后,再使能从机模式;

- 确保当使能从机时SS输入信号为无效状态。

Tx/Rx FIFO

Tx/Rx FIFO均128bytes深

如果控制器试图将数据送入到一个已满的RxFIFO,该数据将会丢失,同时设置溢出(overflow)标志。写1清除溢出位

如果TxFIFO已满,写操作被忽略,则不要向其写入更多数据。满标志位1直到不再满。

当TxFIFO的级别高于TxFIFO_Not_FULL的阈值级别时,会保持Tx_FIFO_FULL状态。如果我们向已满的TxFIFO写数据,该数据会丢失且不会发出任何指示(比如中断)。

中断

寄存器

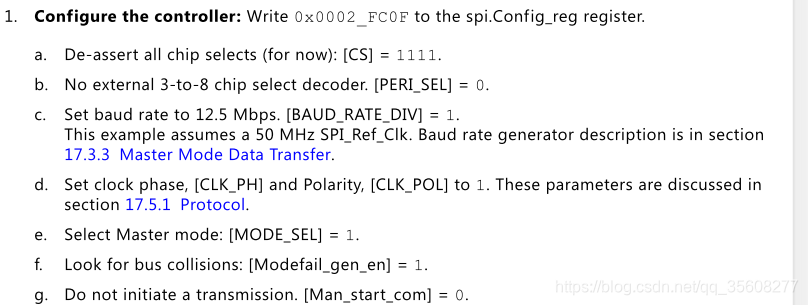

编程流程

复位

时钟

Tx Rx 信号路由

控制器配置

中断配置

开始数据传输

eg

数据传输

SPI协议

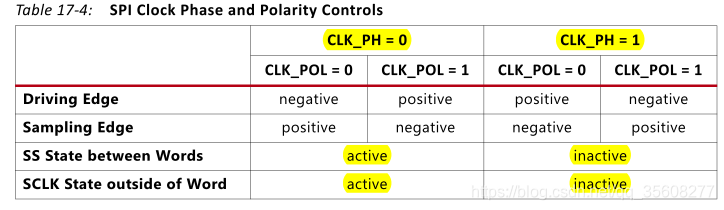

主机模式下,控制器支持几种不同的I/O信号关系,4种时钟相位(CLK_PH)和极性(CLK_POL)的配置组成了通常所说的4种SPI模式。不同的配置参数主要影响SCLK的活跃边沿、SS的选择、SCLK的空闲状态。具体见下表(高电平无效,低电平有效):

上表参数部分看作4×4的矩阵

ref

https://blog.csdn.net/FPGADesigner/article/details/88932544