以下文章来源于小梅哥FPGA ,作者小梅哥

下文所用例程可以下载

链接:https://pan.baidu.com/s/10qP4OnOcc1US_T5gONZ_IQ

提取码:kla0

RS485介绍

RS485是一个定义平衡数字多点系统中的驱动器和接收器的电气特性的标准,该标准由电信行业协会和电子工业联盟定义。使用该标准的数字通信网络能在远距离条件下以及电子噪声大的环境下有效传输信号。RS-485使得廉价本地网络以及多支路通信链路的配置成为可能。

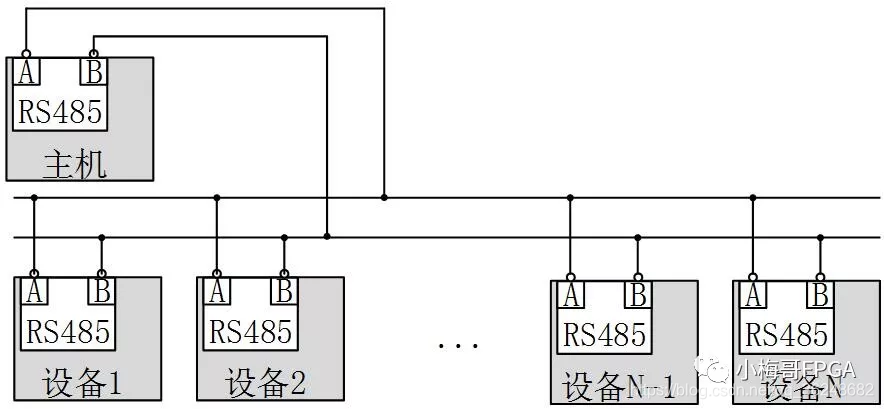

RS485有两线制和四线制两种接线,四线制只能实现点对点的通信方式,现很少采用,现在多采用的是两线制接线方式,这种接线方式为总线式拓扑结构,在同一总线上最多可以挂接32个节点,如图1所示。

图1 RS485组网结构

在RS485通信网络中一般采用的是主从通信方式,即一个主机带多个从机。很多情况下,连接RS-485通信链路时只需要简单地用一对双绞线将各个接口的“A”、“B”端连接起来,忽略信号地的连接。这种连接方法能够在许多场合正常工作,但是在更加恶劣的工作环境中,还是应该保证所有设备都良好的接地,以保证通信的可靠性。

数字电路中,由TTL电子元器件组成电路使用的电平,电平是个电压范围,规定输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

RS-485的电气特性:逻辑“1”以A、B两线间的电压差为+(2~6)V表示;逻辑“0”以两线间的电压差为-(2—6)V表示。接口信号电平比RS-232-C降低了,就不易损坏接口电路的芯片,且该电平与TTL电平兼容,可方便与TTL 电路连接。虽然标准情况下要求压差为2~6V,但是实际上大多数的收发器芯片都将压差限制到了不低于200mV即可,这样能够确保数据不会在网络负载很大的时候因为压差降低而被遗漏。

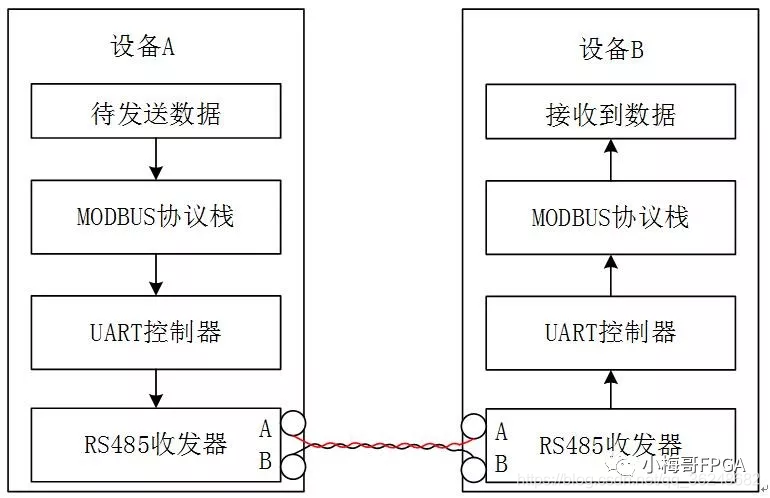

在很多工业设备,尤其是电力系统的仪器仪表中,大多使用RS485接口实现设备和主控站的通信。RS485接口属于电气接口,实现的是通信网络中的物理层。基于RS485物理层接口,使用UART控制器接收和发送按照标准串口协议编码的数据,即可实现设备间最基本的数据收发。然后,再使用常见的上层应用层协议,典型的例如MODBUS协议,完成多个设备的通信管理。该通信层级模型如图2所示:

图2 基于MODBUS的RS485通信数据流图

发送设备发送数据时,数据走向为:

MODBUS协议栈将用户数据打包为一个MODBUS数据帧;

UART驱动以字节为单位将MODBUS数据帧交付给UART控制器;

UART控制器将字节数据完成并串转换,然后通过发送脚送到RS485收发器的驱动器输出(DI)端;

RS485收发器将DI端每一个bit的数据转换为RS485标准的电平,通过双绞线传输到远端。

接收设备接收数据时,数据走向为:

RS485收发器检测到双绞线上的RS485电平的每一个单bit数据,将其转换为普通的TTL电平信号,

并通过接收器输出脚(RO)脚送给UART控制器的接收脚;

UART控制器将接收脚上的每一个单bit信号按照UART协议进行接收解码,得到以字节为单位的实际数据。

MODBUS协议栈将UART接收到的多个字节数据进行解析得到完整的数据帧,并解帧得到实际的数据部分

在实际应用时,MODBUS协议栈一般由CPU通过软件方式实现。虽然使用FPGA,以HDL的方式也能实现一些特定的功能,但是总体来说复杂度高,灵活性差,应用局限性大。如果确实希望在FPGA内部实现MODBUS协议,除了使用HDL编程以外,还可以使用更加灵活的SOPC技术,通过在FPGA内部嵌入NIOS II或其他软核CPU以软件编程的方式实现。

鉴于上述情况,本实验不对如何实现MODBUS协议栈做介绍,仅介绍如何完成基本的数据收发。

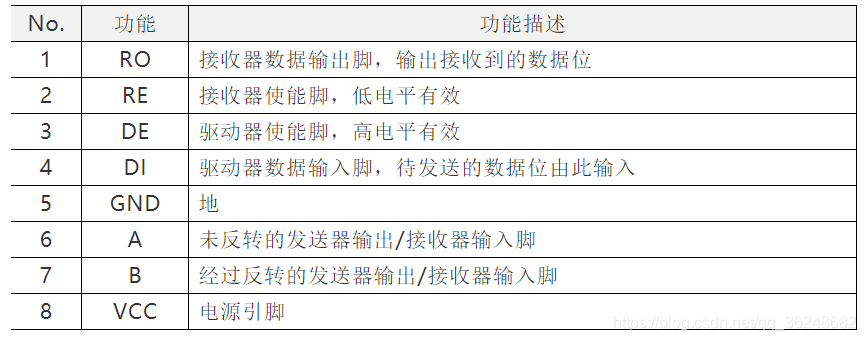

RS485收发电路介绍

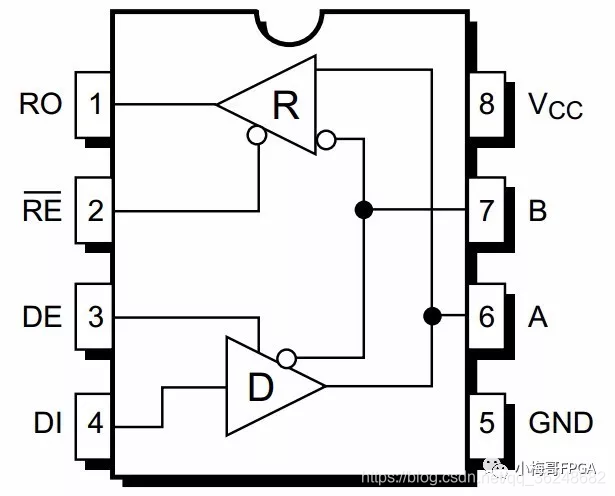

上文提到,要实现基于RS485接口的数据收发,需要有RS485的物理层收发器。能够提供RS485收发器的厂家有很多,常见RS485收发器有MAX485、SP3485(3.3V供电)、ADI公司磁隔离方式的ADM2587以及周立功单片机有限公司开发的RSM485收发模块等。在AC620开发板上,使用的是能够支持3.3V供电的SP3485芯片,该芯片电路简单,能够实现完整的RS485收发器功能。表1为该收发器的功能框图和引脚功能介绍。

表1 SP3485芯片引脚功能介绍

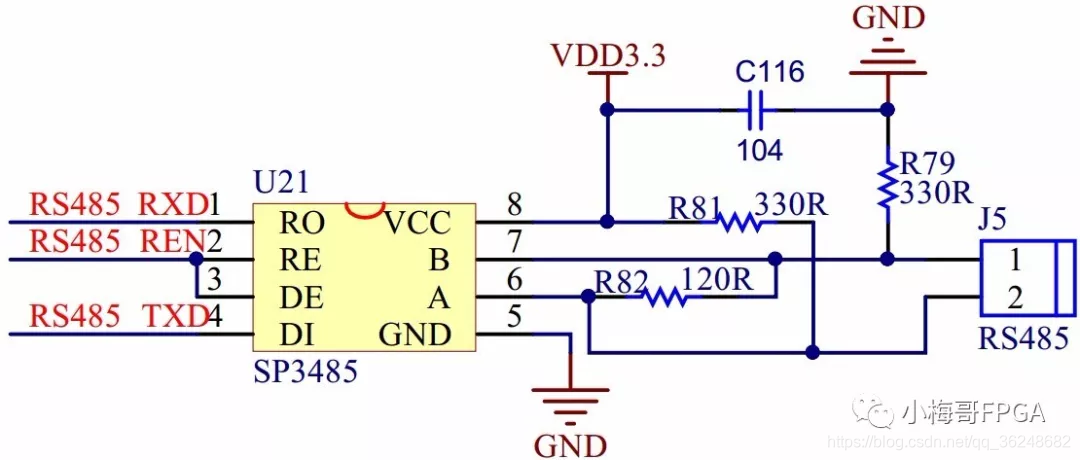

图3为AC620开发板上RS485收发器的电路图

图3 AC620开发板RS485收发器电路图

可以看到,SP3485的RE和DE两个引脚被连接到了一起,然后接到FPGA上,这是因为两者的有效状态本身就是相反的,RE为低电平有效,DE为高电平有效。因此,同一个信号控制这两个引脚,总能保证任意时刻接收和发送器中有且仅有一个被使能。

当RS485_REN信号为低电平时,RE有效,DE无效,因此SP3485芯片中的接收器被使能,而发送驱动器被关闭,芯片处于接收状态;

当RS485_REN为高电平时,RE无效,DE有效,因此SP3485芯片中的接收器被关闭,而发送驱动器被使能,芯片处于发送状态。

FPGA逻辑设计说明

本设计基于小梅哥的《FPGA设计思想与验证方法》视频教程中“11串口发送模块设计与验证”和“12 串口接收模块设计与验证”两个课程对应的随堂工程改编而来。使用时,在“11串口发送模块与验证”随堂工程基础上添加“12 串口接收模块设计与验证”随堂工程中的“uart_byte_rx.v”文件,然后对顶层文件稍加修改实现。

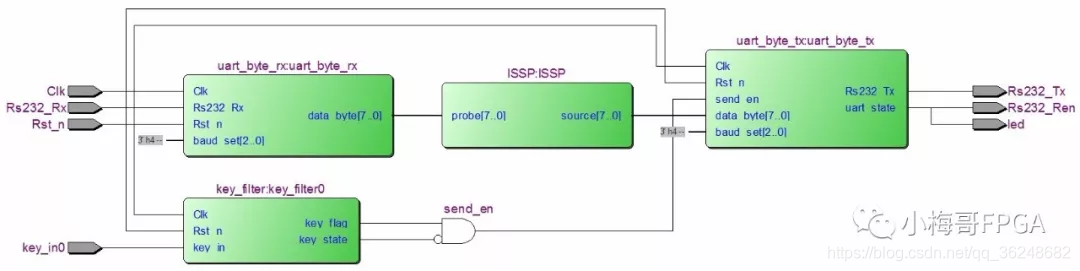

修改后的工程框架如图4所示:

图4 RS485收发工程功能框图

可以看到,对于发送数据,还是和“11串口发送模块与验证”视频中介绍的一样,通过按下按键产生发送使能信号,将data_byte端口上的数据通过Rs232_Tx发出。而data_byte端口又连接到了In-System Sources and Probes工具的信号源端口(source)上,这样,通过在In-SystemSources and Probes工具中给source设置不同的值,就能修改需要通过uart_byte_tx发送的具体数值了。

同时,为了保证发送时SP3485芯片中的发送驱动器是使能的,使用了uart_byte_tx模块中的uart_state端口驱动SP3485的RE和DE信号。当uart_byte_tx模块处于数据发送过程中时,uart_state信号为高电平,此时DE使能,RE无效,SP3485芯片的发送驱动器被使能,DI上的信号就能够通过发送驱动器变为RS485电平,经由A、B两个端口输出。实际上,小梅哥在早期讲解这个uart_byte_tx模块的设计时刻意加上这个uart_state端口,就是为了方便该模块用于RS485接口通信的。

当uart_byte_tx模块数据发送完成,处于空闲状态时,uart_state保持低电平,此时SP3485芯片中的接收器被使能,发送驱动器被关闭。所以,只要RS485总线上有任何电平变化,都能够进入SP3485的接收器,并转换为TTL电平,由SP3485的RO脚传递给FPGA,再接入uart_byte_rx模块的Rs232_Rx信号上,完成串行数据的接收。接收到的数据连接到了In-System Sources and Probes模块的探针端口(Probes)上,方便在In-SystemSources and Probes工具中实时观察接收到的数据。

RS485实验验证

1、验证时,有能力的请直接按照上文描述的内容,通过两个课程的随堂源码搭建对应的应用工程。不熟悉的也可以直接使用我们提供的工程源码,在AC620的“设计实例 --> AC620_Verilog_Example”里面能够找到,工程名为AC620_RS485_RX_TX.rar。

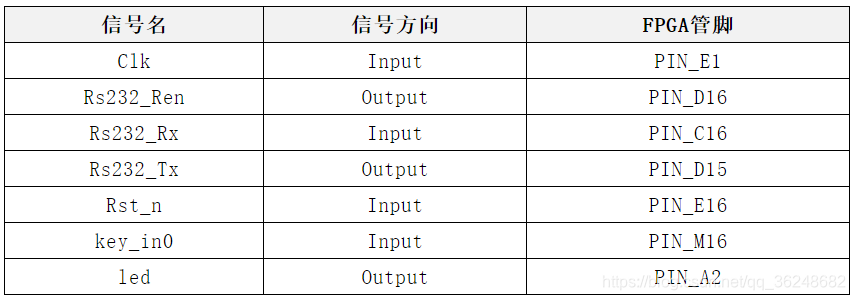

2、按照下述引脚分配表完成工程的引脚分配

3、使用一个USB转RS485转换器,例如图5所示,USB一端连接电脑,RS485一端连接开发板上的RS485接口。该转换器一般使用的是CH340实现的USB转串口,因此插到电脑上会识别出一个COM端口,在电脑上使用时,就像使用串口功能一样。

图5 USB转RS485模块

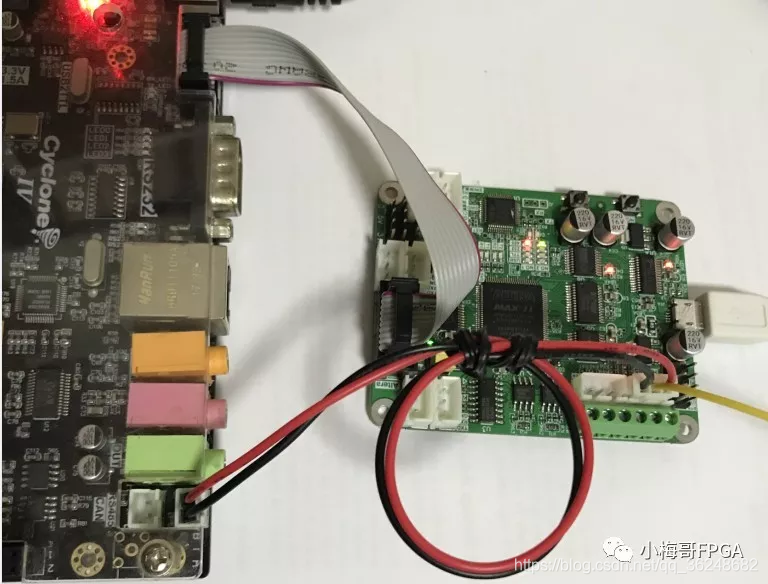

笔者手里没有这个转换模块,但是有我们自己研发的多合一调试器模块,该调试器能够支持USB转TTL、USB转RS232、USB转RS485功能,同时还带有USB Blaster和ST_LinkV2功能,使用很方便,因此笔者就使用该调试器的USB转RS485功能完成本实验的调试。

将该调试器的RS485接口连接到AC620开发板的RS485接口上,如图6所示。在电脑上选择对应的COM端口就可以实现PC和AC620开发板通过RS485接口通信了。

图6 使用多合一调试器实现RS485调试

4、打开串口调试软件(推荐使用“串口猎人”),选择PC上该USB转RS485模块对应的端口号,设置波特率为115200。

5、全编译工程,下载sof文件到开发板中。

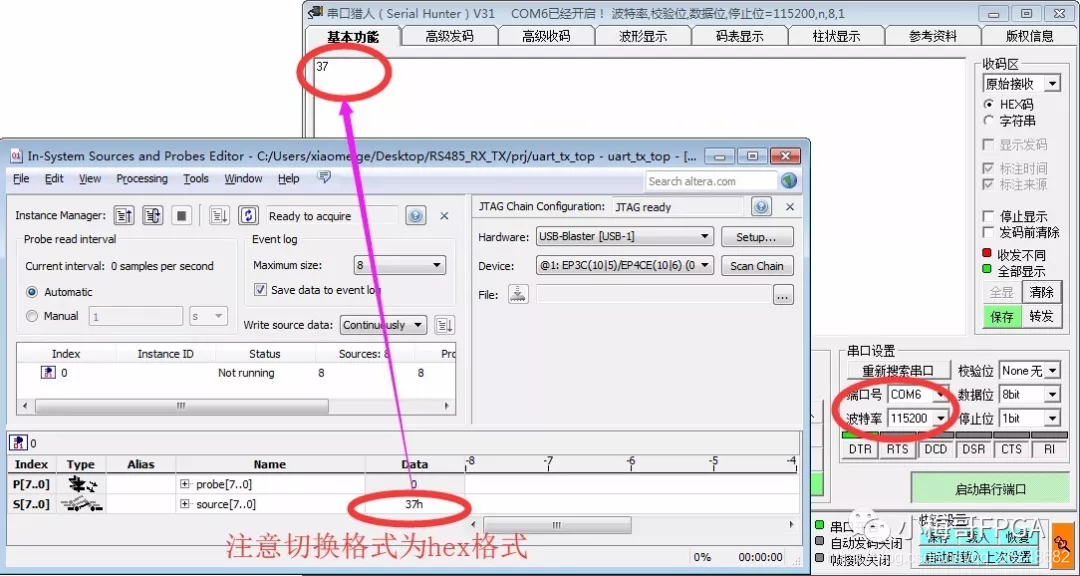

6、打开In-System Sources and Probes工具,将source和probe的显示格式都切换为hex格式,然后在source的data栏中输入希望发送的数据,然后按下开发板上的S0按键,可以看到,串口猎人上对应显示出了接收到的数据,如图7所示。

图7 FPGA发送数据

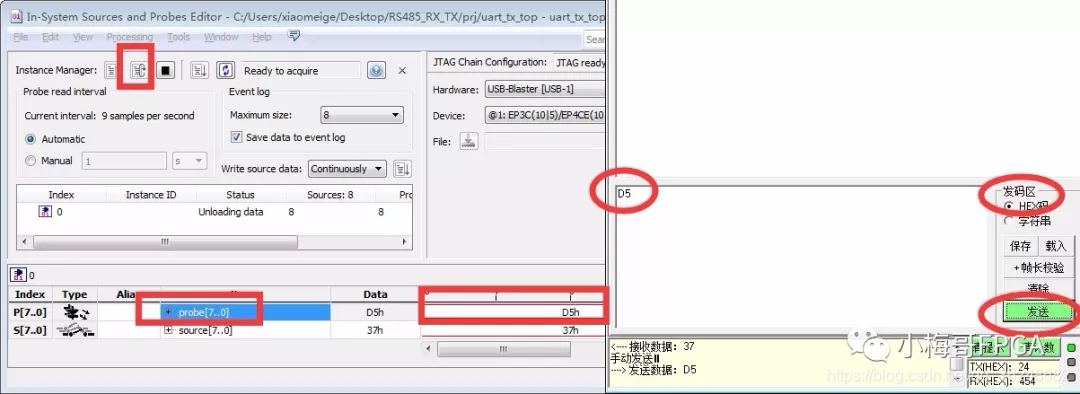

7、选中In-System Sources and Probes中的probe,然后点击持续读取按钮,在串口猎人中输入一个字节的数据并点击发送,则可以看到In-System Sources and Probes中的probe数据立即更新为了接收到的新数据,如图8所示。

图8 FPGA接收RS485数据

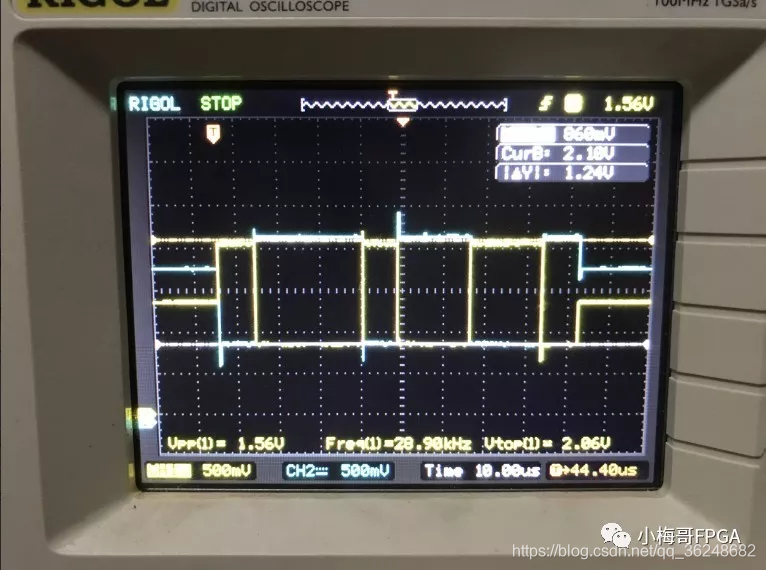

8、使用示波器测量RS485总线上的A和B端,如图9所示。其中蓝色波形为A,黄色波形为B。可以看到,第一位波形,A-B的差值为-1.24V左右,代表0,对应了UART串口协议的起始位,第二位,A-B的差值为1.24V,代表1,而实际发送的数据37h的二进制值为00110111b,bit0的值为1,刚好与波形对应。

图9 SP3485传输数据波形图

总结

自此,基于FPGA的RS485基本通信就实现了,用户可以基于此工程,编写上层的应用逻辑,以实现更加复杂多样化的定制功能。当然,笔者更推荐使用NIOS II软核CPU实现这些功能。